Fターム[5H740BB04]の内容

電力変換一般 (12,896) | 主回路スイッチング素子の接続と負荷態様 (2,347) | 直並列接続 (107)

Fターム[5H740BB04]に分類される特許

1 - 20 / 107

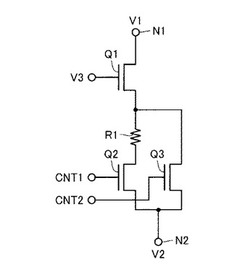

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

ゲート駆動回路

【課題】ワイドギャップ半導体のターンオフの速度を高速化できるゲート駆動回路。

【解決手段】負極が接地された正電源E1と、正極が接地された負電源E2と、正電源の正極と負電源の負極との間に設けられ、制御信号を生成する制御回路11と、正電源の正極と負電源の負極との間に設けられたトランジスタQ1とトランジスタQ2との直列回路と、ドレイン端子、接地されたソース端子及びQ1とQ2との接続点に接続されたゲート端子を備えたワイドバンドギャップ半導体からなるスイッチング素子GaNFETと、制御信号のオフ時にQ1を所定時間だけオンさせQ1を介して負電源の電圧をスイッチング素子のゲート端子に印加するターンオフ制御回路13と、スイッチング素子のゲート端子と接地との間に設けられ、制御信号のオフ時にそのゲート端子とソース端子を短絡させるトランジスタQ3とトランジスタQ4との直列回路を備える。

(もっと読む)

出力回路

【課題】貫通電流の発生を防止することのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力用NMOSトランジスタN100のドレイン端子に入力電圧VDINが印加され、ソース端子OUTにLC回路およびダイオードDが接続される。この出力回路は、NMOSトランジスタN1およびN2が、出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に直列に接続され、NMOSトランジスタN3が、NMOSトランジスタN1とNMOSトランジスタN2の接続点と接地電位端子GNDとの間に接続され、制御回路1が、出力用NMOSトランジスタN100が非導通のときに出力用NMOSトランジスタN100のソース端子OUTとゲート端子との間に短絡経路が形成されるようNMOSトランジスタN1〜N3の導通を制御する。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

電力変換装置

【課題】電力変換装置を構成するFETの発熱を低下させ、最大出力電力を高めた改良された電力変換装置を得る。

【解決手段】FET1a、FET1bとFET1a、FET1bに逆並列接続された還流ダイオードD1a、D1bとにより半導体スイッチS1a、S1bを構成し、スイッチング動作を行う2個1組の半導体スイッチS1a、S1bと、平滑コンデンサC1とを有し、半導体スイッチS1a、S1bのFET1a、FET1bの相補的スイッチング動作により電力変換を行う電力変換装置10において、半導体スイッチS1a、S1bに流れる電流の向きを検出する電流センサCS1と、半導体スイッチS1a、S1bに流れる電流の向きが負であるときに、半導体スイッチS1a、S1bのPWMゲート信号のオン信号を間引くゲート生成部11を備えた。

(もっと読む)

信号伝達装置及びこれを用いたモータ駆動装置

【課題】ドライバチップの異常検出期間が短過ぎると、異常パルス信号のパルス生成が停止された後、異常判定期間の経過前に異常パルス信号のパルス生成が再開されてしまい、コントローラチップでドライバチップの異常を認識することができなくなるおそれがあり、2つの回路を絶縁しつつ一方の異常を確実に他方に伝達することのできる信号伝達装置、及びこれを用いたモータ駆動装置を提供する。

【解決手段】信号伝達装置100は、第1回路110と第2回路120との間を絶縁しながら信号伝達を行うものであり、第1回路110は、第2回路120から伝達される異常パルス信号Sbを監視して第2回路120の異常有無を判定し、第2回路120は、第2回路120で異常が検出されてから少なくとも第1回路110で第2回路120の異常有無が判定されるまで異常パルス信号Sbを異常状態に保持する。

(もっと読む)

電力変換装置

【課題】複数の電力変換回路を有し、これらの電力変換回路に属する半導体モジュールを積層した電力変換装置において、電力変換回路間のサージ電圧による干渉を低減する。

【解決手段】複数の電力変換回路の正極端子を接続する正極接続プレート66にスリット100,102を設ける。一方、正極接続プレート66が配置される固定台68上にかしめ突起105を設ける。かしめ突起105を、正極接続プレートのスリット100,102に貫通させ、かしめ突起105の先端をつぶして正極接続プレート66をかしめ、固定台68に固定する。正極接続プレートを固定するためのボルト等を用いていないため、負極接続プレート70の面積を広くすることができ、サージ電圧による干渉を低減できる。

(もっと読む)

駆動回路

【課題】複数のスイッチ素子を備える装置を小型化すること。

【解決手段】駆動回路1は、キャパシタC21と、充電部を構成する抵抗R21およびダイオードD21と、を備える。キャパシタC21は、スイッチ素子Q11のゲートと、スイッチ素子Q21のゲートと、の間に設けられ、制御部22の端子Y3には、スイッチ素子Q11のゲートが接続されるとともに、キャパシタC21を介してスイッチ素子Q21のゲートが接続される。抵抗R21およびダイオードD21で構成される充電部は、スイッチ素子Q21のゲートとソースとの間に設けられる。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#の駆動異常の有無を適切に判断することのできるスイッチング素子の駆動回路を提供すること。

【解決手段】スイッチング素子S*#のゲートの充電経路を流通する電流を一定値に制御する定電流制御を行う。そして、定電流制御の開始が指示されてから充電経路における電流の流通が開始されるまでの時間が規定時間を上回ると判断された場合、スイッチング素子S*#の駆動異常が生じている旨判断する。また、定電流制御によって充電経路を電流が流通する時間が下限時間未満になると判断されたり、上記流通する時間が上限時間を上回ると判断されたりした場合、スイッチング素子S*#の駆動異常が生じている旨判断する。

(もっと読む)

半導体スイッチ

【課題】 主素子の逆並列ダイオードの逆回復特性を改善することができ、構成素子の耐電圧化を図ることができる半導体スイッチを提供する。

【解決手段】 半導体スイッチ7は、スイッチング素子1及び逆並列ダイオード2を有した主素子3と、逆電圧印加回路6と、を備えている。逆電圧印加回路6は、補助電源12と、高速還流ダイオード4と、補助素子5と、コンデンサ13と、を有している。高速還流ダイオード4は、多直列に接続された複数のダイオード15で形成されている。

(もっと読む)

スイッチング素子の駆動回路

【課題】充電用スイッチング素子24lをオン操作することで、直流電圧源22lの端子電圧(制限用電圧VL)をスイッチング素子S*#のゲートに印加している期間において、ノイズ等によってコレクタ等からゲートへの電流の流れ込みが生じうること。

【解決手段】ゲート電圧Vgeは、端子T8を介して駆動制御部70によってモニタされる。駆動制御部70では、充電用スイッチング素子24lのオン操作期間においてゲート電圧Vgeが制限用電圧VLを上回る場合、シンクスイッチング素子60をオン操作して、ゲートの過剰な電荷を放電させる処理を行う。

(もっと読む)

ドライバ回路

【課題】 絶縁電源を別に設けることなくハイサイド側の回路に負のゲート電圧を供給することが可能なゲートドライバ回路を実現する。

【解決手段】

第1トランジスタ21と第2トランジスタが直列に接続されたハーフブリッジ回路において、ハイサイド側の第1トランジスタ21に負のゲート電圧を第1の制御回路11を介して供給するためのコンデンサ13、及び、ローサイド側の第2トランジスタ22に負のゲート電圧を第2の制御回路12を介して供給するための制御回路電源14を備え、コンデンサ13の一端をスイッチ素子30を介して制御回路電源14の−端子側の負電圧VEEと接続し、他端を出力端子4の電圧と接続するように構成したドライバ回路1であって、スイッチ素子30は、第2トランジスタ22がオン状態となるタイミングでオンされるように制御される。

(もっと読む)

情報処理装置、これを用いたモータ駆動装置、及び、情報処理方法

【課題】 上下アームのスイッチング素子を駆動するとともに、上下アームの異常を検出して異常信号を出力するゲート駆動回路を備える情報処理装置において、異常信号の通知機能が正常であるか否かを判定する。

【解決手段】 情報処理装置(ECU)において、ブートストラップ式のゲート駆動回路は、ゲート駆動の開始前に、通常駆動時ならば先に下アーム駆動信号を出力すべきところ先に上アーム駆動信号D1を出力し(S10)、ダミー異常信号Edを意図的に発生させる(S20)。ここで異常信号通知機能が正常であれば、ダミー異常信号Edは、異常信号出力部から出力され、異常信号線を経由して伝達され、異常信号受信部に受信される。そこで、異常信号受信部がダミー異常信号Edを受信したか否かを確認することで、異常信号通知機能が正常であるか否かを判定する(S30)ことができる。

(もっと読む)

電力変換回路の駆動装置

【課題】フェール信号を出力するフェール用フォトカプラPCfの2次側を直列接続する場合、その配線長が長くなることから、フェール信号のノイズに対する耐性が低下するおそれがあること。

【解決手段】インバータIV1、コンバータCVおよびインバータIV2を構成する上側アームのスイッチング素子と下側アームのスイッチング素子とは、基板30に対して2列に配置され、その制御端子(ケルビンエミッタ電極KE、センス端子ST、ゲートG)が基板30に差し込まれている。これら2列の間には、フェール用フォトカプラPCfが配置されている。インバータIV1に対応するフェール用フォトカプラPCfは、隣接するもの同士で直列接続され、各列の端部が接続されることでU字型の配線構造を有し、その端部がマイコン20に接続されている。

(もっと読む)

インバータ駆動装置

【課題】インバータのゲート駆動にソフトターンオフ(Soft Turn Off)を設けてIGBTを安定して保護できるようにしたインバータ駆動装置を提供する。

【解決手段】本発明のインバータ駆動装置は、IGBTのターンオンまたはターンオフを制御し、IGBTで短絡または過電流が検出されればIGBTを強制的にターンオフさせるゲート駆動部と、前記ゲート駆動部から出力されるIGBTのターンオンまたはターンオフ制御電流を増幅させる電流バッファと、前記ゲート駆動部から出力されるIGBTの強制ターンオフ制御電流を遅延させてIGBTのソフトターンオフ時間を長く維持させるフィルタと、を含んで構成される。

(もっと読む)

ドライブ回路

【課題】1個のデッドタイム生成回路を用いて、直列に接続されている2つのスイッチング素子を駆動する2系統の信号のそれぞれ対してデッドタイムを設けることができ、IC化した場合に外付けコンデンサを1個にすることができるドライブ回路を提供する。

【解決手段】

コンデンサ13aを用いて信号Va0をデッドタイムよりも短い時間遅延させる遅延回路2aと、コンデンサ13bを用いて信号Vb0をデッドタイムよりも短い時間遅延させる遅延回路2bと、コンデンサ23を用い、信号Va0および信号Vb0の立ち上がりのタイミングからデットタイム分遅延させたタイミングで立ち上がる周期T/2のデッドタイム生成用信号V6を生成するデッドタイム生成回路3と、デッドタイム生成用信号V6に基づいてデッドタイムが設けられた信号Va7および信号Vb7とを生成するAND回路17a、17bとを設ける。

(もっと読む)

電力変換装置

【課題】並列接続された電力用スイッチング素子の特性の差異により生ずるターンオン/オフ動作時間の差に起因する当該並列接続された電力半導体素子間の遮断電流の偏りを緩和し、信頼性を向上させ、電流定格、及び耐圧の低い素子の適用を可能とし、低コスト化を実現する。

【解決手段】図は直流から交流に変換する電力変換装置1相分の回路を示し、電力用スイッチング素子を2並列で用いている回路構成例であり、電力半導体素子6a、6bの特性に差異があると各々の通電電流はILa≠ILbとなるが、6a、6bの特性に適したゲート電流IGa、IGbを流すゲート駆動回路構成を提供とすることで、ターンオン/オフに要する時間に差を緩和しILa≒ILbとし、並列接続された一方の電力半導体素子への主回路電流の集中を抑制することが可能となる。図では2並列の例であるが、並列接続数によらず本解決手段は有効である。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

パワー半導体モジュール及びそれを用いた電力変換装置

【課題】従来は、電力変換回路毎に半導体モジュールが必要となっていたため、種類が増加するという問題があった。また、需要の少ない回路方式では、その回路方式に合ったモジュールをカスタマイズ化することは型費や歩留まりなどの問題でコストアップ要因となるため、必然的に既存の半導体モジュールを組み合わせて回路を構成する必要があった。

【解決手段】半導体モジュールの構成を、ダイオードを逆並列接続したIGBT2個と双方向スイッチ2個、又は双方向スイッチ4個を1個のモジュールに内蔵させ、5つの外部端子を備える構成にした。

(もっと読む)

電力用半導体装置

【課題】ブートストラップコンデンサを十分に充電することができ、かつ回路を簡略化及び小型化することができる電力用半導体装置を得る。

【解決手段】ブートストラップコンデンサCbsの一端が、トーテムポール接続されたハイサイドスイッチング素子M1とローサイドスイッチング素子M2の接続点に接続され、他端がハイサイド駆動回路10aの電源端子に接続されている。ブートストラップダイオードDbsは、ローサイド駆動電源LVからの電流をブートストラップコンデンサCbsの他端に供給する。ハイサイド駆動回路10aがハイサイドスイッチング素子M1をONにし、ローサイド駆動回路10bがローサイドスイッチング素子M2をOFFにする場合に、ブートストラップ補償回路12は、ブートストラップコンデンサCbsの他端に、高圧側電位を基準電位とするフローティング電源FVからの電流を供給する。

(もっと読む)

1 - 20 / 107

[ Back to top ]