Fターム[5H740JB02]の内容

Fターム[5H740JB02]の下位に属するFターム

主電流に比例させるもの (15)

Fターム[5H740JB02]に分類される特許

1 - 20 / 27

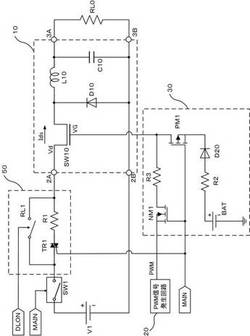

制御回路及び電子機器

【課題】ノーマリーオフ化したGaN−HEMTを電源回路に用いた場合、長期間電源をオフしている間にノーマリーオンに戻るのを防止する制御回路を提供する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

電源装置の駆動回路及び電源装置

【課題】遷移期間においてハイサイドトランジスタQ1がオンしないようにする。

【解決手段】高電位電源ラインと低電位電源ラインとの間に直列に接続されたハイサイドトランジスタとロウサイドトランジスタと,両トランジスタの接続ノードと出力端子との間に設けられたインダクタとを有する電源装置の前記両トランジスタを駆動する駆動回路であって,前記ハイサイドトランジスタのゲートを駆動する第1のゲートドライバと,前記ロウサイドトランジスタのゲートを駆動する第2のゲートドライバとを有し,前記ハイサイドトランジスタがオンでロウサイドトランジスタがオフの第1の状態から,前記ハイサイドトランジスタがオフでロウサイドトランジスタがオンの第2の状態に遷移する遷移期間で,前記第1のゲートドライバは前記ハイサイドトランジスタのゲートを前記低電位電源ラインの電位より低い第1の電圧に駆動する電源装置の駆動回路。

(もっと読む)

電源回路

【課題】主スイッチング素子の面積を大きくすることなく、ゲートの容量に蓄積された電荷を引き抜く引き抜き期間を短くすることができる電源回路を提供する。

【解決手段】Nチャネル型の主スイッチング素子10と、主スイッチング素子10を制御する駆動回路30と、主スイッチング素子10の第2電極端子に接続される負バイアス回路20とを備える。そして、負バイアス回路20を、接地された第1抵抗21と、当該第1抵抗21と第2電極端子との間に配置されて第2電極端子との接続点の電位を第1抵抗21との接続点の電位より低くする電位降下手段22、23とを有するものとする。また、駆動回路30を第1抵抗21と電位降下手段22、23との接続点に接続する。そして、主スイッチング素子10がオフされたとき、ゲートの容量に蓄積された電荷を駆動回路30および第1抵抗21と電位降下手段22、23との接続点を介して引き抜くようにする。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】信号遅延が小さく高速化可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、差動電流生成回路と電流減算回路とを備えたレベルシフト回路が提供される。前記差動電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、入力される制御信号に応じて、規定値または前記規定値よりも大きい電流値に変化する電流と前記規定値よりも大きい電流値または前記規定値に変化する電流とを一対の差動電流として生成する。前記電流減算回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記一対の差動電流を受けて、前記一対の差動電流の差に等しい電流を生成する。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】低消費電力で高速動作可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、電流生成回路と、電流スイッチ回路と、保護回路と、を備えたレベルシフト回路が提供される。前記電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、第1の電流を生成して第1の出力線に出力する。前記電流スイッチ回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記電流生成回路よりも大きい電流供給能力で前記第1の電流を受け、入力信号に応じて前記第1の電流を流しまたは前記第1の電流を遮断する。前記保護回路は、前記電流生成回路と前記電流スイッチ回路との間において前記第1の出力線に接続され、前記第1の出力線の電位を前記第1の低電位端子の電位以上で前記第1の高電位端子の電位以下に制限して前記電流生成回路を過電圧から保護する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

アーク加工用電源装置

【課題】 電源装置のインバータ回路を駆動するスイッチング素子駆動回路の逆バイアス電圧が低くなると、ターン・オフ損失が増加しスイッチング素子の劣化に繋がる。

【解決手段】 直流変換回路と、直流電圧を高周波交流電圧に変換するフルブリッジのインバータ回路と、インバータ回路を制御すると共に変圧器の入力電流が基準電流以上になると所定時間インバータ回路を停止する出力制御回路と、出力制御信号に応じてスイッチング素子を駆動すると共に逆バイアスコンデンサに電流を供給するスイッチング素子駆動回路とを備え、インバータ回路が停止しているとき、第1のスイッチング素子及び第4のスイッチング素子が0から1/2周期の間で重ならないようにオンし、第2のスイッチング素及び第3のスイッチング素子が1/2から1周期の間で重ならないようにオンするスイッチング制御回路、を備えたことを特徴とするアーク加工用電源装置である。

(もっと読む)

駆動回路及びこれを備える半導体装置

【課題】簡易な構成でスイッチング素子の負バイアス駆動を行う駆動回路及び当該駆動回路を備えた半導体装置の提供を目的とする。

【解決手段】本発明の駆動回路は、ICチップに搭載され、半導体スイッチング素子4aを駆動する駆動回路であって、前記ICチップ外部の単一電源から供給される第1の電圧V1を受け、第1の電圧V1から第2の電圧V2を生成して、これを半導体スイッチング素子4aの基準端子に印加する電源回路8と、前記ICチップ外部からの入力信号に応じて、半導体スイッチング素子4aの制御端子に第1の電圧V1を印加/非印加することにより半導体スイッチング素子4aを駆動する駆動部とを備える。

(もっと読む)

半導体電力変換装置のゲート駆動回路

【課題】ターンオフサイリスタのゲート・カソード電圧が負になった場合でもターンオン電流が増大するのを防止することのできる半導体電力変換装置のゲート駆動回路を提供する。

【解決手段】エネルギー蓄積手段12の正極から第1のスイッチ10を介してターンオフサイリスタ14のゲートにリアクトル13を、ターンオフサイリスタのカソードとエネルギー蓄積手段の負極間に第2のスイッチ8を設ける。環流ループを得るためにフライホイールダイオード7及び9を設ける。

スイッチ10、8をオンオフさせるためのターンオン制御手段5を設ける。ターンオン制御手段5は、スイッチ8がオンで且つターンオフサイリスタ14のゲート・カソード電圧が負になったとき、スイッチ8、10をオフさせるように制御する。

(もっと読む)

電力変換装置

【課題】 ノイズによる誤動作や短絡を防止して安全に駆動できるゲート駆動回路を有する電力変換装置をより少ない部品と簡単な構成で実現する。

【解決手段】 上側スイッチング素子(1−SW2)を駆動する上側ゲート駆動回路(1−G2)と、下側スイッチング素子(1−SW1)を駆動する下側ゲート駆動回路(1−G1)と、を有する電力変換装置に、前記上側ゲート駆動回路については負電圧電源回路(1−E3)を備え、前記下側ゲート駆動回路については負電圧電源を作り出す下側ブートストラップ回路(1−B2)を備えた。

(もっと読む)

電力変換器のゲート駆動回路

【課題】ゲート信号のオン状態が所定期間以上継続することを防止すること。

【解決手段】電力変換器(3)のスイッチング素子(301〜304)のオン期間を規定するパルス信号(S1〜S4)を絶縁用のトランス(201)に入力し、トランス(201)から出力される信号を用いてスイッチング素子(301〜304)のゲートに与えるゲート信号を形成するゲート駆動回路である。トランス(201)から出力される信号を整形する整形手段(202)と、整形手段(202)によって整形された信号が所定期間オン状態を継続した場合に前記ゲート信号をオフ状態にさせる信号オフ手段(203、204、205)とを備える。

(もっと読む)

ゲート駆動回路

【課題】複数個直列に接続された素子の過電流保護を確実、かつ安全に行ない得るようにする。

【解決手段】複数個直列接続される半導体素子1a〜1cと対応して設けられるゲート駆動回路3a,3b,3cを、絶縁トランス14a〜14cおよび信号線13を介して互いに接続し、いずれかの過電流判定回路8において過電流と判断されたら、当該過電流判定回路8から他のゲート駆動回路へその旨の信号を伝送することにより、他のゲート駆動回路でも過電流保護動作が行なわれるようにする。

(もっと読む)

電圧駆動型半導体素子のドライブ回路及びインバータ装置

【課題】正電圧の電源のみで、導通損失を増加させることなく、誤点弧を防止する電圧駆動型半導体素子のドライブ回路及びインバータ装置を提供する。

【解決手段】半導体素子を駆動するドライブ回路において、直流電源の正側に接続された第1のスイッチと、第1のスイッチの他端子に接続され、かつ直流電源の負側に接続された第2のスイッチと、直流電源の正側に接続された第3のスイッチと、第3のスイッチの他端子に接続された第4のスイッチと、第4のスイッチの他端子に接続され、かつ直流電源の負側に接続された第5のスイッチと、第1のスイッチの他端子と第4のスイッチの他端子に接続されたコンデンサを備え、半導体素子のゲートは第3のスイッチの他端子に接続され、半導体素子のソースは直流電源の負側に接続する。

【効果】正電圧の電源のみで、半導体素子のゲートに負電圧を印加することが可能となる。

(もっと読む)

インバータ回路

【課題】ハイサイドドライバを使用することなく、GND基準の低圧信号によりp型MOS−FETが制御されるインバータ回路を提供する。

【解決手段】インバータ回路は、ハイサイドMOS−FET(12)とローサイドMOS−FET(13)とが入力信号に従って一方がONし他方がOFFするインバータ回路において、上記入力信号のDCレベルをカットするDCレベルカット用コンデンサ(1、2)と、上記DCレベルがカットされた入力信号の最小ピーク値を電源電圧の近傍の値にクリップし上記ハイサイドMOS−FETのベースに出力する第1のトランジスタ(7)と、上記DCレベルがカットされた入力信号の最大ピーク値をGNDの近傍の値にクリップし上記ローサイドMOS−FETのベースに出力する第2のトランジスタ(8)と、を備える。

(もっと読む)

半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】半導体スイッチング素子の両端電圧を直列コンデンサを介し、ハーフブリッジ形ダイオード整流器により整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための逆バイアス側電源として供給する。

(もっと読む)

電圧駆動型半導体スイッチング素子の駆動回路

【課題】上下アーム数が複数相分ある場合でも最小限の部品を追加するだけで、オフ状態のスイッチング素子への逆バイアス電圧の印加を可能にする。

【解決手段】主回路用直流電源の正極と負極との間に直列に接続されて交互にオン・オフを繰り返す2つの電圧駆動型半導体スイッチング素子を駆動する駆動回路において、前記スイッチング素子のうち主回路用直流電源1の正極に接続された上アーム素子2のオン時に、逆バイアス用直流電源9からダイオード10を介して充電される逆バイアス用コンデンサ11を備え、上アーム素子2のオフ時に、逆バイアス用コンデンサ11の充電電圧により上アーム素子2に逆バイアス電圧を印加する。

(もっと読む)

絶縁ゲート型半導体素子の駆動回路

【課題】単一の直流電源を使用しながらも簡単な構成で、ターンオン時の逆バイアス電圧の印加を実現できる絶縁ゲート型半導体素子の駆動回路を提供する。

【解決手段】ゲート電圧に応じて、グランドラインに接続されたエミッタと所定の電圧が供給されるコレクタとの間に流れる電流を制御する絶縁ゲート型半導体素子を駆動する駆動回路は、グランドラインGNDと直流電圧VDが供給される電圧ラインとの間に直列接続され、絶縁ゲート型半導体素子PTのゲート電圧を制御するためのトランジスタQ1,Q2と、ゲート電圧を直流電圧VDより低く維持するための電圧クランプ回路と、絶縁ゲート型半導体素子PTのゲートとトランジスタQ1,Q2の接続点との間に設けられ、絶縁ゲート型半導体素子PTのオン時に充電され、オフ時に逆バイアス電圧を発生するコンデンサC1などで構成される。

(もっと読む)

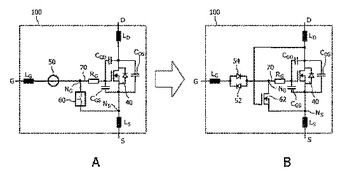

スイッチング回路装置

スイッチング回路装置100は、電界効果トランジスタ40と、電界効果トランジスタ40のゲート電圧を特に、或る閾値、特に或る正の閾値レベル下にして、電界効果トランジスタ40のゲート電圧にバイアスをかける回路50,52,54,60,62とを有している。実施形態においては、逆回復及びゲートバウンスが同時に軽減される。一実施形態においては、バイアス回路は、電界効果トランジスタ40のゲート電圧にバイアスをかけるために、電界効果トランジスタ40のゲートGと直列に接続されたバイアスダイオード52と、電界効果トランジスタ40のゲート電圧を或る閾値、特に或る正の閾値レベル下にするために、電界効果トランジスタ40のゲートGと電界効果トランジスタ40のソースSとの間に接続されたクランピング電界効果トランジスタユニット62とを有している。  (もっと読む)

(もっと読む)

1 - 20 / 27

[ Back to top ]