Fターム[5H740LL01]の内容

Fターム[5H740LL01]に分類される特許

21 - 37 / 37

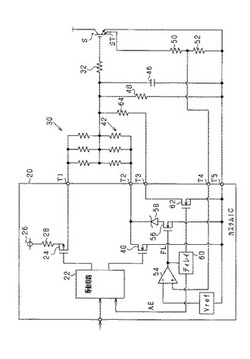

電力変換回路の駆動回路

【課題】電圧制御形のパワースイッチング素子Sに過度の電流が流れることを回避する処理を行う場合、サージが大きくなるおそれがあること。

【解決手段】パワースイッチング素子Sのセンス端子STから出力される電流による抵抗体52での電圧降下量は、コンパレータ54によって、閾値電圧Vrefと大小関係が比較される。これにより、パワースイッチング素子Sを流れる電流(コレクタ電流)が閾値を超えるか否かを判断する。そして、閾値を超えると判断される場合、スイッチング素子56をオンすることで、パワースイッチング素子Sのゲートの電圧をツェナーダイオード58のブレークダウン電圧程度に制限する。ツェナーダイオード58のカソード及びパワースイッチング素子Sのゲート間には、放電用抵抗体42が接続されている。

(もっと読む)

半導体素子駆動回路

【課題】半導体素子の種類によらず半導体素子を確実に保護することが可能な半導体素子駆動回路を提供する。

【解決手段】このIGBT駆動回路では、IGBT1のゲート−補助エミッタ間にトランジスタ6を接続し、IGBT1の主電流Iが所定値I1を超えたことに応じてトランジスタ6を導通させ、その所定時間Td1経過後に制御信号VCを「L」レベルにし、トランジスタ6を非導通にするとともにIGBT1のゲートの電荷を抵抗素子20およびトランジスタ17を介して放電させる。したがって、IGBT1のコレクタに発生するサージ電圧VSを小さく抑制できる。

(もっと読む)

スイッチング回路、及びトランジスタの駆動回路

【課題】トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制すること等。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

(もっと読む)

インバータ装置

【課題】

パワーモジュールに大きな電流を流すインバータ装置であっても、高電位側IGBTを駆動する信号の基準電位端子とゲート駆動ICの基準電位端子間の逆サージを効果的に回避する。

【解決手段】

高電位側のIGBT121及び低電位側のIGBT123を有するIGBTモジュール113と、高電位側IGBT121及びIGBT123を駆動する信号を出力するゲート駆動IC101と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と低電位側のIGBT123のコレクタ端子117との間に設けられた容量128と、ゲート駆動IC101の高電位側IGBT駆動信号用基準電位端子106と高電位側IGBT121のエミッタ端子116との間に設けられた抵抗127と、を有するインバータ装置。

(もっと読む)

電圧制御型トランジスタのゲートドライブ回路

【課題】安定した電圧で充電して当該充電電圧をターンオフ時に利用することができ、しかもターンオフ時にパルストランスの二次巻線側に設けたゲート放電用トランジスタを高速にオンすることができる電圧制御型トランジスタのゲートドライブ回路を提供する。

【解決手段】パルストランス10とMOSトランジスタ20とダイオード21とコンデンサ30とダイオード31とゲート放電用pnpトランジスタ40と抵抗41とを備え、一次巻線11に印加された電圧によって二次巻線12に発生する電圧をトランジスタ20およびダイオード21を介して電圧制御型トランジスタ50のゲートに印加するとともにダイオード31を介してコンデンサ30を充電し、一次巻線11に印加される電圧が印加されなくなることで二次巻線12に発生する逆電圧によりコンデンサ30、抵抗41、ダイオード21、トランジスタ20を介する電流が流れる。

(もっと読む)

電力変換装置

【課題】ダイオードリカバリによるサージ電圧を抑制すると共に、半導体スイッチング素子のターンオン時の損失増加を抑えることにより、電力変換効率の低下を抑えることが可能な電力変換装置を提供する。

【解決手段】ゲート抵抗で第1半導体スイッチング素子のスイッチング速度を決定し、第1半導体スイッチング素子を駆動する第1のゲート駆動回路7と、前記半導体スイッチング素子に制御パルスを供給する制御パルス発生回路12の出力端に、第2半導体スイッチング素子のゲートの充電開始から所定の時間後にオンするスイッチ素子であるPチャネル型のMOS-FET15とツェナーダイオード16との並列回路を直列に接続し、更に並列回路の出力端をゲート抵抗17を介して第2半導体スイッチング素子のゲート端子に接続し、第2半導体スイッチング素子を駆動する第2のゲート駆動回路8とを備える。

(もっと読む)

ドライバ回路

【課題】パワーデバイスのゲートにコンデンサと抵抗の直列回路を接続することなく、損失およびノイズを低減するとともに、ドライブ能力を向上させることが可能なドライバ回路を提供する。

【解決手段】ドライバ回路には、IGBT43のゲート電圧波形を設定するスロープ設定回路13を設け、スロープ設定回路13の出力電圧V*をオペアンプ14の非反転入力端子に入力するとともに、抵抗15、16にて分圧された電圧Vgsfをオペアンプ14の反転入力端子に入力し、スロープ設定回路13の出力電圧V*と、抵抗15、16にて分圧された分圧電圧Vgsfとの偏差に比例した出力電圧Voutをオペアンプ14から出力させて、IGBT43のゲート端子に入力する。

(もっと読む)

サイリスタ用ゲート駆動装置

【課題】サイリスタ素子がターンオフ時に故障しないようにする。

【解決手段】サイリスタ素子2の制御電極3のゲート電圧を正電位にする順バイアス電圧手段5と、負電位にする逆バイアス電圧手段6とを具備したサイリスタ用ゲート駆動装置において、サイリスタ素子の主電極に流れる陽極電流又は陰極電流の電流値を監視する電流監視手段10と、この電流監視手段で検出された電流値が入力され、この入力された電流のサイリスタ素子がターンオフ開始直前の電流値が、サイリスタ素子のオン電流最大定格値に対してどのくらいの割合であるかを演算する電流演算手段11と、この電流演算手段の出力値に対応して、サイリスタ素子の制御電極に印加するゲート電圧の逆バイアス定常値を制御する逆バイアス定常値制御手段12とを備えている。

(もっと読む)

モータ制御装置、及びモータ制御方法

【課題】 モータの駆動制御に伴って、装置各部の温度が上昇し、その許容温度に対して

余裕がなくなってきた場合は、温度上昇を抑制する効果が得られる制御を行い、一方、そ

の許容温度に対して余裕がある場合は、モータ電流の歪やスイッチング動作に起因するノ

イズを低減する効果が得られる制御を行うことができ、装置の発熱状態に応じて適切なモ

ータの駆動制御を実行することができるモータ制御装置を提供すること。

【解決手段】 モータ50に駆動電流を供給するラインに介装されるスイッチング回路4

と、スイッチング回路4を駆動させるためのプリドライバ3と、プリドライバ3を駆動さ

せてモータ50の駆動を制御するモータ制御手段20と、スイッチング回路4のスイッチ

ング切替時の動作速度を切り替えるための動作速度切替手段11と、発熱状態に基づいて

動作速度切替手段11の設定を切り替える切替制御手段20とを装備する。

(もっと読む)

制御モータ駆動装置

【課題】本発明は上記課題に鑑み、インバータ回路におけるスイッチング素子の出力電流に発生するノイズを同期的に低減させ、インバータ回路によって駆動される制御モータの誤作動を有効に防止し得る制御モータ駆動装置の提供を目的とする。

【解決手段】制御モータ駆動装置100を構成するインバータ回路240は、ドライブ回路141と複数のスイッチ回路242a〜242fと電流検出回路143とを備えている。そして、インバータ回路240に配備されるそれぞれのスイッチ回路242a〜242fは、ゲートGに接続される調整抵抗Rga〜Rgfと、エミッタE−コレクタC間に接続される帰還ダイオードD1a〜D1fと、ゲートG−エミッタE間に接続される吸収ダイオードD2a〜D2fとを備えるスイッチング素子Tra〜Trfから構成されている。

(もっと読む)

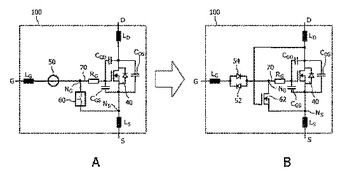

スイッチング回路装置

スイッチング回路装置100は、電界効果トランジスタ40と、電界効果トランジスタ40のゲート電圧を特に、或る閾値、特に或る正の閾値レベル下にして、電界効果トランジスタ40のゲート電圧にバイアスをかける回路50,52,54,60,62とを有している。実施形態においては、逆回復及びゲートバウンスが同時に軽減される。一実施形態においては、バイアス回路は、電界効果トランジスタ40のゲート電圧にバイアスをかけるために、電界効果トランジスタ40のゲートGと直列に接続されたバイアスダイオード52と、電界効果トランジスタ40のゲート電圧を或る閾値、特に或る正の閾値レベル下にするために、電界効果トランジスタ40のゲートGと電界効果トランジスタ40のソースSとの間に接続されたクランピング電界効果トランジスタユニット62とを有している。  (もっと読む)

(もっと読む)

絶縁ゲート型半導体素子のゲート回路

【課題】 負側電源の故障が発生しても、絶縁ゲート型半導体素子が誤オン動作しないような安全な絶縁ゲート型半導体素子のゲート回路を得る。

【解決手段】 正側電源2Aと負側電源2Bで動作し、絶縁ゲート型半導体素子3のゲート駆動を行うFET12A及びFET12Bから成るトーテムポール回路と、ゲート制御IC11と、ゲート制御ICの出力とFET12Aのゲート間に設けたツェナーダイオード15A及び抵抗14Aから成る直列回路と、ゲート制御ICの出力とFET12Bのゲート間に設けたツェナーダイオード15B及び抵抗14Bから成る直列回路とで構成し、ツェナーダイオード15Aの降伏電圧は、正側電源の電圧からFET12Aのゲートしきい値電圧を減算した値より大きく、ツェナーダイオード15Bの降伏電圧は、負側電源の電圧からFET12Bのゲートしきい値電圧を減算した値より小さく選定する。

(もっと読む)

スイッチング素子保護回路

【課題】 スイッチング素子を大型化せずに高温動作時におけるスイッチング素子の特性劣化や破壊を防止できるスイッチング素子保護回路を提供する。

【解決手段】 本発明によるスイッチング素子保護回路は、MOS-FET(4)の動作温度を検出する温度検出用サーミスタ(11)と、温度検出用サーミスタ(11)により検出した動作温度が所定のレベルを越えるときに保全信号を発生する比較回路(12)と、過電圧保護回路(10)の検出電圧を設定する2つのアバランシェダイオード(5,6)とMOS-FET(4)の制御端子(G)との間に接続された切換手段(13)を構成するトランジスタ(14)とを備え、比較回路(12)の保全信号が発生したときにトランジスタ(14)をオン状態にして過電圧保護回路(10)の検出電圧を低下させる。これにより、高温動作時のMOS-FET(4)が低下した安全動作領域内での動作に切り換わるので、高温動作時におけるMOS-FET(4)の特性劣化や破壊を防止できる。

(もっと読む)

スイッチング回路

【課題】 スイッチング素子に半導体素子を用いてこれをパルス駆動する際に、良好なスイッチング特性を有するスイッチング回路を得る。

【解決手段】 スイッチング回路1をONする際は、半導体スイッチング素子11の制御端子としてのゲート端子Gのインピーダンスを、このスイッチング回路1の制御信号の立ち上がりを微分するように開放値から短絡値を経て抵抗15に相当する値に安定させる。また、スイッチング回路をOFFする際は、この抵抗15に相当するインピーダンス値から開放値まで変化させている。これによって、制御信号入力端子に印加されるパルス状の制御信号に対する応答速度を速める。

(もっと読む)

半導体集積回路装置

【課題】本発明は、電源電圧変動(パルス重畳)に依ることなく、高精度の熱保護動作を行うことが可能な半導体集積回路装置を提供することを目的とする。

【解決手段】上記目的を達成すべく、本発明に係る半導体集積回路装置の熱保護回路1は、電源電圧Vccから高周波数成分を除去するフィルタ手段を有して成る構成、具体的には、基準電圧Vrefを生成するバンドギャップ電源部BG及び抵抗R1、R2と、温度検出用のトランジスタN1と、電源電圧VccからトランジスタN1のオン/オフ状態に応じた制御信号Sctrlを生成する抵抗R3、R4と、制御信号Sctrlに応じてオン/オフ制御されるトランジスタP1と、トランジスタP1のオン/オフ状態に応じて熱保護信号Stsdを生成するトランジスタN2及び抵抗R5、R6と、を有するほか、前記フィルタ手段として、トランジスタP1のエミッタ及びコレクタに各々接続された抵抗R7及び容量C1を有して成る構成とされている。

(もっと読む)

半導体スイッチ回路および電力変換装置およびインバータ装置および空気調和機

【課題】半導体スイッチ用の駆動電源を不要とし、信頼性が高く、応答速度が速く、スイッチング特性にあわせた適切な駆動制御が可能といった半導体スイッチ回路半導体スイッチ回路およびその応用商品を提供することを目的とする。

【解決手段】半導体スイッチ100と、電源供給手段102と、電圧昇圧手段103とを備え、前記電源供給手段102の出力電圧は、前記半導体スイッチ100の動作電圧以下であることを特徴とするもので、電源供給手段102における2次側回路が簡素化され部品点数が削減できる。また、常に半導体スイッチ100における最適なスイッチング速度を具現化するゲート駆動を電圧昇圧手段103における昇圧動作で実現できる。

(もっと読む)

トライアックのトリガを制御するシステムおよび方法

この発明は、トライアックのゲートへの単一の短い期間のパルスであらゆる力率の負荷を動作させることにより、トライアックを制御しトリガするシステムに関する。単一のコンパレータ(CP1)を使用するために、また、電流レベル(Ic)で制限することなく動作させるために、トライアックを制御しトリガするシステムが予見され、前記トライアックはゲートを備え、かつ、負荷に接続され、ゲートは、制御ユニット4に接続され、 制御ユニットは、回路電圧Vacを負荷に印加して電流Icを流すためにトライアックを動作させ、システムは、ゲート電圧検出ユニット(1)、制御ユニット(4)、制御ユニット(4)に接続のゲート電圧検出ユニット(1)を備え、制御ユニットはゲート電圧限界値(+LIMIT,−LIMIT)を確立し、トライアックの導通を維持するためゲートにパルスを発生させ、ゲートでのパルスは、前記電圧限界値と、ゲート測定電圧との比較から発生され、制御ユニットは、Icを測定し、Icに比例して電圧限界値を調節する。

(もっと読む)

(もっと読む)

21 - 37 / 37

[ Back to top ]