Fターム[5J001BB20]の内容

Fターム[5J001BB20]に分類される特許

101 - 116 / 116

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

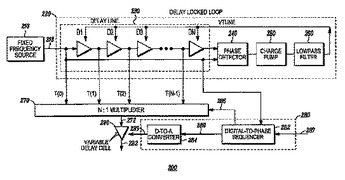

周波数合成の方法と装置

DPC(200)であって、周波数源(20)と、クロック信号を受信し複数の位相シフトされたクロック信号を生成する遅延ロックループ(220)と、合成信号の所望の周波数を識別する入力信号を受信する為の、DPS(282)とDAC(284)とを有した制御装置(280)と、複数の位相シフトされたクロック信号を受信し、位相シフトされたクロック信号の1シーケンスを選択し、粗い合成信号を出力する選択回路(270)と、可変遅延セル(290)とがあるDPC(200)であり、可変遅延セル(290)が、粗い合成信号を修正して、周波数が実質的には所望の周波数である合成信号(292)を生成する為に、粗い合成信号を受信するべく選択回路に結合された第1の入力と、微同調調整信号を受信する為に制御装置に結合された第2の入力とを有している。DPCには更に、DPCを較正するトレーニング装置がある。  (もっと読む)

(もっと読む)

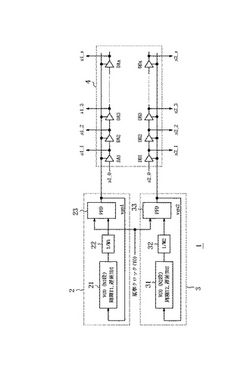

半導体集積回路装置のタイミング制御回路

【課題】半導体集積回路装置の制御対象回路に与える制御信号が製造プロセスや電源電圧、周囲温度などの変動によって変動するのを抑制すること。

【解決手段】外部クロックextCLKに基づき基準信号actCLKを生成する中央制御回路2側に、遅延値を制御するディジタル値DCTRL[n:0]からなる遅延制御信号を生成する遅延制御回路6を設け、中央制御回路2からローカル制御回路3に対して基準信号と遅延制御信号とを供給する。ローカル制御回路3に設けた可変遅延回路7は、遅延値がディジタル値で制御される単位遅延回路を多段に接続して構成され、メモリセルアレイ1に供給する各種の制御信号を、前記基準信号を前記遅延制御信号のディジタル値が示す所定の遅延値だけ遅延したタイミングで生成する。

(もっと読む)

容量装置及び半導体装置並びにそれを用いたマルチバイブレータ

【課題】二端子間に接続されて用いられる容量装置及び半導体装置並びにそれを用いたマルチバイブレータに関し、寄生容量の影響を低減できる容量装置及び半導体装置並びにそれを用いたマルチバイブレータを提供することを目的とする。

【解決手段】 本発明は、二端子(a、b)間に接続される容量装置(C100、C200)において、複数の容量素子(C10、C20)を、二端子(a、b)の両方の端子から見た素子容量(C11、C21)及び寄生容量(C12、C22)の配置が対称となるように接続したことを特徴とする。

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

発振回路

【課題】遅延時間を細かく制御でき、発振回路の発振周波数のステップ幅を低減でき、且つ簡単な回路構成でディジタル信号で制御可能な遅延回路を用いた発振回路を提供する。

【解決手段】遅延回路の最後段の遅延素子DLYnの出力信号CKnはNANDゲートNGT1を介して、遅延回路の入力端子に帰還され、環状発振回路(リングオシレータ)が構成され、NANDゲートNGT1の一方の入力端子は遅延素子DLYnの出力端子OUTに接続され、他方の入力端子は発振回路の動作/停止状態を制御する制御信号SONの入力端子に接続されている。

(もっと読む)

ディジタル処理コンポーネントの給電レベルを調節するシステム及びこれを動作させる方法

可変動作周波数をもつディジタル処理コンポーネント(100)の給電レベル、VDD、を調節するための制御回路(125)が開示される。制御回路(125)は、N個の遅延セル(201)と給電調節回路(210、215、220)とを包含する。N個の遅延セル(201)は直列に結合され、その各々はVDDの値により決定される遅延Dを持ち、その結果最初の遅延セル(201a)の入力に印加されたクロック縁はN個の遅延セル(201n)を通り順次リップルする。給電調節回路(210、215、220)はVDDを調節可能でまた(i)少なくともK遅延セル(201)及びK+1遅延セル(201)の出力をモニタし、(ii)クロック縁がK遅延セル(201)の出力に到達しそしてK+1遅延セル(201)の出力には到達していないことを決定し、(iii)それに応じVDDを調節可能な制御信号を発生する。  (もっと読む)

(もっと読む)

発振器

【課題】 発振周波数の調整範囲を広く取ることによって製造歩留まりを向上させることができる発振器を得る。

【解決手段】 リング状に接続された複数の遅延回路とを有する発振器において、各遅延回路は、直列に接続されたインバータ、遅延部及び遅延微調整部を有し、遅延部は、外部から入力された制御電圧に応じた遅延を入力信号に付加し、遅延微調整部は、外部から入力された微調整信号に応じた遅延を入力信号に付加する。また、定電流回路と電圧制御回路とを有する。そして、電圧制御回路が電圧制御信号に応じた電圧を定電流回路に供給する。また、定電流回路が電圧に応じた電流を各遅延回路に供給する。そして、複数の遅延回路が電流に応じた遅延を入力信号に付加する。

(もっと読む)

パルス発生器

連続する2つの遅延素子(D1,D2,D3,D4,D5)ごとに複数の結合点(A1,A2,A3,A4,A5)で結合された、遅延素子(D1,D2,D3,D4,D5)の直列結合を備え、前記遅延素子(D1,D2,D3,D4,D5)の直列結合はそれぞれ第1信号(y)及び第2信号(x)に結合された第1端(A0)及び第2端(A5)を持っており、第1及び第2信号(x,y)は同一周波数を持っていると共に互いに位相がずらされているパルス発生器において、2つの互いに異なる結合点(A2,A3)に結合され、2つの異なる結合点間の遅延素子の数と遅延素子の直列結合の総遅延時間との比率によって決定される時間幅の出力パルス(O)を発生するゼロクロス検出器(3)をさらに備えることを特徴とする。  (もっと読む)

(もっと読む)

パルス幅変調回路

【課題】

高速、高精度の動作を実現できるパルス幅変調回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路では多相クロック生成回路2によって基準クロックに基づき多相クロック信号を生成する。そして、入力データと、多相クロック生成回路2によって生成された多相クロック信号とに基づいてパルス幅変調信号を生成する。ここで、多相クロック生成回路2は、位相ロックループ回路を有し、位相ロックループ回路によって生成された中間クロック信号をさらに位相補間することにより多相クロック信号を生成する。

(もっと読む)

周波数可変発振回路並びにそれを用いた位相同期回路及びクロック同期回路

【課題】低い電源電圧で動作し、かつ、高い周波数で発振することができる周波数可変発振回路並びにそれを用いた広い発振周波数範囲を有する位相同期回路及びクロック同期回路を提供すること。

【解決手段】pMOS及びnMOSトランジスタのゲートを相互に接続して入力端子とし、かつ、ドレインを相互に接続して出力端子とした相補型増幅回路を用いて差動増幅回路及び入出力端子を互いに交叉して接続した正帰還回路を構成し、差動増幅回路の出力端子間に正帰還回路を接続し、前記相補型増幅回路のソース電流を制御するための周波数制御信号をゲートに入力するMOSトランジスタと前記相補型増幅回路とを電源端子と接地端子の間に直列に接続して構成した遅延回路を環状に縦続接続して周波数可変発振回路を構成する。

(もっと読む)

可変遅延回路

本発明に係る可変遅延回路は、直列に接続され、基準クロック信号又はデータ信号を順次遅延させる複数段の第1可変遅延素子と、複数段の第1可変遅延素子に並列に接続され、基準クロック信号を遅延させる第2可変遅延素子と、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の位相とを比較する位相比較器と、位相比較器の比較結果に基づいて、複数段の第1可変遅延素子によって遅延された基準クロック信号の位相を、第2可変遅延素子によって遅延された基準クロック信号の所定のサイクル後の位相と略等しくすべく、複数段の第1可変遅延素子のそれぞれの遅延量を制御する遅延量制御部とを備える。 (もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

クロックパルス幅調整回路

【課題】半導体集積回路の動作速度を保証すると共に、ダイナミック回路の動作時のピーク電流が単一時間に集約されることを防ぎ、EMIを抑制することを目的とする。

【解決手段】トランジスタ駆動能力測定回路333によりプロセスのばらつきによるトランジスタの駆動能力を測定し、クロックパルス変更回路444にて測定結果に基づいてクロックパルスの立ち上がりおよび立ち下りのタイミングを変更することにより、最適なタイミングでダイナミック回路251を動作させることができ、半導体集積回路の動作速度の保証を行うことができる。

(もっと読む)

可変遅延生成回路

【課題】 電流制御型発振回路4から出力されるクロック8の遅延量を細かく設定する。

【解決手段】 制御電圧1を入力し、この制御電圧1の大きさに対応した可変電流3を出力するV/Iコンバータ2と、可変電流3を入力し、この可変電流3の大きさに対応した周波数のクロック8を出力する電流制御型発振回路4と、クロック8、及び可変電流3を入力し、この可変電流3の大きさに対応した遅延をクロック8につけて出力する電流制御型遅延回路9とを備えるものとした。

(もっと読む)

101 - 116 / 116

[ Back to top ]