Fターム[5J001BB20]の内容

Fターム[5J001BB20]に分類される特許

21 - 40 / 116

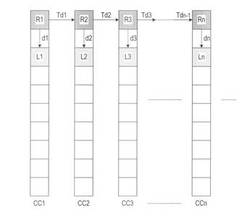

パルス遅延回路の構成方法

【課題】プログラマブルロジックデバイス上に、遅延ユニット毎の遅延時間のばらつきの少ないパルス遅延回路を構成する。

【解決手段】FPGAには、1列に配置された複数のロジックセルからなるセル列が多数設けられており、同一のセル列に属する二つのロジックセル間の伝送(以下「同セル列内伝送」という)と、異なるセル列に属する二つのロジックセル間の伝送(以下「異セル列間伝送」という)とでは、遅延が異なったものとなる。ストレートディレイラインを構成する遅延ユニットR1〜RnをFPGAに実装する際にマニュアルで配置する。具体的には、遅延ユニットR1〜Rnを隣接するn個のセル列CC1〜CCnに一つずつ割り当て、しかも、遅延ユニットR1〜Rnが、その接続順に並ぶように、セル列CCi(i=1,2,…,n)に遅延ユニットRiを割り当る。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路の出力の相対的な遅延時間の分解能を高くする。

【解決手段】

信号発生装置(1)は、複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する複数の積分回路(111,112)と、前記複数の積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する複数の比較回路と(121,122)、前記各比較信号を入力し、これらの入力信号の全部または一部を、セットされた時間だけ遅延させた遅延信号を出力する少なくとも1つの遅延回路と(131,132)、前記各遅延信号、および前記遅延回路によっては遅延されていない比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた信号を出力する信号処理回路(14)とを備える。

(もっと読む)

発振回路

【課題】チップ面積を増大させることなく、低消費電流で安定した動作周波数を実現する。

【解決手段】発振回路は、電圧発生回路、ランプ電圧発生回路、及びアンプ回路を有する第1及び第2の遅延回路と、第1及び第2の遅延回路からの遅延信号が入力されるフリップフロップ回路とを備える。電圧発生回路は、電源線に接続された第1の電流源と、この第1の電流源及び接地線間にカスケード接続された第1及び第2のEMOSトランジスタと、ドレインが電源線、ゲートが第1のEMOSトランジスタにそれぞれ接続されたDMOSトランジスタと、このDMOSトランジスタ及び接地線間にカスケード接続され、それぞれ第1及び第2のEMOSトランジスタにゲートが共通接続された第3及び第4のEMOSトランジスタとを含み、DMOSトランジスタのソースから出力電圧を出力することを特徴とする。

(もっと読む)

チャネル間遅延補正回路及びそれに用いるチャネル間遅延補正方法

【課題】 BER特性等の性能を向上させることが可能なチャネル間遅延補正回路を提供する。

【解決手段】 チャネル間遅延補正回路は、各々異なる第1及び第2の入力信号をアナログ/ディジタル変換する第1及び第2の変換回路(A/D変換器8,9)と、第1及び第2の変換回路各々の出力をそれぞれ遅延する第1及び第2の遅延回路(固定遅延回路10、可変遅延回路11)と、第1及び第2の遅延回路各々の出力を基に第1及び第2の入力信号のチャネル間の遅延時間に相当する遅延時間誤差を出力する演算回路(乗算器13)と、演算回路の演算結果を基に第1及び第2の遅延回路の一方に対して遅延時間差がなくなるように遅延量を制御する制御回路(ループフィルタ12)とを有する。

(もっと読む)

偶数段パルス遅延装置

【課題】偶数段パルス遅延装置において、リングディレイライン内でのパルスの周回動作の停止を自動で検出して、再起動等の処理を適正に実行できるようにする。

【解決手段】偶数段パルス遅延装置は、NAND1、INV(インバータ)2〜31及びNAND32からなる偶数個の反転回路がリング状に連結され、NAND32の制御用端子にインバータINV18の出力が接続されたリングディレイライン10を備える。リングディレイライン10は、NAND1の起動用端子にスタートパルスPAを入力すると起動し、パルスを周回させるが、外乱ノイズ等によって周回動作が停止することがある。そこで、INV31の出力を監視し、その出力が、リングディレイライン10内でパルスが一周するのに要する時間以上変化しないときに、リングディレイライン10の動作が停止したと判断して、リングディレイライン10を再起動する動作判定部20を設ける。

(もっと読む)

局部発振器信号のためのデューティサイクル調整

局部発振器(LO)モジュールは、局部発振器と、フィードバック回路と、を備える。局部発振器は、電源電圧でバイアスがかけられ、デューティサイクルを有する局部発振器信号を生成する。フィードバック回路は、局部発振器信号の電圧レベルを表す第1の電圧信号と、局部発振器信号に関する希望されるデューティサイクルに対応する電源電圧の部分の電圧レベルを表す第2の電圧信号との間の差に応答して局部発振器信号のデューティサイクルの絶対的調整を行う。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】主電源とバックアップ電源とを切り換える切換回路を内蔵しないリアルタイムクロック用の半導体集積回路において、バックアップモードにおける消費電力を低減する。

【解決手段】この半導体集積回路は、外部の主電源による第1の電源電圧又は外部のバックアップ電源による第2の電源電圧が選択的に供給されて動作する半導体集積回路であって、第1又は第2の電源電圧に基づいて第3の電源電圧を生成する定電圧回路と、第3の電源電圧が供給されて原振クロック信号を生成する発振回路と、原振クロック信号を分周し、分周されたクロック信号に基づいて計時情報を管理するロジック回路と、第1の電源電圧が供給されているか否かを表す信号に従って、第1の電源電圧が供給されていないときに、定電圧回路から出力される第3の電源電圧の値又は定電圧回路の動作期間を減少させる制御回路とを具備する。

(もっと読む)

DLL回路

【課題】本発明は、電圧制御発振部を用いて多相クロックを生成し、そのうちで基準クロックに同期されるクロックを選択して、遅延クロックとして提供するDLL回路を提供する。

【解決手段】本発明は、基準クロックを単位時間だけ遅延させて複数の多相クロックを生成し、複数の多相クロックの何れか一つと基準クロックとの周波数が一致する時にイネーブルされるイネーブル信号を生成するように構成される多相クロック生成部;及び、イネーブル信号がイネーブルされると、制御信号により複数の多相クロックの何れか一つを所定時間遅延させて基準クロックの位相と比較し、複数の多相クロックのうち、基準クロックと位相が一致する多相クロックを遅延クロックとして生成するように構成される多相クロック選択部を含むことを特徴とする。

(もっと読む)

絶対遅延時間発生装置

【課題】外部水晶体を参照信号源とせずに、正確な周波数を発生する。

【解決手段】PVT検知装置は複数の遅延モジュールと信号位相/周波数制御モジュールを含む。各遅延モジュールは対照ユニットと参照ユニットを含む。対照ユニットと参照ユニットは互いにPVTに対する異なる感度の遅延特性を有する。各遅延モジュールは入力信号がそれぞれ対照ユニットと参照ユニットを通ってから生じた位相又は周波数の相違を対照し、各遅延モジュールの遅延パラメータを発生する。信号位相/周波数制御モジュールは各遅延パラメータを受けて対照し、絶対遅延時間発生装置の外部環境のPVT状態を検出し、遅延時間発生器を制御して補正することにより、正確な絶対遅延時間を発生する。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

半導体集積回路装置

【課題】PLL回路におけるジッタを低減しながら、ワイドレンジで安定した動作を行う。

【解決手段】PLL回路のオシレータを構成する遅延バッファ7のインバータ13,14は、電流制限用トランジスタであるトランジスタ8を介して電源電流が供給されている。トランジスタ8は、バイアス電流である入力信号in1に応じてインバータ13,14に供給する電流制限する。このトランジスタ8を設けたことにより、発振周波数の低い帯域における該インバータ13,14に流れるリーク電流を防止することができる。

(もっと読む)

デジタルDLL回路及び半導体装置

【課題】出力信号のジッターを低減可能としたデジタルDLL回路を提供する。

【解決手段】クロック信号CLKを1周期遅延させるための固定遅延素子の段数を選択する位相判定部1と、位相判定部1で選択した固定遅延素子の段数に基づいて、入力信号INを任意の位相量だけ遅延させて出力する固定遅延素子の段数を選択する位相調整部21とを備えたデジタルDLL回路において、位相調整部21は、選択信号に基づいて、複数段の固定遅延素子と、該固定遅延素子の1段当たりの遅延時間を1/2n刻みで調整する可変遅延部とで生成する遅延時間で、入力信号INを任意の位相量遅延させた出力信号OUTを生成する。

(もっと読む)

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

位相制御装置、位相制御プリント板、制御方法

【課題】出力信号の位相を微小に制御することを課題とする。

【解決手段】第1の遅延ラインでは、入力信号の入力を受け付けると、信号の位相に対して遅延量を加える遅延器各々によって当該入力信号の位相に対して遅延量を加えるとともに当該遅延器ごとの遅延信号を出力し、DLL回路では、第2の遅延ラインが、外部にて周波数の異なる信号に切り替えることが可能である外部信号の入力を受け付けると、遅延器各々によって当該外部信号の位相に対して遅延量を加え、第2の遅延ラインの複数の遅延器すべてによって遅延された遅延信号と、当該第2の遅延ラインにて遅延量が加えられていない外部信号との位相差を比較し、位相比較器によって比較される遅延信号を外部信号に同期させる電圧であって、当該位相比較器によって出力された位相差から生成された制御電圧を、第1の遅延ラインおよび第2の遅延ラインの複数の遅延器各々に入力する。

(もっと読む)

パルス幅補正装置およびパルス幅補正方法

【課題】二値化のコンパレートレベルを調整することなく、データが誤って取り込まれるのを防止すること。

【解決手段】デューティー比検出回路3は、二値化信号DIのデューティー比の基準値からのずれを検出し、遅延回路5は、二値化信号DIを所定の遅延量だけ順次遅延させた遅延信号DLを生成し、セレクタ6は、デューティー比検出回路3にて検出された二値化信号DIのデューティー比のずれに対応した遅延信号DLnを遅延信号DLから選択し、パルス幅補正回路7は、セレクタ6にて選択された遅延信号DLnを用いることにより、二値化信号DIのパルス幅を補正する。

(もっと読む)

バーニア遅延回路、それを用いた時間デジタル変換器および試験装置

【課題】高精度にキャリブレーションが可能なバーニア遅延回路を提供する。

【解決手段】リングオシレータ10は、入力されたバイアス信号SbiasGに応じた周波数で発振する。バイアス信号調節部12は、リングオシレータ10の発振周波数が、所定の基準周波数と一致するように、帰還によりリングオシレータ10に対するバイアス信号SbiasGを生成する。個別バイアス回路14は、N個の第2可変遅延素子D21〜D2Nごとに設けられた複数のバイアス回路BIAS1〜BIASNを備える。各バイアス回路BIAS1〜BIASNは、バイアス信号Sbias2A1〜Sbias2ANを個別に調節可能に構成される。

(もっと読む)

遅延同期ループ回路および表示装置

【課題】所望の単位遅延回路の1個分の遅延追加がなされた場合であっても不安定な単位遅延回路が連続しないようにすること。

【解決手段】本発明は、外部クロックと内部クロックとの位相差を比較する位相比較器1と、位相比較器1からの出力信号により遅延時間を制御するアップダウンカウンタ2と、外部クロックの遅延を制御して内部クロックとするため、アップダウンカウンタ2から出力される信号の複数ビットに対応した複数個の単位遅延回路(Delay-Cell)を備え、この複数個のDelay-Cellを直列に接続するにあたり、アップダウンカウンタ2からの出力における同一ビットの出力により制御されるDelay-Cellが隣り合わないよう接続されるデジタル遅延ライン3とを有する遅延同期ループ回路である。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

21 - 40 / 116

[ Back to top ]