Fターム[5J022CA01]の内容

アナログ←→デジタル変換 (13,545) | 構成入、出力系 (1,145) | 平均値・多数決回路 (112)

Fターム[5J022CA01]に分類される特許

1 - 20 / 112

A/D変換回路、A/D変換方法およびA/D変換プログラム

A/D変換器

【課題】 差動信号のA/D変換を行うA/D変換器においてチャージインジェクションやクロックフィードスルーに起因したA/D変換の誤差を少なくする。

【解決手段】 各A/D変換サイクルにおいて、正相アナログ入力部50Pおよび逆相アナログ入力部50Nは、正相アナログ入力信号INPおよび逆相アナログ入力信号INNをサンプリングし、正相アナログ入力信号INPを正相入力ノードC1PBまたは逆相入力ノードC1NBに、逆相アナログ入力信号INNを逆相入力ノードC1NBまたは正相入力ノードC1PBに供給する。制御部400は、このサンプリングした各信号の供給先をA/D変換サイクル単位で切り換える。A/D変換器では、正相入力ノードC1PBおよび逆相入力ノードC1NB間の電圧のA/D変換が行われる。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

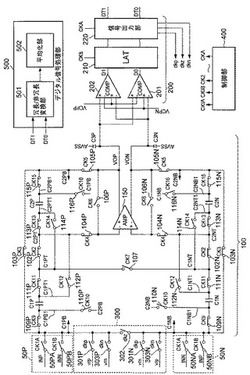

A/D変換器

【課題】 キャパシタの誤差の影響を少なくし、A/D変換器の精度を高める。

【解決手段】 アナログ信号更新部100は、キャパシタC1PおよびC1Nが差動増幅器150の入力側に入力キャパシタとして接続され、キャパシタC2PおよびC2Nが差動増幅器150の入出力間に帰還キャパシタとして接続された第1の状態またはキャパシタC2PおよびC2Nが差動増幅器150に入力キャパシタとして接続され、キャパシタC1PおよびC1Nが差動増幅器150に帰還キャパシタとして接続された第2の状態に切り換え可能である。制御部400は、A/D変換サイクル単位で、A/D変換のための係数乗算処理時のアナログ信号更新部100を交互に第1の状態とし、または第2の状態とする切り換えを行う。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

信号処理装置

【課題】複数のAD変換器を用いて同一のアナログ信号をAD変換する信号処理装置において、個々のAD変換器の特性のばらつきによって生じる同一のアナログ信号のAD変換精度の低下を抑制する。

【解決手段】クロック生成部58はπ[rad]位相の異なる二つのクロックを生成し、対象信号供給部52は受信信号RSまたは0VのいずれかをAD変換部68の二つのAD変換器72、74に供給する。被補正データ生成部86は、AD変換部68が受信信号RSをAD変換した結果に基づき、読出データRDを生成する。オフセットデータ生成部76は、AD変換部68が基準電圧をAD変換した結果に基づき、AD変換器72、74毎の測定誤差を表すオフセットデータAZ1、AZ2を生成する。補正部100は、読出データRDからオフセットデータAZ1、AZ2分を除去する補正処理を実行し、サンプリングデータSDを生成する。

(もっと読む)

ADC

【課題】アナログ入力信号に対する周波数の制限を抑制したバックグランドキャリブレーションを行うADCとその補正回路を提供する。

【解決手段】アナログ入力信号をサンプリング周波数(以下fs)でサンプリングしてデジタル出力信号に変換するADCであって,アナログ入力信号をタイムインタリーブでデジタル出力信号に変換するN個のアナログデジタル変換(以下ADC)チャネルと,N個のADCチャネルがそれぞれ出力するチャネルデジタル信号を合成して前記デジタル出力信号を生成するチャネル合成器と,N個のADCチャネルの少なくとも一つの出力に設けられた適応フィルタと,デジタル出力信号に応じて前記適応フィルタの係数を生成する補正回路とを有し,補正回路は,デジタル出力信号に含まれるアナログ入力信号成分と誤差に対応するイメージ信号成分のうち,イメージ信号成分の直流成分を演算し,直流成分に基づいて当該直流成分が抑制されるように前記係数を演算する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

信号処理装置

【課題】2個のチップを接続する配線本数を削減しつつ、SN比の低下を抑制する。

【解決手段】第1のチップ10は、第2データD2を1ビットの第3データD3に変換するノイズシェーパー14と、第1信号配線L1を介して送信信号YPDMを送信し、第2信号配線L2を介してクロック信号YCLKを送信するPDM送信回路15とを備え、第2のチップ20は、第3データD3を6ビットのデータに変換する移動平均フィルター22と、5ビットの第5データD5を出力するクリップ回路24とDEM−DAC25とを備える。

(もっと読む)

A/D変換器とその補正方法

【課題】A/D変換器においてノイズ等の異常値を除去し高精度のA/D変換結果を出力する。

【解決手段】A/D変換器は、奇数回のサンプリングでビット毎に行う多数決に基づきA/D変換結果を補正する多数決回路M4を具備する。多数決回路M4は、第1判定回路M11、M13、第1補正回路M15、M17、第2判定回路M12、M14、第2補正回路M16、M18を備える。第1判定回路はビット毎のサンプリングによるA/D変換結果の“1”出現回数が第1判定値と一致する場合、桁上げ付近且つ桁上げありと判定する。第1補正回路は、判定されたビットより下位ビットのA/D変換結果を“0”に補正する。第2判定回路はビット毎のサンプリングによるA/D変換結果の“1”出現回数が第2判定値と一致する場合、桁上げ付近且つ桁上げなしと判定する。第2補正回路は判定されたビットより下位ビットのA/D変換結果を“1”に補正する。

(もっと読む)

AD変換装置

【課題】AD変換部の動作周波数及びビット数を変更せずに、回路規模および消費電流の増大なく、デジタル出力の分解能を改善したAD変換装置を提供すること。

【解決手段】AD変換装置は、基準クロックの周期の整数倍の周期の制御クロックを生成する制御クロック生成部と、制御クロックの周期を1サイクルとして、基準クロックの周期毎に異なるシフト電圧を発生するシフト電圧発生部と、シフト電圧によってアナログ信号をオフセットするオフセット部と、オフセットされたアナログ信号を基準クロックの周期毎にAD変換するAD変換部と、制御クロックの周期毎にAD変換部の出力を平均化する平均化部と、を備える。シフト電圧は、基準シフト値を基準として、平均化部の出力の最小分解能の値とシフト電圧の前記基準クロックの周期間のオフセット値との合計がAD変換部の最小分解能の値となり、基準クロックの周期毎に異なる。

(もっと読む)

アナログデジタル変換器

【課題】短時間で誤差を補正することができるアナログデジタル変換器を提供することを課題とする。

【解決手段】アナログデジタル変換器は、アナログ入力電圧をサンプリングするスイッチトキャパシタ回路(101)と、前記スイッチトキャパシタ回路の電圧の正負符号を変換する符号変換回路(401)と、前記符号変換回路の出力電圧を増幅するアンプ(301)と、前記アンプの出力電圧から前記アンプのオフセット電圧を除去するオフセット電圧除去回路(402)と、前記オフセット電圧除去回路の出力電圧をラッチするラッチ回路(302)と、補正モードでは、前記ラッチ回路の出力電圧に応じて前記スイッチトキャパシタ回路の誤差を補正する制御部(103)とを有し、前記スイッチトキャパシタ回路は、アナログデジタル変換モードでは、前記ラッチ回路の出力電圧に応じてアナログ電圧を出力する。

(もっと読む)

光伝送装置およびアナログ−デジタル変換装置

【課題】ADCを適切に補正することができる。

【解決手段】変換部1は、光信号を電気信号に変換する。増幅器2は、変換部1によって変換された電気信号を増幅する。ADC3a〜3nは、増幅器2で増幅された電気信号を時分割でアナログ−デジタル変換する。制御部4は、複数のADC3a〜3nの補正を行う際、複数のADC3a〜3nの出力の合計振幅または平均振幅が所定値以上となるように、増幅器2の増幅率を制御する。

(もっと読む)

A/D変換器

【課題】より一層の高精度化が可能なA/D変換器を提供する。

【解決手段】制御回路(制御手段)5は、積分器1において入力電圧Vinを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第1の二重積分と第1の基準電圧(グラウンド電圧)VAGNDを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第2の二重積分とが選択的に行われるように入力切替部2を制御する機能を有する。第1の二重積分における第2積分期間に対応したカウント値からなる第1のカウント値と第2の二重積分における第2積分期間に対応したカウント値からなる第2のカウント値とが入力されるディジタル回路7を備える。ディジタル回路7は、第1のカウント値ごとに、第1のカウント値の前後1つずつの第2のカウント値の平均値を第1のカウント値から減算した差分値を求めてディジタル値として出力する機能を有する。

(もっと読む)

アナログ・デジタル変換器

【課題】上位ビットと下位ビットを分けてAD変換を行い、ノイズの影響を受けやすい下位ビットの変換結果の信頼性を、多数決処理を用いて向上させる場合、並列型ADコンバータの基準電圧発生回路としてDAコンバータを搭載する必要があった。

【解決手段】基準電圧発生回路を簡単な抵抗比のみでの構成することにより、下位ビットを変換する並列型ADコンバータの基準電圧発生回路の規模を最小にすることが可能となる。

(もっと読む)

アナログ−デジタル変換回路、照度センサ、近接センサ、測距センサ、携帯電話、およびデジタルカメラ

【課題】微小なアナログ入力電流を高い精度で検出することが出来るアナログ−デジタル変換回路を提供する。

【解決手段】アナログ−デジタル変換回路1は、アナログ入力電流Iinをデジタル変換してデジタル値ADCOUTを得るADC2(アナログ−デジタル変換部)を備えるアナログ−デジタル変換回路であって、所定期間毎に得られた所定個数のデジタル値ADCOUTを記憶するレジスタユニットと、レジスタユニットが記憶しているデジタル値ADCOUTを全て加算することによって加算値ADD[N]を算出する加算器と、加算値ADD[N]と所定の閾値とを比較するとともに、当該比較の結果に従ってデジタル出力信号DOUTを出力する比較回路5とを備える。

(もっと読む)

デジタルアナログ変換回路及び表示ドライバ

【課題】CMOS化するスイッチ数、ゲート幅増加を抑制し、面積増加を抑制可能とする、デジタルアナログ変換器、データドライバ、表示装置を提供。

【解決手段】参照電圧集合体80は第1、第2の参照電圧群81、82を含み、デコーダ100は、mビットのデジタル信号の上位側(m−n)ビットの信号を共通に入力する第1乃至第2のサブデコーダ部10、20と、前記mビットのデジタル信号の下位側nビットの信号を共通に入力する第3乃至第4のサブデコーダ部30、40と、を備え、前記第1及び第3のサブデコーダ部10、30は第1導電型のトランジスタよりなり、前記第2及び第4のサブデコーダ部20、40は第2導電型のトランジスタよりなり、増幅回路50は入力に受けた電圧を、予め定められた重み付けで平均し、前記重み付け平均した電圧、前記mビットのデジタル信号に対応したアナログ信号として出力端子51から出力する。

(もっと読む)

DA変換回路

【課題】ラダー抵抗回路の各抵抗の抵抗値を時間的に平均化できるようして、変換特性の劣化を軽減する。

【解決手段】入力ラインが4ビット、出力ラインが6ビットで、入力ラインをシフトせず又はその並びのままでMSB方向に所定ビット数だけシフトして出力ラインに接続するシフト回路200と、シフト回路200のLSB側の4ビットにバッファ301が接続され、MSB側の2ビットにトライステートバッファ302が接続されたバッファ回路300と、バッファ回路300の出力側に接続されたR−2R型のラダー抵抗回路400と、出力端子600をと有する。シフト回路200は、出力ラインのうちの入力ラインが接続されたラインよりもLSB側のラインを“0”に設定し、且つ出力ラインのうちの入力ラインが接続されたラインよりもMSB側のラインを任意の値に設定する。バッファ回路300は、出力ラインのうちの入力ラインが接続されたラインよりもMSB側のラインに対応するトライステートバッファの出力がハイインピーダンスに設定される。

(もっと読む)

AD変換装置、AD変換方法、及び電子機器

【課題】AD変換の精度を向上させる。

【解決手段】AD変換装置1は、大きさが互いに異なるn(nは2以上の自然数)個の偏移信号δkを生成する偏移信号生成部20と、偏移信号生成部20を制御する偏移信号制御部10と、入力アナログ信号Cinとn個の偏移信号δkとを順次加算してn個の第1信号S1を生成する偏移信号加算部30と、n個の第1信号S1をAD変換してn個の第2信号S2を生成するAD変換部40と、n個の第2信号S1に平均処理を施して出力デジタル信号Coutを生成する信号処理部50とを備える。

(もっと読む)

AD変換装置およびAD変換装置の調整方法

【課題】入出力変換特性の調整に適したノイズ環境下で調整可能なAD変換装置を得る。

【解決手段】入力信号をAD変換した結果である複数のAD変換値をAD変換値保存部9へ格納するAD変換器7と、AD変換値保存部9に格納された複数のAD変換値の平均値を計算し平均値保存部10に格納する平均値演算部18と、AD変換値保存部9に格納された複数のAD変換値の分散を計算し分散保存部11に格納する分散演算部19と、平均値及び分散に基づいてAD変換値の不確かさを判定する不確かさ判定部20と、AD変換値保存部9に格納された複数のAD変換値に正規分布検定を行い、正規性の有無を判定する正規分布検定部17と、不確かさ判定部20において不確かさが所定の許容値より小さいと判定され、且つ正規分布検定部17において正規性を有すると判定された場合に、平均値に基づいてAD変換器7の入出力変換特性の調整を行う調整処理部23とを備える。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

A/D変換器

【課題】相互オフセット較正型A/D変換器において、キャリブレーション終了後には不要となるA/D変換器を有効活用し、A/D変換の精度を高めたA/D変換器を提供する。

【解決手段】2つのA/D変換器を有し、相互にオフセットを較正するA/D変換器では、キャリブレーション終了後においては両者のトランスファーカーブ特性は同じものとなる。そこで、実際のA/D変換の際には、両者のA/D変換器のトランスファーカーブの関係をその分解能の1LSBの半分である0.5LSBずらして両A/D変換器を動作させる。その後、同一時刻にサンプリングした両A/D変換器の出力の和または平均値を出力する。

(もっと読む)

1 - 20 / 112

[ Back to top ]