Fターム[5J022CD01]の内容

アナログ←→デジタル変換 (13,545) | 変換処理系 (818) | 符号変換及び補正処理(試験パターン) (783)

Fターム[5J022CD01]の下位に属するFターム

メモリ (270)

エンコーダ、デコーダ (297)

論理回路(プルアップ・ダウン回路) (114)

特殊量子化器 (24)

関数波形発生 (24)

Fターム[5J022CD01]に分類される特許

1 - 20 / 54

アナログデジタル変換装置

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の差分に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の変化の割合に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

符号変換処理システム

【課題】アナログ信号或はリニア特性のデジタル信号と折線圧縮符号化信号との符号変換を行う符号変換システムに関し、低レベル信号の品質改善を図る。

【解決手段】

アナログ信号或はリニア特性のデジタル信号と折線圧縮符号化信号との符号変換を行う符号変換システムであって、アナログ信号或はリニア特性のデジタル信号の0を中心とした±1の範囲を折線圧縮符号化信号の0を含まない+0.5又は−0.5に対応させるMid−rise形式の基本変換特性を含み、アナログ信号或はリニア特性のデジタル信号の0を含む±0.5以下のレベル範囲を、折線圧縮符号化信号の0或は0を含む複数段階のレベルに変換し、アナログ信号或はリニア特性のデジタル信号の±0.5以下の低レベル信号と折線圧縮符号化信号との間の変換を行って、低レベル信号の伝送品質の向上を図る。

(もっと読む)

受信回路

【課題】

従来のAD変換回路は動作タイミングを適切に制御できないという問題があった。

【解決手段】

入力するアナログ信号とリファレンス電圧との差分を出力する差動アンプと、リファレンス電圧が連続する差動アンプの中間電圧を補間する補間回路と、差動アンプの出力信号および補間回路の出力信号の遅延時間を可変する遅延回路と、遅延回路の出力信号を所定周波数のクロック信号に応じて二値信号に変換する判定回路と、判定回路が出力する二値信号をデジタルデータにエンコードするエンコーダ回路とを有するAD変換回路と、AD変換回路が出力するデジタル信号を等化して受信データを復号する等化復号回路と、AD変換回路の変換タイミングを変化させてAD変換回路または等化復号回路の出力信号を評価し、評価結果が予め設定した範囲内となるAD変換回路の変換タイミングを選択する調整回路とを有する。

(もっと読む)

通信システム、送信装置、及び受信装置

【課題】低コストで高速通信を実現することが出来る通信システム、送信装置、及び受信装置を提供する。

【解決手段】通信システム(1)は、データを送信する送信装置(2)と、前記送信装置から送信されるデータを受信する受信装置(3)と、送信装置と受信装置とを接続する通信路(4)とを備える。送信装置は、比率情報と論理値との組み合わせを少なくとも3パターン以上記憶する論理値テーブル(213)を備える。送信装置は、送信データの論理値に基づいて、論理値テーブルから比率情報を読み出し、読み出した比率情報に基づいて1単位区間内における高電圧区間と低電圧区間との長さの比率を制御する。受信装置は、比率情報と論理値との組み合わせを少なくとも3パターン以上記憶する論理値テーブル(313)を備える。受信装置は、1単位区間内における高電圧区間と低電圧区間との長さの比率を特定し、特定した比率に基づいて論理値テーブルから論理値を読み出す。

(もっと読む)

光送信回路、光受信回路及び光結合型絶縁回路

【課題】光結合部の試験が容易な光送信回路、光受信回路及び光結合型絶縁回路を提供する。

【解決手段】アナログ信号をデジタル信号に変換するアナログデジタル変換回路と、クロックに基づく信号に前記アナログデジタル変換回路の出力を重畳して、平均デューティ比が0よりも大きくかつ1未満に符号化した送信信号を生成する符号化回路と、前記アナログ信号の入力レベルに応じて、前記送信信号または前記アナログ信号を出力する送信制御回路と、前記送信制御回路の出力を光信号に変換して出力する電気光変換素子と、を有する光送信回路と、前記光信号を受信して電気信号に変換する光電気変換回路と、前記光電気変換回路の出力を復号して再生デジタル信号と再生クロックを出力する復号回路と、前記光電気変換回路の出力の平均デューティ比に応じて前記復号回路の出力または前記光電気変換回路の出力を出力する受信制御回路と、を有する光受信回路と、を備えたことを特徴とする光結合型絶縁回路が提供される。

(もっと読む)

アナログ信号変換装置

【課題】データサイズが8ビットに制限される宇宙機において、サーミスタの非線形アナログ信号を精度良く8ビットのデジタル信号に変換することを目的とする。

【解決手段】デジタル処理部220はサーミスタ101から出力された非線形アナログ信号111を信号の強さに応じて16ビットの非線形デジタル信号112に変換する。デジタル処理部220はリニアライズ計算ロジック221を記憶している。リニアライズ計算ロジック221は、16ビット値と、16ビット値に相当する計測温度を線形アナログ信号で表した場合の当該線形アナログ信号の信号の強さに相当する8ビット値とを対応付けている。16/8ビット変換部222は非線形デジタル信号112の16ビット値に対応する8ビット値をリニアライズ計算ロジック221に基づいて特定し、特定した8ビット値を表す線形デジタル信号113を出力する。

(もっと読む)

A/D変換器

【課題】変換エラーの発生状況に応じてチョッパ型コンパレータの待機時間を自動的に調整して、A/D変換精度を向上させ得るA/D変換器を提供する。

【解決手段】複数のチョッパ型コンパレータと、制御信号発生回路と、出力コードを出力するエンコーダとを備えたA/D変換器において、出力コード(D0〜D2)に基づいてチョッパ型コンパレータ1の変換エラーを検出し、当該変換エラーが存在しないとき第一の選択信号SELを生成し、当該変換エラーが存在するとき第二の選択信号SELを生成する出力コード監視回路12と、制御信号発生回路11に備えられ、第一の選択信号SELに基づいて待機時間を段階的に短縮し、第二の選択信号SELに基づいて待機時間を前段階に戻す待機時間調整回路を備えた。

(もっと読む)

データ変換のシステムおよび方法

ディジタル化されたAC信号に対して非線形データ変換を実行するデータ変換システム(100)を提供する。非線形データ変換システム(100)は、ディジタル化されたAC信号を受け取る入力と、非線形変換された信号を出力する出力と、入力および出力に結合された処理システム(104)とを含む。処理システム(104)は、ディジタル化されたAC信号を受け取り、非線形変換された信号を作成するために所定の伝達関数を使用してディジタル化されたAC信号を非線形変換し、非線形変換された信号を出力に転送するように構成される。  (もっと読む)

(もっと読む)

ダウンサンプリング装置

【目的】

a/b倍可変ダウンサンプリングするために生じる、メモリ容量増大と演算器増大、及びそれら必要容量の非決定性を解決する。

【構成】

aがbより小なるaおよびbとしa/b倍ダウンサンプリングをするダウンサンプリング装置に関して、aの値を格納する記憶装置と、bの値を格納する記憶装置と、初期値として0の値を格納する記憶装置と、前記第3の記憶装置の記憶値と前記第1の記憶装置の記憶値を加算する加算器と、前記加算器の出力から前期第2の記憶装置の記憶値を減算する減算器と、前記減算器の出力が0以上であれば1を出力する比較器と、前記比較器の出力が1なら前記減算器の出力を出力し前記比較器の出力が0なら前記加算器の出力を出力するセレクタから成るダウンサンプリング装置とする。

(もっと読む)

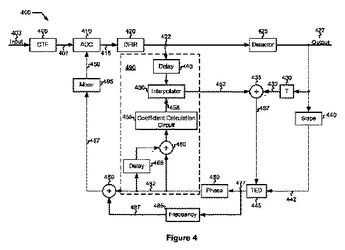

データ検出器フィードバックループにおいて遅延を軽減するためのシステム及び方法

本発明の種々の実施例はデータ検出器フィードバックループにおける遅延を軽減するためのシステム及び方法を提供する。その方法は、デジタルサンプルを生成するために或るサンプリングインスタントにおいてアナログ−デジタル変換を実行するステップ、及び検出出力を生成するためにデジタルサンプルに対してデータ検出を実行するステップを含む。検出された出力は、位相エラーを特定するためにデジタルサンプルに比較される。一時的期間中に、デジタルサンプルは位相エラーを反映して調整デジタルサンプルを生成するために調整される。一時的期間後に、位相エラーを反映するためにサンプリングインスタントが調整される。  (もっと読む)

(もっと読む)

並列型アナログ−ディジタル変換器

【課題】全ビット・グレイコード変換方式と同等のスパークル抑止能力を持ち、配線の錯綜およびパイプラインディレイの増大を防止したADCを実現する。

【解決手段】所定電圧ステップずつ異なる基準電圧Vrefを生成し、基準電圧Vrefとアナログの入力信号Vinとの電圧比較を並列に行ってアナログの入力信号の電圧レベルを検出し、所定ビットNの上位のnビット分の電圧レベルを符号化しグレイコードを出力する第1エンコーダ3−8と、残りの下位ビット分の電圧レベルを符号化し出力する第2エンコーダ3−1〜3−7と、第1エンコーダから出力されるグレイコードをバイナリーコードに変換し、上位nビットADB[5]〜ADB[3]を生成する第1出力回路4と、第1出力回路4から生成されるディジタル信号ADB[3]と、第2エンコーダの出力とを用いて、下位ビットADB[2]〜ADB[0]を生成する第2出力回路5とを有する。

(もっと読む)

信号処理装置

【課題】交流電源の周期数に拘わることなく一定のサンプリング周期で入力信号を取り込んで電源周期数に起因するコモンモードノイズを除去し得る簡易な構成の信号処理装置を提供する。

【解決手段】A/D変換手段においては、演算処理手段に設定された一動作周期内において、第1の入力信号を電源周波数に応じて定められる回数に亘って繰り返しサンプリングすると共に、第2の入力信号を少なくとも1回サンプリングし得る一定の周期で前記第1および第2の入力信号をそれぞれデジタル変換し、平均化処理手段においては前記電源周波数に応じて定められる回数に亘って繰り返しサンプリングされた前記第1の入力信号のデジタル変換値の平均値を求める。

(もっと読む)

A/D変換装置及び方法

【課題】A/D変換器の異常動作、特に電源電圧や参照電圧の異常による異常動作の検出を可能とする。

【解決手段】A/D変換部に供給される電源電圧または参照電圧のどちらか一方を選択し、選択された電圧と電源電圧とで第1のA/D変換を行って第1のA/D変換結果を生成し、選択された電圧と参照電圧とで第2のA/D変換を行って第2のA/D変換結果を生成する。そして、第1と第2のA/D変換結果を比較することにより、電源電圧の異常を検出する。

(もっと読む)

アナログ/デジタル変換方法及びこれを用いた半導体装置

【課題】半導体装置の回路構成を簡単にして回路規模を小さくし、低価格化を図る。

【解決手段】レギュレータ44で生成された安定電圧VREG0を外部へ出力するための出力端子35をLSI30に設け、この出力端子35をユーザが必要に応じてアナログ入力端子34−3に接続する構成にしている。これにより、通常のA/D変換経路と同一の経路で、安定電圧VREGOをA/D変換部43にてA/D変換し、常に一定電圧のA/D変換値AOUT1を容易に得ることができ、アナログ入力端子34−0〜34−2から入力されるアナログ信号AIN0〜AIN2の電圧の絶対値が、補正式を用いてCPU45にて容易に算出可能となる。更に、安定電圧VREGOを通常のA/D変換経路と同一の経路でA/D変換しているので、A/D変換回路40の回路規模を小さくでき、しかも、A/D変換回路周辺の配線も簡略化できる。

(もっと読む)

デジタルキャリブレーション型アナログデジタル変換器及びそれを用いた無線受信回路及び無線送受信回路

【課題】マルチレートのデータを受信する無線チップにおいて、アナログデジタル変換器の消費電力や回路面積が大きくなる。

【解決手段】参照用のアナログデジタル変換ユニットとメインアナログデジタル変換ユニットをともに備えたデジタルキャリブレーション型アナログデジタル変換器において、高サンプルレートの無線受信信号を処理する時は、参照アナログデジタル変換ユニットとメインアナログデジタル変換ユニットを共に動作させて通常のデジタルキャリブレーション型アナログデジタル変換器を構成し、低サンプルレートの無線受信信号を処理する時は、参照アナログデジタル変換ユニットを使用して、アナログデジタル変換を行い、メインアナログデジタル変換ユニットなどは動作を停止させて消費電力を低減することを特徴とする。

(もっと読む)

半導体集積回路

【課題】A/Dコンバータ及びD/Aコンバータをいずれも含んだアナログモジュールを備えた半導体集積回路において、アナログモジュールの検査コストを低減する。

【解決手段】テスト起動端子TSから起動指令が入力されると、テスト制御回路20は、スイッチ16〜19を切り替えることで、テストパターン生成回路15,アナログモジュール(A/Dコンバータ10,D/Aコンバータ11),判定回路14を接続するループバック経路を設定すると共に、テストパターン生成回路15,判定回路14を起動することでテスト動作を実行し、そのテスト動作によって判定回路14から出力される測定結果(アナログモジュールの動作特性の良否)を、テスト結果端子TRを介して出力する。つまり、テスト起動端子TSに起動指令を入力してテスト結果端子TRを監視するだけでアナログモジュールの検査を実施することができる。

(もっと読む)

A/D変換回路、A/D変換方法及び半導体集積回路

【課題】アナログ部の設計期間の長期化を回避し、アナログ部で発生するA/D変換器の非線形性歪を補正することのできるA/D変換回路、A/D変換方法及び半導体集積回路を提供する。

【解決手段】アナログ入力値の変化に追従し、所定のタイミングでアナログ入力値をホールドしてアナログ入力ホールド値を出力するトラックホールド回路(12)と、所定の複数の参照値を生成する参照値生成回路(13)と、前記アナログ入力ホールド値とそれぞれの参照値とを増幅する複数のプリアンプ(14)と、前記それぞれのプリアンプ出力に対応したロジック信号を発生するコンパレータ(15)と、前記コンパレータで発生された前記ロジック信号を所定コードのデジタル出力値に変換するエンコーダ(16)とを備え、前記エンコーダは、前記ロジック信号を前記所定コードに変換する変換ロジックを外部からの補正用データに基づいて変更するA/D変換回路である。

(もっと読む)

オフセット調整回路

【課題】DAコンバータの分解能をADコンバータの分解能よりも低くし、ブリッジ型センサーのオフセットに対してADコンバータの出力を精度よく調整する。

【解決手段】ブリッジ型センサーの出力電圧が印加される差動増幅回路と、前記差動増幅回路の出力電圧を第1デジタル信号に変換するADコンバータと、前記ブリッジ型センサーのオフセットに応じて発生する前記第1デジタル信号を調整するための第2デジタル信号を保持する保持回路と、前記第1デジタル信号及び前記第2デジタル信号を加算する演算回路と、前記ブリッジ型センサーのオフセットに応じて発生する前記差動増幅回路の出力電圧を調整するための第3デジタル信号をアナログ電圧に変換する、前記ADコンバータの分解能より低い分解能のDAコンバータと、を有する。

(もっと読む)

1 - 20 / 54

[ Back to top ]