Fターム[5J022CF07]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | スイッチング回路 (649)

Fターム[5J022CF07]の下位に属するFターム

マルチプレクサ (274)

Fターム[5J022CF07]に分類される特許

1 - 20 / 375

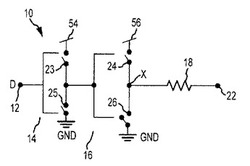

抵抗性デジタル/アナログ変換

【課題】抵抗性構成要素を利用するデジタル/アナログ変換の技術及び方法を提供する。

【解決手段】RDAC回路は、nビットデジタル入力信号から導出されたアナログ出力信号を供給する。RDAC回路は、複数の抵抗性回路分岐10を含み、各抵抗性回路分岐は、プルアップ/プルダウンネットワーク構成に配置する。RDAC回路は、並列に位置決めされた複数の抵抗性回路分岐を含み、複数の抵抗性回路分岐の各々は、第1のインバータ回路14、第2のインバータ回路16、及び抵抗性構成要素18を含む。RDAC回路は、アナログ出力信号を供給する出力ノードを含む。

(もっと読む)

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

半導体集積回路、閾値設定方法、及び通信装置

【課題】複数の比較器に対して両端の閾値を適切な値に設定すると共にその間の閾値を等間隔に設定可能である半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、閾値設定動作により、第1及び第Nの比較器の閾値は、第1及び第Nの比較器による入力電圧と閾値との比較結果に応じて、それぞれ入力電圧の下限値近傍及び上限値近傍に設定され、閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定される。

(もっと読む)

デジタル−アナログ変換器及び半導体集積回路

【課題】デジタル−アナログ変換器の低電圧動作を実現するとともにミラー電流精度を高める。

【解決手段】デジタル−アナログ変換器10は、基準電流を所定のミラー比で複製する第1トランジスタと前記第1トランジスタにカスコード接続される第2トランジスタとを含むミラー回路と、前記第2トランジスタのゲートに接続され、外部からの入力されるデジタル入力信号によってオン・オフ制御されるアナログスイッチとを含む。

(もっと読む)

アナログデジタル回路及びそのアナログデジタル回路を用いた受信機

【課題】アナログ電圧を基準電圧と比較する比較器を有し、その比較器を構成するMOSトランジスタの耐圧をアナログ入力信号の信号振幅の最大電圧より低くすることが可能な逐次変換型アナログデジタル変換器を提供する。

【解決手段】共通ノードに第1端子により接続し、2の巾乗の重み付けがされた複数の第1キャパシタ50a〜50eからなるキャパシタアレイ40と、共通ノードの電圧減衰に寄与する第2キャパシタ70と、それぞれの第1キャパシタに、第1基準電圧、第2基準電圧、又は、入力信号の電圧の内の一つの供給又は切断を行う、複数の第1スイッチからなるスイッチアレイと、共通ノードに第3基準電圧を供給又は切断を行う第2スイッチ30と、共通ノードの電圧を、第3基準電圧と比較する比較器と、第1スイッチ、第2スイッチを制御する制御回路と、を備える。

(もっと読む)

デジタル・アナログ・コンバータ及びデジタル・アナログ変換方法

【課題】パルス変調を用いてデジタル値をアナログ信号に変換する。

【解決手段】デジタル・アナログ・コンバータは、第1及び第2デジタル値D1,D2に応じて第1及び第2パルス変調信号P1,P2を生成する第1及び第2パルス・モジュレータ20,22と、第3デジタル値D3に応じて第3パルス変調信号P3を生成する第3パルス・モジュレータ24と、第3パルス変調信号に応じて第1及び第2パルス変調信号を組み合わせることによってアナログ信号A1を生成するスイッチ/フィルタ回路26を含む。第1及び第2パルス変調信号は、組み合わせる前にローパス・フィルタ処理しても良い。第3デジタル値は、第1及び第2デジタル値の遷移の間、一方向に増加するとしても良く、第3デジタル値は、第1及び第2デジタル値の交互の遷移の間で、夫々反対方向に増加するとしても良い。

(もっと読む)

DA変換回路

【課題】精度の高いDA変換結果を出力する。

【解決手段】入力される2値の論理値に応じて充電され、充電電荷が再分配されることでDA変換結果を第1および第2の容量素子C1、C21(C22)における電圧として得る電荷再分配型のDA変換回路であって、第2の容量素子C21(C22)に電荷として保持されたDA変換結果を出力する増幅器AMPと、第1の容量素子C1の一端と増幅器AMPの入力端とを短絡可能とするスイッチ素子φ4と、第2の容量素子C21(C22)に保持されたDA変換結果を増幅器AMPの入力端に与える前に、スイッチ素子φ4を一時的に短絡するように各部を制御するタイミング信号群を生成するタイミング制御回路CNTと、を備える。

(もっと読む)

増幅装置、増幅システムおよび電流電圧変換装置

【課題】適切にオフセット電圧をキャンセルすることが可能な増幅装置、増幅システムおよびこれを用いた電流電圧変換装置を提供する。

【解決手段】実施形態によれば、増幅装置は、メインアンプと、第1のサブアンプと、第2のサブアンプとを備える。前記メインアンプは、第1の入力電圧と第2の入力電圧との差を増幅した電圧を出力する。前記第1のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。前記第2のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。

(もっと読む)

AD変換器、情報処理装置

【課題】動作速度の低下や回路所要面積の増大を抑えつつノイズ増加を防ぐことのできるAD変換器、情報処理装置を提供する。

【解決手段】各々の一端が互いに接続され、それぞれ所定の比率で重み付けされた容量値を有し、容量値を低減可能な可変容量キャパシタを少なくとも1つ含む複数の重み付けキャパシタを有するAD変換器は、複数の重み付けキャパシタの互いに接続された一端が入力と接続された比較器と、複数の重み付けキャパシタの互いに接続された一端と異なる他端それぞれを、入力信号が入力される入力端子、入力信号の逐次比較に用いる参照電圧源、グランドおよび開放端子のいずれか1つと接続する複数のスイッチとを有する。また、このAD変換器は、重み付けキャパシタに入力信号をサンプリングするとともに、比較電圧を生成して処理を実行する逐次比較制御部と、可変容量キャパシタの容量値を低減させる容量制御部とを有する。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】レイアウト効率の向上や回路特性の向上等を実現できるD/A変換回路、A/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードに接続される第1のD/A変換部DAC1と、出力ノードと第1のノードとの間に設けられる第1の直列キャパシターCS1と、第1のノードに接続される第2のD/A変換部DAC2と、出力ノードと第2のノードとの間に設けられる第2の直列キャパシターCS2と、第2のノードに接続される第1のサブD/A変換部SDAC1と、スイッチ制御を行う制御回路を含む。第2のD/A変換部DAC2の第2のキャパシターアレイ部CAR2と第1のサブD/A変換部SDAC1の第1のサブD/A用キャパシターアレイ部SCAR1とが、第1のD/A変換部DAC1の第1のキャパシターアレイ部CAR1を通る対称軸LXに対して線対称に配置される。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】見かけ上の容量比精度を高めて変換精度を向上できるD/A変換回路、及びこれを含むA/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードNCに接続される第1のD/A変換部DAC1と、出力ノードNCと第1のノードN1との間に設けられる第1の直列キャパシターCS1と、第1のノードN1に接続される第2のD/A変換部DAC2と、制御回路20を含む。第1のD/A変換部DAC1は第1のキャパシターアレイ部CAR1と第1のスイッチアレイ部SAR1を含む。第2のD/A変換部DAC2は第2のキャパシターアレイ部CAR2と第2のスイッチアレイ部SAR2を含む。制御回路20は、入力デジタルデータの各ビットに対するキャパシターの割り当てを動的に変化させるスイッチ制御を第1のD/A変換部DAC1の第1のスイッチアレイ部SAR1に対して行う。

(もっと読む)

半導体集積回路装置

【課題】アナログ・ディジタル変換回路ブロックを備えた半導体集積回路装置において、信頼性の高い断線検出を実現する。

【解決手段】例えば、入力ポートA[k]とアナログ・ディジタル変換回路ADCの入力端子Ainの間に設けられPMOSトランジスタMP1,MP2,MPcおよびNMOSトランジスタMN1,MN2,MNcを含んだT型スイッチ回路TS[k]と、Ainを電源電圧VCCAにプリチャージするPMOSトランジスタMPuを備える。A[k]から信号入力端子Vint[k]までの断線有無を検出する際に、まず、MPuを介してAinをVCCAにプリチャージすると共に、MN2,MP2をオンに、MN1,MP1,MPc,MNcをオフに駆動する。次いで、MPuをオフに制御すると共に、MN1,MN2,MP1,MP2をオンに、MPc,MNcをオフに制御する。

(もっと読む)

D/A変換回路、A/D変換回路及び電子機器

【課題】見かけ上の容量比精度を高めて変換精度を向上できるD/A変換回路、及びこれを含むA/D変換回路、電子機器等の提供。

【解決手段】D/A変換回路は、出力ノードに一端が接続される複数のキャパシターを有するキャパシターアレイ部41と、キャパシターアレイ部41の複数のキャパシターの他端に接続され入力デジタルデータに応じてスイッチ制御される複数のスイッチ素子を有するスイッチアレイ部51と、スイッチアレイ部51のスイッチ制御を行う制御回路20を含む。キャパシターアレイ部41には、第1型キャパシター1Cと、第1型キャパシター1Cとは容量値が異なる第2型キャパシター3Cとが設けられる。制御回路20は、入力デジタルデータの各ビットに対する第1型キャパシター1Cと第2型キャパシター3Cの割り当てを動的に変化させるスイッチ制御をスイッチアレイ部51に対して行う。

(もっと読む)

アナログデジタル変換器

【課題】入力容量が小さく、バッファ回路の消費電力を削減したアナログデジタル変換器を提供する。

【解決手段】本発明の一態様としてのアナログデジタル変換器は、入力端子と、第1コンパレータと、第1出力端子と、第2コンパレータと、第2出力端子とを備える。第1コンパレータは、入力端子で受けた入力信号と第1参照信号を比較して、第1論理信号および制御信号を生成する。第1トランジスタは、入力信号に応じた電流を生成する。第1スイッチおよび第2スイッチは制御信号に応じて互いに短絡および開放が逆になるように切り替えられる。第2トランジスタは、第1スイッチがオンのとき、第2参照信号に応じた電流を、端子に供給する。第3トランジスタは、第2スイッチがオンのとき、第3参照信号に応じた電流を、端子に供給する。出力部は、第1トランジスタで生成された電流を、端子に供給された電流と比較して、第2論理信号を生成する。

(もっと読む)

デジタル/アナログ変換器

【課題】D/Aコンバータの回路面積を削減する。

【解決手段】N個の上側抵抗RHおよびN個の下側抵抗RLはそれぞれ、デジタル入力コードDINの各ビットに対応付けられ、それぞれの抵抗値が対応するビットに応じて実質的にバイナリで重み付けされている。N個の上側スイッチSWHは、それぞれが対応する上側抵抗RHと並列に設けられ、かつそれぞれのオン、オフが対応するビットに応じて制御される。N個の下側スイッチSWLは、それぞれが対応する下側抵抗RLと並列に設けられ、かつそれぞれのオン、オフが対応するビットの論理反転に応じて制御される。

(もっと読む)

サンプルホールド回路及びAD変換器

【課題】アナログ信号に含まれているサンプルホールド動作周期と同じ周期の周期性ノイズや、サンプルホールド動作周期の逓倍の周期の周期性ノイズ等に起因する影響を抑えて信号処理することのできるサンプルホールド回路及びAD変換器を提供する。

【解決手段】入力されたアナログ信号をサンプルホールドするための第1のサンプルホールド回路部23と、第2のサンプルホールド回路部24との2つのサンプルホールド回路部を備えている。第1のパルス信号生成回路部21は、各サンプルホールド動作周期TSHにおいて、任意のタイミングで第1のサンプルホールド回路部23によりアナログ信号AINがサンプルホールドされると共に、その任意のタイミングを変化させて、第1のパルス信号S1を生成する。これにより、サンプルホールド回路20から出力されたアナログ信号ASHに、なるべく周期性ノイズの同じオフセット成分を付加されないようにする。

(もっと読む)

電流検出回路

【課題】離散的範囲で高精度の電流検出が必要な場合に、アナログディジタル変換器のビット数を抑制することである。

【解決手段】電流検出回路10は、大電流範囲の電流検出用に小抵抗値を有する第1抵抗素子12と、小電流範囲の電流検出のための小電流検出部20と、大電流範囲と小電流範囲とで電流パスを切り替える切替部14と、バッファアンプ部30,32と、アナログディジタル変換回路部40、42と、切替部14に切替信号を出力する切替制御回路34とを含んで構成される。小電流検出部20は、小電流範囲の電流検出用に大抵抗値を有する第2抵抗素子28と、バイパストランジスタ26と、第2抵抗素子28の両端子間電圧を閾値電圧である基準電圧22となるように制御する作動増幅器24を含んで構成される。

(もっと読む)

ディジタル/アナログ変換器

【課題】出力の線形性と低消費電力性をバランスよく達成しながら大出力振幅のアナログ信号が生成可能な高速のカレント・ステアリング型のDACを提供する。

【解決手段】DACは、D−FF1D0〜1D5と、スイッチ3D0〜3D5と、電流源11D0〜11D5と、R−2R抵抗ラダー12から構成される。電流源11D0〜11D5は、上位2ビットに対応する電流源11D4,11D5の電流値Iに対して、下位4ビットに対応する電流源11D0〜11D3の電流値が、対応するビットに応じて重み付けされる。R−2R抵抗ラダー12は、出力端子12b,12cがそれぞれのビットに対応するスイッチ3D4,3D5の入力端子に接続され、さらに出力端子12bがアナログ出力端子に接続され、出力端子12cが下位4ビットに対応するスイッチ3D0〜3D3の入力端子に接続される。

(もっと読む)

半導体集積回路およびその検査方法

【課題】半導体集積回路に内蔵されたアナログ/デジタル変換器をテストするためのテスト信号発生器として半導体集積回路に内蔵されたデジタル/アナログ変換器を使用する際に、デジタル/アナログ変換器が正常なデジタル/アナログ変換動作を実行可能であるか否か動作検証することを可能とすること。

【解決手段】半導体集積回路1は、アナログ/デジタル変換器(ADC)5とデジタル/アナログ変換器(DAC)6とを内蔵する。DAC6は、ADC5をテストするためのテスト信号生成器として使用可能とされる。半導体集積回路1は、DAC6の出力端子とADC5の入力端子の間に入力端子と出力端子とが接続されたバッファ増幅器7を更に具備する。バッファ増幅器7の出力端子とADC5の入力端子のいずれか一方は、半導体集積回路1の外部端子(T1、T2)として外部に導出される。

(もっと読む)

1 - 20 / 375

[ Back to top ]