Fターム[5J030CB04]の内容

音質制御、圧縮伸張、振幅制限 (2,281) | 目的、効果 (181) | 回路構成の簡素化 (14)

Fターム[5J030CB04]に分類される特許

1 - 14 / 14

リミッタ回路

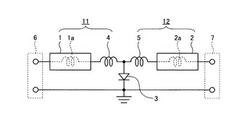

【課題】装置の大型化、伝送周波数における通過損失の上昇を招くことなく、高周波帯域の不要波による影響を抑制可能とするリミッタ回路を得る。

【解決手段】誘導性のマイクロストリップ線路1を含む入力側経路11と、誘導性のマイクロストリップ線路2を含む出力側経路12と、一端が接地され、他端が入力側経路11と出力側経路12との間に接続されたPINダイオード3と、を備え、PINダイオード3がキャパシタ性を有する小信号入力時において、入力側経路11および出力側経路12のインダクタンス値とPINダイオード3のキャパシタンス値とにより、当該リミッタ回路の伝送周波数を遮断周波数以下の通過帯域に含み、且つ、不要波の周波数を通過帯域に含まないローパスフィルタを形成する。

(もっと読む)

振幅制限装置

【課題】電子機器に搭載され、何らかの信号処理の対象となる信号の振幅を既定のしきい値以下に制限する振幅制限装置に関し、構成が複雑化することなく、入力信号の振幅制限を高い精度で安定的に実現できる振幅制限装置を提供する。

【解決手段】しきい値に対する入力信号の瞬時値の超過分を示すパルスの帯域制限によって得られた補正信号を前記入力信号から減じ、前記入力信号の振幅を制限する振幅制限装置であって、前記パルスに先行して前記しきい値に対する前記入力信号の瞬時値の超過分を示す先行パルスを帯域制限し、前記補正信号を予測する予測手段と、前記予測手段によって予測された補正信号の前記パルスの時点における瞬時値と、前記パルスの尖頭値との内、大きい一方を前記補正信号を得る帯域制限の対象とする制御手段とを備える。

(もっと読む)

騒音補正装置

【課題】 演算処理量を削減しつつ広帯域の周波数にわたって騒音補正をすることができる「騒音補正装置」を提供する。

【解決手段】 本発明のオーディオ装置は、オーディオ信号Saを車内の音響空間に出力する出力手段と、音響空間内の音声を入力するマイクロフォン30と、マイクロフォン30から得られた音声信号Sdとオーディオ信号Saを用いて騒音信号を検出し、検出された騒音信号に応じた利得GLを算出する補正パラメータ算出部120と、車速に応じた騒音レベルの利得GLを推定するコントローラ60と、低域のオーディオ信号を算出された利得GLにより補正し、高域のオーディオ信号を推定された利得GHにより補正する信号レベル補正部130とを有する。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

ダイオードリミッタ装置及びレーダ

【課題】調整機構等を精密な部品を用いることなく、低背化できる簡素な構成の、導波管を入出力とするダイオードリミッタ装置を提供する。

【解決手段】導波管下板30は所定深さの溝が形成されたアルミニウム板である。導波管上板31は所定厚さの単純なアルミニウム板である。導波管下板30に形成されている溝と導波管上板31とで囲まれた空間によって導波路及び共振器が構成されている。導波管共振器34と導波管32,36との境界部分には、幅方向を狭めた窓33,35が形成されている。同軸共振器37は、中心導体38とその周囲の部分円柱状の空間とで第2の共振器を構成している。中心導体38の先端と導波管上板31との間には間隙が生じていて、その間隙にPINダイオード41が接続されている。これにより、導波管を入出力とし、途中に同軸共振器37と導波管共振器34が挿入された回路が構成される。

(もっと読む)

リミッタ回路

本発明は、信号入力(E1)と信号出力(A)を有し、出力信号を制限するためのリミッタ回路であって、前記出力信号は、前記信号出力(A)に存在すると共に、前記リミッタ回路の前記信号出力(A)に接続された追加の回路(SCH)に供給され得、バイアス電圧(U)を供給するための電圧接続部(E2)と、トランジスタ(T)とが存在し、前記トランジスタ(T)のゲート接続部(G)は、第1のマッチング回路(A1)を介して前記電圧接続部(E2)に、且つ、第2のマッチング回路(A2)を介して前記信号入力(E1)に接続されているリミッタ回路に関する。  (もっと読む)

(もっと読む)

振幅制限回路及びデジタル処理装置

【課題】後段でサンプリングレートが変換されてもデジタル信号を所望の振幅に制限できる振幅制限回路及びこれを有するデジタル処理装置を提供することを目的とする。

【解決手段】振幅制限回路100は、デジタル信号を所望の振幅値に制限する振幅制限部12と、振幅制限部12の入力側に接続され、デジタル信号のサンプリングレートを変換するサンプリングレート変換部11と、振幅制限部12の出力側に接続され、デジタル信号のサンプリングレートを変換するサンプリングレート変換部13と、を有する。デジタル処理装置301は、振幅制限回路100とデジタル回路200を備える。

(もっと読む)

リミッタ装置

【課題】簡単な回路構成でクリップすることを防止できるリミッタ装置を提供する。

【解決手段】アナログレベル調整器7は、入力端子6に入力されたアナログ信号のレベルを調整する回路であって、CPU2により供給されるデジタル信号に応じてレベルを調整する。リミッタスイッチ5bによりリミッタ機能がオンされた場合は、リミッタ機能がオフされた場合より12dBゲインが低くなるように調整される。このことにより、リミッタ機能がオンの場合に、アナログ信号で、クリップすることを抑制することができる。また、この時、DSP9には、逆に12dBゲインを高くするように制御する。このことにより、デジタルリミッタ9cから出力されるレベルは、リミッタ機能をオン、オフした場合に、変化しないので、リミッタ機能をオンオフした場合に、再度、ゲインを調整する必要がない。

(もっと読む)

リミッタ回路

【課題】 部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現するリミッタ回路を得る。

【解決手段】 入力端子1aからの高周波信号を分岐する結合回路2と、入力側キャパシタ3aと出力側キャパシタ3bとの間に高周波信号線路7を挟んで並列接続された複数のPINダイオード回路6a,6bと、結合回路2の分岐側から入力される高周波信号の信号レベルに応じた直流バイアスを入力側キャパシタ3aと出力側キャパシタ3bとの間に供給する検波回路8とを備えたものである。

一組の結合回路2および検波回路8によって複数のPINダイオード回路6a,6bに直流バイアスを供給するので、部品点数を削減でき、小型化、低価格化、低リーケージ化および低損失化を実現することができる。

(もっと読む)

集積回路

【課題】より高い周波数で動作し、物理的に小さく、また電力制限状態に迅速にセットできる能動制限器を備えた集積回路を提供する。

【解決手段】本発明の集積回路(103)は第1のRFポート(134)と、第2のRFポート(136)と、前記第1のRFポートと第2のRFポートの間に配置された制限器部分(105)と、検出器部分(102)とを具備する。検出器部分(102)は、前記制限器部分に結合され、かつ、前記第1のRFポートと前記第2のRFポートの間のRF信号経路に結合されて、入力信号の電力レベルを検出するように構成されている。

(もっと読む)

スイッチトキャパシタアンプ回路およびこれを用いた固体撮像装置

【課題】

スイッチトキャパシタアンプ回路およびこれを用いた固体撮像装置で任意の利得でログリニア可変する。

【解決手段】

アンプと、第1の時間位相に、入力信号が供給される入力端子と前記アンプの入力端子間に接続される第1の固定キャパシタと第1の可変キャパシタを有するn(nは1以上に整数)個の入力回路と、第2の時間位相に、アンプの出力端子に接続される、第2の固定キャパシタと第2の可変キャパシタを有するm(mは1以上の整数)個の帰還回路とを有し、第1と第2の可変キャパシタの総和を一定とした条件で可変して入出力特性がログリニアで可変するようにした。

(もっと読む)

クランプ回路

【課題】入力信号を特定の基準レベルに固定するクランプ回路のプログラマブル・ゲイン・アンプのゲインの影響を受けることなく、安定したクランプレベルを発生するビデオ信号のクランプ回路を提供する。

【解決手段】 プログラマブル・ゲイン・アンプ1とキャパシタ2が直列接続されて成るビデオ信号増幅回路200のプログラマブル・ゲイン・アンプ1の出力端子にクランプ用アンプ5の負端子が接続され、正端子がクランプ電圧入力端子に接続され、クランプ用アンプ5の出力端子が第1スイッチ4の一方の端子に接続され、他方の端子はプログラマブル・ゲイン・アンプ1の入力端子に接続され、さらに第1スイッチ4の制御端子が制御信号入力端子に接続されて構成される。

(もっと読む)

クランプ回路装置

【課題】 より少ない素子数で簡単に構成することができるクランプ回路装置を提供する。

【解決手段】 FET1,抵抗素子2,FET3の直列回路によって基準電圧V1,V2を設定し、それらの基準電圧とバンドギャップリファレンス回路6により生成した基準電圧V2とを加算回路4,減算回路9により夫々加算,減算してFET7,11のゲート電位V4,V5を設定し、電源にドレインを接続したFET7のソースと、グランドにドレインを接続したFET11のソースとを、制御IC部8の入力端子に共通に接続してクランプ回路装置12を構成する。そして、入力端子に正極性の過電圧が印加された場合には電圧を(V4+Vtp)にクランプし、負極性の過電圧が印加された場合には電圧を(V5−Vtn)にクランプする。

(もっと読む)

リミッタ回路

【課題】 回路規模が小さく、クリップ精度が高く、しかも、大きな容量のコンデンサを必要としないリミッタ回路を提供する。

【解決手段】 制御端子30にクリップ電圧として例えば+2Vを加えると、この電圧+2VはFET28のソースに加えられると共に、オペアンプ31の−入力端へ加えられ、オペアンプ31から電圧−2Vが出力され、FET23のソースへ加えられる。この状態において、入力端子21の入力信号が−2V〜+2Vの範囲にある場合は、FET25、26が共にオフとなり、回路が入力信号に影響を与えることはない。入力信号が+2V以上になると、FET26のソース電圧がゲート電圧より高くなり、FET26がオン状態となり、入力信号が+2Vでクリップされる。また、入力信号が−2V以下になると、FET25のソース電圧がゲート電圧より低くなり、FET25がオン状態となり、入力信号が−2Vでクリップされる。

(もっと読む)

1 - 14 / 14

[ Back to top ]