Fターム[5J039DA14]の内容

Fターム[5J039DA14]に分類される特許

1 - 20 / 26

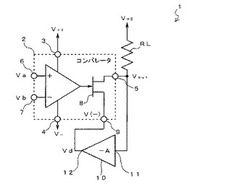

コンパレータ回路

【課題】ローレベル出力電圧を0V、あるいは所望の電圧に精度よく設定でき、温度変化やプルアップ抵抗の抵抗値の変化によるローレベル出力電圧の変動が小さいコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続され、他端が正電源V+2に電気的に接続されるプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がコンパレータ2の出力段トランジスタ8のソース端子またはエミッタ端子に電気的に接続された反転増幅器10と、を備えたものである。

(もっと読む)

インターフェイス回路

【課題】ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現する。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

(もっと読む)

シュミットトリガ回路

【課題】安定なヒステリシス特性を有するシュミットトリガ回路を提供する。

【解決手段】実施形態のシュミットトリガ回路は、PMOSトランジスタP1、P2とNMOSトランジスタN1、N2が直列に接続されたインバータIV1と、PMOSトランジスタP1に並列に接続されたPMOSトランジスタP3と、NMOSトランジスタN1に並列に接続されたNMOSトランジスタN3と、出力信号Zの反転信号DをPMOSトランジスタP3およびNMOSトランジスタN3のゲート端子へ印加するインバータIV2と、を有し、入力信号Aを反転させた信号BをPMOSトランジスタP1およびNMOSトランジスタN2のゲート端子へ印加する高閾値論理回路1と、入力信号Aを反転させた信号CをNMOSトランジスタN1およびPMOSトランジスタP2のゲート端子へ印加する低閾値論理回路2と、を備える。

(もっと読む)

シュミット回路

【課題】ノイズの伝搬をより抑制することが可能なシュミット回路を提供する。

【解決手段】シュミット回路100は、入力信号が入力され、しきい値電圧を可変可能な入力論理回路と、前記入力論理回路の出力信号が入力され、第1のしきい値電圧を有する第1の論理回路C1と、前記入力論理回路の出力信号が入力され、前記第1のしきい値電圧より小さい電圧である第2のしきい値電圧を有する第2の論理回路C2と、前記第1の論理回路C1の出力信号及び前記第2の論理回路C2の出力信号に応じて、前記入力論理回路のしきい値電圧を調整する可変抵抗回路R1、R2と、前記入力信号の電位が前記第1のしきい値電圧と前記第2のしきい値電圧との間の場合はフローティングされたフローティング電位を出力し、前記入力信号の電位が前記第1のしきい値電圧以上若しくは前記第2のしきい値電圧以下の場合は固定電位を出力する第3の論理回路C3と、を備える。

(もっと読む)

コンパレータ回路およびモータ駆動回路

【課題】 コンパレータ回路から、高耐圧特性を必要とするコンデンサを削減する。

【解決手段】 一端が共通に接続されたコンデンサC1〜C3と、C1に電圧VrefまたはVinの何れか一方を順次印加する第1スイッチ回路と、入力端がC1〜C3の接続点に接続されたインバータと、C1にVrefが印加される第1期間に、インバータの入力端と出力端とを接続する第2スイッチ回路と、第1期間の次に、C1にVinが印加される第2期間には、インバータの出力レベルを出力し、第1期間には、第2期間の最後におけるインバータの出力レベルを保持して出力する第1ラッチ回路と、第1期間には、C3にLレベルの電圧を印加するとともに、C2にHレベルの電圧を印加し、第2期間には、C3にHレベルの電圧を印加するとともに、C2にLまたはHレベルの電圧を印加する制御回路と、を有する。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、しきい値電圧を決定する参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、前記基準電圧を基準とした、検出すべき電圧を入力する第4の端子と、前記第1、第2の端子を制御端子に接続され、前記参照電圧の電位差に応じた電流をそれぞれ流す、第1導電型の第1、第2のトランジスタと、前記第1のトランジスタと前記第4の端子との間に接続される第2導電型の第3のトランジスタと、前記第2のトランジスタと前記第3の端子との間に接続され、前記第3のトランジスタの流す電流に応じたミラー電流を流す第2導電型の第4のトランジスタと、を有し、前記第2、第4のトランジスタの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

コンパレータ回路

【課題】短い判定時間を実現して高速化を図り、また高感度化も同時に実現する。

【解決手段】ノードN1,N2の間に2個のインバータを逆並列接続した正帰還部1と、正帰還部1への電源供給を行う電源用トランジスタMP3,MN3と、ノードN1,N2を正電源端子VDDに個々に接続するリセット用トランジスタMP4,MP5と、入力電圧に比例して内部抵抗を減少させる入力用トランジスタMN6,MN7と、入力用トランジスタMN6,MN7をノードN1,N2と接地GNDとの間に個々に接続する判定用トランジスタMN4,MN5と、ノードN1,N2に入力側がそれぞれ接続されたインバータINV1,INV2とを備える。

(もっと読む)

ヒステリシスコンパレータ回路及びそれを用いた遅延回路

【課題】回路規模を大型化することなく、大きな遅延時間を得る。

【解決手段】遅延対象の矩形波の入力信号Vinを台形波発生回路10により台形波信号Vcに変換し、その台形波信号の中間電圧よりも高く設定された第1のスレッショルド電圧Th1を有するインバータ21と、中間電圧よりも低く設定された第2のスレッショルド電圧Th2を有するインバータ22とで、台形波信号Vcと第1及び第2のスレッショルド電圧を比較し、インバータ21とインバータ22の出力でバッファ回路23を駆動し、台形波信号Vcに同期して反転し、かつ遅延した矩形波の出力信号Voutを生成する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

逆ヒステリシス回路

【課題】入力信号の周波数に変化が生じた場合であれ、確実に動作することの逆ヒステリシス回路を提供する。

【解決手段】逆ヒステリシス回路1は、第1インバータ10の出力信号である第1出力信号OUT1の電圧レベル及び第2インバータ20の出力信号である第2出力信号OUT2の電圧レベルの双方に基づいて、逆ヒステリシス回路1としての入力端子に入力される入力信号の立ち上がり時における閾値電圧レベルを第1閾値電圧レベルとし、入力信号の立ち下がり時における閾値電圧レベルを第2閾値電圧レベルとする出力信号を生成する出力信号生成部を備える。出力信号生成部30は、第1出力信号OUT1の電圧レベルに応じて動作する第1フリップフロップ32と、第2出力信号OUT2の電圧レベルに応じて動作する第2フリップフロップ35とを含んで構成されている。

(もっと読む)

比較器及びこれを用いたアナログ−デジタル変換器

【課題】トランジスタのON抵抗または寄生容量による動作スピードの低下を防止可能な比較器を提供する。

【解決手段】正相入力信号と逆相基準信号との電圧に応じて抵抗値が変化する正相の可変抵抗部130と;逆相入力信号と正相基準信号との電圧に応じて抵抗値が変化する第2の可変抵抗部140と;クロック信号が第1レベルであれば第1及び第2のインバータの出力電位を第1または第2電源端子の電位にリセットする第1及び第2のスイッチと;第1レベルと第2レベル間を遷移するクロック信号を1つのゲート端子で受ける第1FinFETを含み、正相出力信号を反転させて逆相出力信号を出力する第1のインバータ110と;クロック信号を1つのゲート端子で受ける第1FinFETと同じ極性の第2FinFETを含み、逆相出力信号を反転させて正相出力信号を出力する第2のインバータ120と;を具備する。

(もっと読む)

入力回路

【課題】入力レベルに対してヒステリシス特性を持たせる。

【解決手段】第1トランジスタM1は、ソースが接地端子P2に接続され、ゲートに入力デジタル信号S1が入力される。第2トランジスタM2は、ソースが電源端子P1に接続され、そのドレインが第1トランジスタM1のドレインに接続される。第2トランジスタM2はデプレッション型で構成する。第1インバータ12は、第1トランジスタM1、第2トランジスタM2の接続点P3、すなわちドレイン電位Vxを反転し、第2トランジスタM2のゲートに出力する。入力回路10は、接続点P3のドレイン電位Vxに応じたレベルを出力する。

(もっと読む)

インバータアンプ

【課題】パワーダウン時のリーク電流が抑制されるインバータアンプの提供。

【解決手段】入力端子とバイアス供給回路との間にパワーダウン時リーク電流抑制用トランジスタを設ける。

(もっと読む)

シュミットトリガ回路及びそれを具備する半導体集積回路

【課題】無駄な電流を減少させると共に入出力特性のヒステリシス幅の調整範囲を広くすることが可能なシュミットトリガ回路を提供する。

【解決手段】このシュミットトリガ回路1は、入力信号を反転して出力する第1のインバータ2と、第1のインバータ2の出力信号を反転して出力する第2のインバータ3と、入力信号及び第2のインバータ3の出力信号に基づいて、第1のインバータ2の出力ノードと高電位側の電源電位との間及び/又は第1のインバータ2の出力ノードと低電位側の電源電位との間のインピーダンスを調整するインピーダンス調整回路4とを具備する。

(もっと読む)

信号増幅器

【課題】高速動作を可能とし、素子ばらつきに依存しない高信頼性動作を可能としている増幅器の提供。

【解決手段】一方の入力が他方の出力に接続され一方の出力が他方の入力に接続されることでフリップフロップを構成する第1及び第2のインバータを含み、インバータを構成する第1及び第2のトランジスタ対(MP1、MN1及びMP2、MN2)のうち、各一方のトランジスタ(MN1、MN2)の制御端子は、第1及び第2の容量(C1、C2)を介して第1及び第2のインバータの入力(1、2)にそれぞれ接続され、リセット時には、第1及び第2のインバータの互いの入力と出力(OUT、OUTB)を非接続とした状態で第1及び第2のインバータの入力には基準信号(VR)が共通に供給され、各一方のトランジスタはダイオード接続され、第1及び第2の容量には基準信号(VR)と各一方のトランジスタの制御端子との電圧差が蓄積される。

(もっと読む)

浮遊抵抗体ラダーを用いたインバータベースのフラッシュA/D変換器

【課題】低消費電力などのインバータベースのフラッシュADCの特徴を保有する一方、インバータのサイズまたはパラメータを変えないでインバータ不整合を指示するフラッシュADCを持つことが望まれる。

【解決手段】アナログ信号をデジタル信号に変換するA/D変換器であり、複数の比較器を含む比較器アレーと、直列に接続された複数の抵抗を含む抵抗列と、抵抗列に流れる一定の電流を与えるための電流発生器とを備え、前記比較器の各々は第1のインバータおよび第1のインバータと直列に接続された第2のインバータを含み、前記抵抗器の各々は複数の比較器の1つに対応することを特徴とする。

(もっと読む)

コンパレータ回路

【課題】閾値電圧(基準電圧)のバラツキや変動が抑えられたコンパレータ回路を提供する。

【解決手段】コンパレータ回路10は、NMOSトランジスタQ1とPMOSトランジスタQ2とを含み、両トランジスタQ1,Q2のゲート同士が接続されて入力端子12とされ、両トランジスタQ1,Q2のドレイン同士が接続されて出力端子13とされるCMOSインバータ回路11を備える。NMOSトランジスタQ1のソースと低位電源VSSとの間に、ダイオード接続されたPMOSトランジスタQ4が接続される。PMOSトランジスタQ2のソースと高位電源VDDとの間に、ダイオード接続されたNMOSトランジスタQ3が接続される。

(もっと読む)

容量結合を利用したCMOSの時系列型AD変換回路及びDA変換回路

【課題】容量結合回路を利用して少ない素子数で論理回路,AD変換回路等を提供する。

【解決手段】アナログ入力が与えられる入力端子と、2値の出力が与えられるN(Nは複数)ビットの出力端子とを有するアナログ・デジタル変換回路において、一方の電極が入力端子に接続される入力容量と、入力容量の他方の電極が入力される第一のインバータと、該第一のインバータに接続される第二のインバータとを有する単位回路が、N個並列に設けられ、その単位回路の第二のインバータの出力がそれぞれの出力端子に与えられ、更に、各単位回路に対応する出力の反転出力が、それぞれ下位ビットに対応する単位回路の前記第一のインバータの入力に帰還容量を介して帰還され、最上位ビットからM(Mは整数)番目の単位回路の反転出力に対応する前記帰還容量の容量値は、帰還される単位回路の入力容量の1/2M 倍であることを特徴とするアナログ・デジタル変換回路。

(もっと読む)

電圧比較回路およびその閾値電圧補正方法

【課題】 CMOSインバータは製造ばらつきによって閾値電圧が大きく変動するため、レーザートリミングにより閾値電圧の変動を抑えていたが、特殊なプロセスが必要で製造工程が煩雑になっていた。

【解決手段】 CMOSインバータ1と、基準電圧発生手段5と、外部入力信号と基準電圧とを切り換える入力信号切換スイッチ6と、CMOSインバータ1の一方と並列に接続され、各オン・オフ切換スイッチ4(n−1)によりオン・オフが切り換えられる補正用トランジスタ群3と、オン・オフ切換スイッチを制御する補正スイッチング制御手段7とを備えた電圧比較回路であって、補正スイッチング制御手段は、基準電圧がCMOSインバータへ接続されているときに、CMOSインバータの出力信号に応じて、基準電圧とCMOSインバータの閾値電圧とを逐次比較する逐次比較部と、該比較結果に基づきオン・オフ切換スイッチの切換を行う切換補正部とを有する。

(もっと読む)

1 - 20 / 26

[ Back to top ]