Fターム[5J039DB08]の内容

Fターム[5J039DB08]の下位に属するFターム

ヒステリシス幅が可変のもの (17)

特殊なヒステリシス(逆特性、時間変化) (5)

Fターム[5J039DB08]に分類される特許

1 - 20 / 45

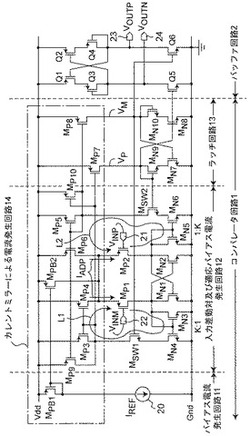

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

シュミットトリガ回路

【課題】安定なヒステリシス特性を有するシュミットトリガ回路を提供する。

【解決手段】実施形態のシュミットトリガ回路は、PMOSトランジスタP1、P2とNMOSトランジスタN1、N2が直列に接続されたインバータIV1と、PMOSトランジスタP1に並列に接続されたPMOSトランジスタP3と、NMOSトランジスタN1に並列に接続されたNMOSトランジスタN3と、出力信号Zの反転信号DをPMOSトランジスタP3およびNMOSトランジスタN3のゲート端子へ印加するインバータIV2と、を有し、入力信号Aを反転させた信号BをPMOSトランジスタP1およびNMOSトランジスタN2のゲート端子へ印加する高閾値論理回路1と、入力信号Aを反転させた信号CをNMOSトランジスタN1およびPMOSトランジスタP2のゲート端子へ印加する低閾値論理回路2と、を備える。

(もっと読む)

コンパレータ

【課題】安定したヒステリシス特性を有するコンパレータを提供する。

【解決手段】コンパレータ1は、一対の差動入力トランジスタT1,T2を有する差動回路部10と、差動回路部10にヒステリシスを付加するためのセレクタ回路部20と、レベル変換増幅部30とを備える。セレクタ回路部20は、差動入力トランジスタT1,T2のドレインにそれぞれ接続するトランジスタT3,T4を有し、トランジスタT3,T4の一方がオンするときオンしたトランジスタに接続する側のトランジスタT1,T2から一定のバイアス電流Ibを吸引するように接続される。レベル変換増幅部30の2つの増幅回路31,32は、セレクタ回路部20のトランジスタT3,T4に対して並列に接続されており、差動回路部10の出力に応じてトランジスタT3,T4の一方をオンし同時に他方をオフすることでバイアス電流Ibを切り換える。

(もっと読む)

半導体集積装置における遅延回路及びインバータ

【課題】静電気放電に対する耐性が強く且つ低消費電力にて、遅延時間のバラツキを抑えることが可能な遅延回路及びインバータを提供する。

【解決手段】遅延回路のインバータとして、低電位部は、夫々のソース端子及びドレイン端子が第1共通接続点にて接続されている一対のFETを有し、高電位部は、夫々のソース端子及びドレイン端子が第2共通接続点にて接続されている一対のFETを有する。インバータ出力L2が高電位状態となった場合には、上記第1共通接続点に電源電位VDDを印加する一方、低電位状態となった場合には、上記第2共通接続点に接地電位GNDを印加することによりヒステリシス特性を持たせる。更に、製造上のバラツキ又は環境温度の変化に伴う遅延時間の変動を抑制させるべく、上記した電源電位VDD又は接地電位GNDの供給元となり、かつ常時オン状態のFETを設ける。

(もっと読む)

コンパレータ及び半導体装置

【課題】動作モードに応じた短い応答時間及び低消費電力と、レイアウト面積の削減とを実現するコンパレータを提供する。

【解決手段】コンパレータは、第1の動作モードに対応した第1の電圧と、第2の動作モードに対応した第1の電圧より低い第2の電圧とのいずれか一方を基準電圧として選択される動作モードに応じて出力する基準電圧生成回路と、第1の動作モードに対応した第1の定電流と、第2の動作モードに対応した第1の定電流より低い第2の定電流とのいずれか一方を選択される動作モードに応じて供給する定電流回路と、定電流回路により電流が供給され、外部から入力される電圧と基準電圧生成回路が出力する基準電圧とを比較した比較結果を出力する差動増幅回路とを備え、差動増幅回路が出力する比較結果に応じて、第1及び第2の動作モードのいずれか一方が動作モードに選択される。

(もっと読む)

マイクロコンピュータ、ヒステリシスコンパレータ回路、及び電圧監視装置

【課題】被監視電圧を効率的に監視でき、かつ、自由度の高いコンパレータを備えたマイクロコンピュータを提供する。

【解決手段】被監視電圧を第1の基準電圧と比較する第1のコンパレータと、被監視電圧を第2の基準電圧と比較する第2のコンパレータと、第1のコンパレータと第2のコンパレータによって並行して被監視電圧を監視し、あらかじめ設定した条件に達したときに割込み信号を発生する割込み制御回路と、を備える。さらに、第1、第2の基準電圧を設定するD/Aコンバータや第1、第2のコンパレータによってセット、リセットされるフリップフロップ回路を設け、フリップフロップ回路により割込みを発生させてもよい。

(もっと読む)

電圧比較回路

【課題】入力電圧の変化を高精度に検出できる電圧比較回路を実現する。

【解決手段】比較器の出力電圧に応じて所定のヒステリシス電圧幅を持たせて比較器の比較電圧を変化させる電圧比較回路において、一端が比較器の出力端子に接続され、他端に基準電圧に応じた電圧が印加され、比較器の出力電圧に応じてオンまたはオフするダイオードを備え、このダイオードがオフしている時は、基準電圧が比較器の比較電圧となる。

(もっと読む)

ヒステリシスコンパレータ

【課題】簡単な回路構成で、広範囲で高精度かつ低いヒステリシス特性を持たせることができるヒステリシスコンパレータを提供する。

【解決手段】ヒステリシスコンパレータ1において、差動対30の一方に定電流源2の負荷抵抗22と比精度が保たれている抵抗23が設けられているコンパレータ回路3、4の出力をRSラッチ5のリセット、セット入力とし、入力信号Vina、Vinbをコンパレータ回路3、4へ入力する際は互いに逆になるように入力する。

(もっと読む)

ヒステリシスを備えた比較器

振幅ヒステリシスを組み込む比較器を提供するための技術である。典型的な実施形態では、電流オフセット段は、フォールドカスコード構造を有する比較器につながれる。電流オフセット段は、振幅ヒステリシスをインプリメントする比較器出力の交換を遅らせるために、入力段から生成された電流をオフセットする。典型的な実施形態では、レール間入力電圧は、2重のNMOSおよびPMOS入力段の提供により適応されてもよい。別の典型的な実施形態では、振幅ヒステリシスは、調整可能なしきい電圧によって制御されてもよい。さらに別の典型的な実施形態では、一定のトランスコンダクタンスgmバイアス回路は、入力同相電圧および/または他の変化にわたるしきい電圧の安定性を維持するために提供されてもよい。 (もっと読む)

信号レベル検出回路

【課題】増幅回路の動作に必要な電流値を増加させることなく、ヒステリシスを用いて耐ノイズ特性を向上させることができる信号レベル検出回路を提供すること。

【解決手段】増幅回路6aの電圧利得は、増幅回路6bの電圧利得より大きく、切替装置6cは、ピークホールド回路7aに増幅回路6aの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6aの出力信号から増幅回路6bの出力信号に切り替え、ピークホールド回路7aに増幅回路6bの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6bの出力信号から増幅回路6aの出力信号に切り替える。

(もっと読む)

パワーオンリセット回路およびパワーオンリセット信号の生成方法

【課題】容易に計算でき、出力精度を高め得るとともに,初期化させる必要な半導体集積回路及び種種の応用に対して高精度且つ有効なリセット信号を提供する。

【解決手段】電源電圧が一定のクランプ電圧レベルを超えると電源電圧の上昇に従って電圧が上昇するチャージクランプ回路と、電源電圧の上昇に基づき一定比率で電圧が上昇する分圧回路と、該チャージクランプ回路の出力と該分圧回路の出力を比較してチャージクランプ回路の出力電圧が上回った場合にリセット信号を出力するコンパレータ回路からなり、さらに、該比較回路の出力から出されるリセット信号を保持するヒステリシス回路を有するパワーオンリセット回路を提供する。

(もっと読む)

コンパレータ回路

【課題】ヒステリシス特性を持たせるための抵抗を短絡/開放するスイッチのオン抵抗変動による差動利得を削減する。

【解決手段】第1段の差動回路は、電源とアースの間に存する、直列接続されたR5およびTR7と、直列接続されたR6およびTR8と、その共通エミッタ接続点に接続された定電流源Ir9で構成される。第2段のエミッタフォロワ回路は、電源とアースの間に存する、直列接続されたTR10,R12および定電流源Ir16と、直列接続されたTR11,R18および定電流源Ir17で構成されて差動出力信号を出力する。SW13,SW14はR12の両端にそれぞれの一端が接続され、他端は次段回路の入力側に接続され、差動出力信号に基づいて排他的にオン/オフする。

(もっと読む)

ヒステリシスコンパレータ

【課題】回路規模を大幅に縮小することが可能なヒステリシスコンパレータを提供する。

【解決手段】強誘電体キャパシタCsと、入力電圧Vinが入力され、強誘電体キャパシタCsに出力する入力端子T1と、強誘電体キャパシタCsに直列接続されたリファレンスキャパシタCoと、強誘電体キャパシタCsとリファレンスキャパシタCoとの接続点に制御端子Tgが接続され、出力電圧Voutを出力するスイッチング回路SW1とを備えている。

(もっと読む)

コンパレータ回路及びそれを有するアナログデジタルコンバータ

【課題】判定時間を短くしたコンパレータ回路と,それを有するADCを提供する。

【解決手段】コンパレータ回路は,入力信号が判定値より大きいか小さいかを示す判定信号を出力する。そして,コンパレータ回路は,入力信号と第1の比較値とを比較し判定結果を有する第1の判定信号を生成する第1のコンパレータと,入力信号と,第1の比較値と異なる第2の比較値とを比較し判定結果を有する第2の判定信号を生成する第2のコンパレータと,第1及び第2の判定信号のうちいずれが先に生成されたかを検出し,先に生成された信号を選択して判定信号として出力する出力選択回路とを有する。

(もっと読む)

センサ回路

【課題】センサ回路が正常に動作している状態において2つのコンパレータの出力信号が異なる値をとることを抑制することが可能なセンサ回路を提供する。

【解決手段】ストップランプスイッチの信号処理回路8は、磁気センサ4,5からブレーキペダルの踏み込み操作に伴うプランジャピンの移動量に応じた値の入力信号Vin1,Vin2がそれぞれ入力される第1及び第2コンパレータ11,12を備えている。信号処理回路8には、一方のコンパレータ12,11の出力信号Vout2,Vout1の値が反転準すると、このときの他方のコンパレータ11,12の出力信号Vout1,Vout2の値も反転するように該他方のコンパレータ11,12の基準信号Vref1,Vref2の値を予め設定された値に変更する第1及び第2基準信号変更回路13,14が設けられている。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力電圧の閾値の変動があっても、ヒステリシス電圧が変化せず、温度特性の影響を受けないヒステリシスコンパレータを提供する。

【解決手段】入力端子INとグランドとの間に接続された抵抗2,3は、入力電圧Vinに対応する電圧を発生し、コンパレータ1の入力端子に与える。コンパレータ1が“H”を出力しているとき、抵抗8にはPMOS6のドレイン電流が流れる。PMOS6のドレイン電流に相当するPMOS4のドレイン電流が抵抗2及び抵抗3の接続点に与えられることにより、ヒステリシス電圧が設定される。温度が変化して抵抗2,3,8の抵抗値が変化しても、PMOS4のドレイン電流が抵抗2及び抵抗3の接続点に与えられることにより設定されるヒステリシス電圧の値は、変化しない。

(もっと読む)

半導体装置

【課題】コストの増加を抑制しつつ、高いチューニング精度を維持するとともに、チューニングに要する時間の増加を抑制できる半導体装置を提供する。

【解決手段】レベルシフト回路5を構成する可変抵抗R1およびR2に加えて、BGR回路1のVBGR電圧の出力ノードと可変抵抗R1との間に接続された付加抵抗RUと、可変抵抗R2と基準電圧との間に接続された付加抵抗RDとを有し、付加抵抗RUおよびRDのそれぞれに並列して、Nチャネル型のMOSトランジスタTUおよびTDが接続されている。

(もっと読む)

ヒステリシスコンパレータ回路

【課題】回路規模をより縮小することが可能なヒステリシスコンパレータ回路を提供する。

【解決手段】ヒステリシスコンパレータ回路100は、定電流源と、定電流による電圧降下に応じた出力電圧を出力する可変抵抗回路と、入力端子に反転入力端子が接続され、定電流源と可変抵抗回路との間の第1の接点に非反転入力端子が接続され、反転入力端子に入力された入力信号と非反転入力端子に入力された第1の接点の基準電圧とを比較し、この比較結果に応じた電圧を出力するコンパレータと、スイッチ回路と、を備える。スイッチ回路は、コンパレータの非反転出力が“Low”レベルの場合は、可変抵抗回路の抵抗値を第1の抵抗値に切り換え、コンパレータの非反転出力が“High”レベルの場合は、可変抵抗回路の抵抗値を第1の抵抗値よりも小さい第2の抵抗値に切り換える。

(もっと読む)

1 - 20 / 45

[ Back to top ]