Fターム[5J039DB09]の内容

Fターム[5J039DB09]に分類される特許

1 - 17 / 17

ヒステリシスコンパレータ

【課題】入力信号に重畳されたノイズの振幅が予め想定できない場合でも適切な出力信号を得る。

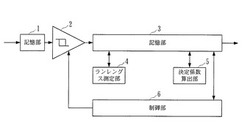

【解決手段】ヒステリシスコンパレータは、入力信号をしきい値TH1,TH2に基づいて2値化することを、ヒステリシス幅W=TH1−TH2を変更しながら行う2値化部2、2値化信号のランレングスをヒステリシス幅Wが同じ2値化信号の信号列毎に測定するランレングス測定部4、ランレングス測定部4の測定結果から得られるランレングス度数分布に対して度数の対数変換を、ヒステリシス幅Wが同じ2値化信号の信号列毎に行い、対数変換後のランレングス度数分布を最小二乗法により1次関数で近似したときの決定係数を、ヒステリシス幅Wが同じ2値化信号の信号列毎に算出する決定係数算出部5、決定係数が最小になるヒステリシス幅Wによる2値化信号を、最適な2値化結果として出力する制御部6を備える。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号のひずみが想定もしくは調整できない場合でも適切な出力信号を得る。

【解決手段】ヒステリシスコンパレータは、入力信号をしきい値TH1,TH2に基づいて2値化することを、しきい値TH1,TH2の中心値を変更しながら行う2値化部2、2値化信号のランレングスを2値化処理時のしきい値が同じ2値化信号の信号列毎に測定するランレングス測定部4、ランレングス測定部4の測定結果からランレングスの分布の特徴値を、2値化処理時のしきい値が同じ2値化信号の信号列毎に算出する特徴値算出部5、2値化信号の立ち上がりから次の立ち下がりまでのランレングスの特徴値と2値化信号の立ち下がりから次の立ち上がりまでのランレングスの特徴値とが最も近くなるしきい値TH1,TH2による2値化信号を、最適なしきい値TH1,TH2による2値化結果として出力する制御部6を備える。

(もっと読む)

シュミット回路

【課題】ノイズの伝搬をより抑制することが可能なシュミット回路を提供する。

【解決手段】シュミット回路100は、入力信号が入力され、しきい値電圧を可変可能な入力論理回路と、前記入力論理回路の出力信号が入力され、第1のしきい値電圧を有する第1の論理回路C1と、前記入力論理回路の出力信号が入力され、前記第1のしきい値電圧より小さい電圧である第2のしきい値電圧を有する第2の論理回路C2と、前記第1の論理回路C1の出力信号及び前記第2の論理回路C2の出力信号に応じて、前記入力論理回路のしきい値電圧を調整する可変抵抗回路R1、R2と、前記入力信号の電位が前記第1のしきい値電圧と前記第2のしきい値電圧との間の場合はフローティングされたフローティング電位を出力し、前記入力信号の電位が前記第1のしきい値電圧以上若しくは前記第2のしきい値電圧以下の場合は固定電位を出力する第3の論理回路C3と、を備える。

(もっと読む)

ヒステリシスコンパレータ

【課題】ヒステリシスコンパレータの閾値の設定範囲を広げる。

【解決手段】一つの実施形態のヒステリシスコンパレータには、電流源2乃至4、比較増幅部10、基準電圧発生部21、カレントミラー回路23、Nch MOSトランジスタNMT3、Nch MOSトランジスタNMT4、Nch MOSトランジスタNMT6、Nch MOSトランジスタNMT8、Nch MOSトランジスタNMT9、端子Pvd、端子Pv1、端子Pin、端子Pvs、及び端子Poutが設けられる。

(もっと読む)

コンパレータ回路およびモータ駆動回路

【課題】 コンパレータ回路から、高耐圧特性を必要とするコンデンサを削減する。

【解決手段】 一端が共通に接続されたコンデンサC1〜C3と、C1に電圧VrefまたはVinの何れか一方を順次印加する第1スイッチ回路と、入力端がC1〜C3の接続点に接続されたインバータと、C1にVrefが印加される第1期間に、インバータの入力端と出力端とを接続する第2スイッチ回路と、第1期間の次に、C1にVinが印加される第2期間には、インバータの出力レベルを出力し、第1期間には、第2期間の最後におけるインバータの出力レベルを保持して出力する第1ラッチ回路と、第1期間には、C3にLレベルの電圧を印加するとともに、C2にHレベルの電圧を印加し、第2期間には、C3にHレベルの電圧を印加するとともに、C2にLまたはHレベルの電圧を印加する制御回路と、を有する。

(もっと読む)

比較回路、集積回路装置及び電子機器

【課題】ヒステリシス幅を設定できる比較回路、集積回路装置及び電子機器等を提供すること。

【解決手段】比較回路は、第1の入力端子に入力信号SINが入力され、第2の入力端子に比較用の基準電圧VRが入力されるコンパレーター10と、コンパレーター10の出力信号SQをモニターする制御部20と、制御部20からのしきい値電圧制御信号SVTが入力される電圧生成回路30とを含み、電圧生成回路30は、コンパレーター10の出力信号SQの電圧レベルが第1のレベルである場合には、基準電圧VRとして、ヒステリシス幅を規定する高電位側しきい値電圧又は低電位側しきい値電圧のいずれか一方である第1のしきい値電圧を出力し、出力信号SQの電圧レベルが第2のレベルである場合には、基準電圧VRとして、高電位側しきい値電圧又は低電位側しきい値電圧の他方である第2のしきい値電圧を出力する。

(もっと読む)

ヒステリシスコンパレータ

【課題】 差動対に入力信号とオフセット電圧を入力し、この差動対に接続される負荷MOSトランジスタのゲートとドレインをたすき掛け接続する構成のヒステリシスコンパレータは、MOSトランジスタのサイズを調整することにより任意のヒステリシス幅を得ることができるが、ヒステリシス幅の1/2のオフセット電圧を与えなければならず、かつヒステリシス幅が半導体プロセスのばらつきによって変動してしまうという課題を解決する。

【解決手段】 差入力信号Vinと閾値Vthが入力される差動対30と負荷部31で構成され、ヒステリシス特性を有する第1のコンパレータ部と、負荷部32と差動対30で構成され、ヒステリシス特性を有さない第2のコンパレータ部の動作を、ヒステリシスコンパレータの出力Voutによって切り替えるようにした。第2のコンパレータ部が動作するときは、出力Voutが遷移する電圧は閾値Vthのみで決まるので、半導体プロセスの影響を受けない。

(もっと読む)

ヒステリシスコンパレータ回路及びそれを用いた遅延回路

【課題】回路規模を大型化することなく、大きな遅延時間を得る。

【解決手段】遅延対象の矩形波の入力信号Vinを台形波発生回路10により台形波信号Vcに変換し、その台形波信号の中間電圧よりも高く設定された第1のスレッショルド電圧Th1を有するインバータ21と、中間電圧よりも低く設定された第2のスレッショルド電圧Th2を有するインバータ22とで、台形波信号Vcと第1及び第2のスレッショルド電圧を比較し、インバータ21とインバータ22の出力でバッファ回路23を駆動し、台形波信号Vcに同期して反転し、かつ遅延した矩形波の出力信号Voutを生成する。

(もっと読む)

クランプ機能付コンパレータ

【課題】追加的な製造プロセスを不要としながら一定且つ任意のクランプ電圧を設定できる。

【解決手段】信号入力線6の電圧が参照電圧VHよりも低い場合、信号ScがLレベル、スイッチ回路16がオフ、スイッチ回路17がオンとなり、FET14、15がオフする。信号入力線6の電圧が参照電圧VH以上になると、信号ScがHレベル、スイッチ回路16がオン、スイッチ回路17がオフとなり、クランプ回路4が動作可能となる。入力電圧がさらに上昇してクランプ電圧VCL以上になると、FET13がオンとなり、抵抗11、端子1a、抵抗12を介してFET13、14に電流が流れ、それに応じてFET15に電流が流れてクランプ動作する。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号の振幅が当初の想定よりも小さい場合や入力信号の振幅変動が生じた場合でも、適正な出力信号を得ることができるヒステリシスコンパレータを提供する。

【解決手段】電圧レベルが連続的に変化する入力信号を互いに異なる電圧レベルを有する2つの閾値電圧に基づいて2値化判定し、この判定結果に応じた出力信号を生成するヒステリシスコンパレータであり、入力信号のトップピークを検出し、トップピークに応じたトップピーク検出電圧を生成するトップピーク検出部と、入力信号のボトムピークを検出し、ボトムピークに応じたボトムピーク検出電圧を生成するボトムピーク検出部と、トップピーク検出電圧の電圧レベルとボトムピーク検出電圧の電圧レベルの範囲内で第1および第2の閾値電圧を生成する閾値電圧生成部と、第1および第2の閾値電圧と入力信号の電圧レベルを比較して入力信号を2値化判定し、この判定結果に応じた出力信号を生成する電圧比較部と、を含む。

(もっと読む)

電圧比較回路、その電圧比較回路を有する半導体集積回路及び電子機器

【課題】しきい値のばらつきを低減させ、入力される2信号の間に所定のオフセット電圧が発生したことを検出する高速かつ高精度なオフセット付きの電圧比較回路、その電圧比較回路を有する半導体集積回路及び電子機器を得る。

【解決手段】定電流回路12と差動入力回路11の一方の入力トランジスタM1との間に接続された抵抗R1を備え、電流制御回路4によって、該抵抗R1の両端電圧差が基準電圧Vrefの所定値Vaで一定になるように、各入力トランジスタM1及びM2にバイアス電流を供給する定電流回路12をなすPMOSトランジスタM3から出力される電流が制御されるようにした。

(もっと読む)

パルス検出装置

【課題】受信結果を監視しながらパルス検出感度を自動調整することができるパルス検出装置を実現する。

【解決手段】入力信号の誤検出を防止するパルス検出装置に関する。ヒステリシスを調整可能なヒステリシスコンパレータで入力信号をパルス信号として検出するパルス入力検出部と、パルス信号の周波数を算出するパルス入力処理部と、この周波数を監視し、ヒステリシスコンパレータのヒステリシスを調整する調整データを制御する調整制御部と、調整データを記憶手段に保持するとともに、調整制御部の指令によりパルス入力検出部に調整データを出力するドライブ制御部とを設けた。

(もっと読む)

高ヒステリシス幅入力回路

【課題】従来のヒステリシス入力回路は等価的にP型MOSFETとN型MOSFETのインバータ回路のβ比を変えて、ロジックレベルのヒステリシスを作っていたが、この方式では電源電圧が低下するとヒステリシス幅が極端に小さくなった。また、電源電圧の広範囲の変動に対してヒステリシス幅を確保することは難しかった。また、ロジックレベルを形成するのにP型とN型MOSFETを用いるので形状比の設定にやや無理があり、また製造工程でのバラツキの影響を受けやすかった。

【解決手段】入力インバータ回路と正極の電源にP型、N型MOSFET、負極の電源にN型、P型MOSFETと、及び前状態を過渡的にでも記憶・遅延する遅延回路を設け、前状態により、前記各MOSFETをオン・オフすることにより、ヒステリシス特性を得る。電圧特性が異なるMOSFETを使い分けることにより、前述の課題が解消できた。

(もっと読む)

入力処理回路

【課題】待機中の暗電流を無くし、且つ、ノイズに強い入力処理回路を提供すること。

【解決手段】入力端子101と出力端子102との間に、入出力特性にヒステリシスを付与したコンパレータ110を配置してなる入力処理回路100であって、入力端子101にCMOSシュミット120を接続し、CMOSシュミット120の閾値を、立ち上がりエッジ検出時において、コンパレータ110よりも低く設定し、CMOSシュミット120からの出力信号を、コンパレータ110の動作状態を制御するイネーブル信号EB1に用いるようにした。

(もっと読む)

波形整形回路及びそれを備えた半導体集積回路

【課題】 入力信号を二値波形に整形して出力する波形整形回路において、入力信号の中間電圧等を基準として上下対称にスレッショルド値を調節することができる波形整形回路を提供すること。

【解決手段】 前記入力信号と閾値との比較結果に応じて第1の電圧又は第2の電圧を出力する比較器と、前記閾値を生成する閾値生成部と、を備え、前記閾値生成部は、基準電圧を生成する基準電圧生成部を有し、前記比較器の出力が第1の電圧のときには前記閾値を基準電圧に対して所定値高い電圧に切り換え、前記比較器の出力が第2の電圧のときには前記閾値を前記基準電圧に対して前記所定値低い電圧に切り換える。

(もっと読む)

ヒステリシス特性を有するコンパレータ

【課題】ヒステリシスを有するコンパレータを提供すること。

【解決手段】一実施形態においてコンパレータは、入力電圧及び基準電圧を受け取り第1の差動出力を生成する第1の差動入力段と、差動入力を有し第2の差動出力を生成する第2の差動入力段とを有する。コンパレータ段は、第1の差動出力及び第2の差動出力に応答し、コンパレータ出力を生成する。コンパレータはヒステリシス制御回路を更に有し、ヒステリシス制御回路はその構成要素として、1)第2の差動入力段の差動入力間に接続された抵抗器及びヒステリシス調整電圧、2)第1の電圧発生器及び第2の電圧発生器、並びに3)コンパレータ出力の制御により、第1の電流発生器と第2の電流発生器の異なる組み合わせを作動させ、抵抗器を流れる第1の電流又は第2の電流を誘導する、少なくとも1つのスイッチを有する。

(もっと読む)

ヒステリシス発生回路

【課題】 簡単な構成により、入力電圧がゆっくり変化する場合に反転回路の閾値電圧を可変させ、ヒステリシスを発生できるようにする。

【解決手段】 入力信号を受けて当該入力信号の反転信号を出力する第1反転回路2と、この第1反転回路からの出力を受けて反転信号を出力する第2反転回路3と、複数の定電流源とこれらの切り替えを行う切替手段を備え第1反転回路2へ供給する電流を切り替える電流切替部と、この電流切替部における電流の切り替えを制御する電流制御部とを有する構成とする。

(もっと読む)

1 - 17 / 17

[ Back to top ]