Fターム[5J039KK05]の内容

Fターム[5J039KK05]の下位に属するFターム

セット優先、リセット優先型 (1)

Fターム[5J039KK05]に分類される特許

1 - 20 / 73

パルス幅延長回路および方法

半導体装置

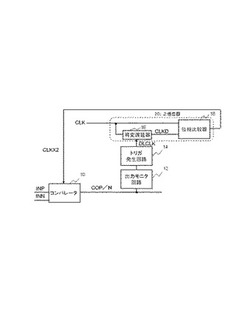

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

時間差増幅回路

【課題】時間差増幅回路の時間差オフセットを低減する。

【解決手段】複数の時間差増幅器が多段接続された時間差増幅回路100であって、複数の時間差増幅器は、第1の正入力端子1a、第1の負入力端子1b、第1の正出力端子1c及び第1の負出力端子1dを有する第1の時間差増幅器TDA1と、第2の正入力端子2a、第2の負入力端子2b、第2の正出力端子2c及び第2の負出力端子2dを有し、第1の時間差増幅器の出力信号が入力される第2の時間差増幅器TDA2と、第2の正入力端子2aに第1又は第4の配線I1,I2を接続させる第1の選択素子S1と、第2の負入力端子2bに第2又は第3の配線I2、I3を接続させる第2の選択素子S2を有する選択回路10aと、選択回路10aを制御する制御回路50を具備する。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

信号伝達装置

【課題】ハイブリッド自動車、電気自動車、家電機器、産業機器、及び医療機器の分野では、入出力間を直流的に絶縁した信号伝達装置が用いられているが、並列接続された2つのトランスに入力されるノイズレベルが互いに異なる場合でも、ノイズキャンセルを正常に作動させる。

【解決手段】信号伝達装置100は、1次巻線T11と2次巻線T12とは直流的に分離されており、1次巻線T11と2次巻線T12とは互いに別々の接地電位に接続されるトランスT1と、前記トランスT1の2次巻線T12からの出力が入力される第1コンパレータCM1及び第2コンパレータCM_M1と、前記第1コンパレータCM1の出力が入力される遅延信号生成部141aと、前記第2コンパレータCM_M1の出力が入力されるマスキング信号生成部143aとを有する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

半導体集積回路及びノイズ耐性検査方法

【課題】半導体集積回路のノイズ除去機能の特性を正確に測定することができる半導体集積回路及びノイズ耐性検査方法を提供する。

【解決手段】半導体集積回路1Aは、入力信号IN中のノイズ成分の振幅を減衰させてノイズ除去信号OUTを出力する入力バッファ11と、ノイズ除去信号OUTの論理レベルが変化したときに、この論理レベルの変化に応じて論理信号をラッチする論理回路12,13とを備える。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

ヒステリシスコンパレータ

【課題】簡単な回路構成で、広範囲で高精度かつ低いヒステリシス特性を持たせることができるヒステリシスコンパレータを提供する。

【解決手段】ヒステリシスコンパレータ1において、差動対30の一方に定電流源2の負荷抵抗22と比精度が保たれている抵抗23が設けられているコンパレータ回路3、4の出力をRSラッチ5のリセット、セット入力とし、入力信号Vina、Vinbをコンパレータ回路3、4へ入力する際は互いに逆になるように入力する。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

同期信号発生回路

【課題】 PWM信号からその同期信号を発生する。

【解決手段】 三角波発生回路101は、PWM信号PWMINの立ち上がりエッジおよび立ち下がりエッジの各々を検出する度に、先行して開始した三角波信号の発生と並行して三角波信号を発生する手段であり、立ち上がりエッジまたは立ち下がりエッジの検出後、三角波信号を基準レベルから一定の時間勾配で変化させ、その後、同種のエッジが検出された以降、同じ大きさの逆方向の時間勾配で三角波信号を変化させる。同期信号発生部160は、三角波発生回路101が発生する三角波信号TRIA、TRIB、TRICに基づいてPWM信号PWMINに同期した同期信号SYNCを発生する手段であり、相前後して発生を開始した2個の三角波信号の大小関係が逆転したとき、同期信号SYNCのレベルを反転させ、先行して発生を開始した三角波信号を基準レベルに初期化する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れ、かつ低消費電流でかつ多段接続が可能な増幅回路を実現する。

【解決手段】第1の電位変換用トランジスタ対(MN1,MN2)および第2のプリチャージトランジスタ対(MP3,MP4)を用いて電流/電圧変換用の容量素子(CL1,CL2)の対向電圧をそれぞれ第1の電源(VDD)レベルおよび第2の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第1の電源から差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。この容量素子への電流供給停止後、第1のトランジスタ対(MN1,MN2)をオン状態、第2のトランジスタ対(MP3,MP4)をオフ状態に設定し、出力ノード(2a,2b)の電圧のレベルシフトをして、出力信号(VON,VOP)を生成する。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

1 - 20 / 73

[ Back to top ]