Fターム[5J039MM10]の内容

Fターム[5J039MM10]に分類される特許

1 - 20 / 43

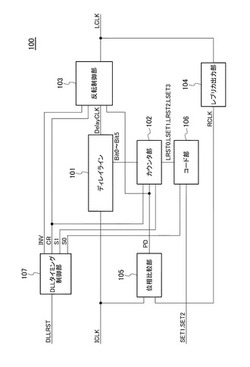

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

DCオフセット及び位相差検出装置及びDCオフセット及び位相差検出方法

【課題】互いに位相の異なるクロック信号の段階的な調整に適したDCオフセット及び位相差検出装置及びDCオフセット及び位相差検出方法を提供すること

【解決手段】本発明にかかるDCオフセット及び位相差検出装置50は、互いに位相の異なる第1及び第2のクロック信号の各々のDCオフセット量を検出し、各クロック信号のDCオフセット量を示すDCオフセット信号を生成するDCオフセット検出部51と、前記DCオフセット信号に応じて前記第1及び第2のクロック信号をDCオフセット調整することで生成された第3及び第4のクロック信号の位相差量を検出し、前記位相差量を示す位相差信号を生成する位相差検出部52とを備える。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

ジッタ低減回路および半導体集積回路

【課題】クロック信号に乗るジッタを低減することが可能なジッタ低減回路および半導体集積回路の提供を図る。

【解決手段】第1クロック信号CLK1の第1周波数を測定する第1周波数測定回路11と、第2クロック信号CLK2の第2周波数を測定する第2周波数測定回路12と、測定された前記第1および第2周波数を比較し、該第1および第2周波数が所定の関係に有るかどうかを判定する周波数比較判定回路20と、前記周波数比較判定回路からの第1制御信号CNT1を受け取り、前記第1クロック信号の遅延を制御して前記第2クロック信号によるジッタを低減する第1遅延制御回路41と、を有するように構成する。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

半導体集積回路

【課題】雑なクロック選択回路に対応できる半導体集積回路を、簡単な配置クラスタリング工程で作製できるようにする。

【解決手段】クロック信号を種々の遅延量で遅延調整するクロックツリー回路と、遅延調整されたクロック信号が供給されるクロック同期回路とを備える。クロックツリー回路は、クロック信号導入端の後段に設けられた第一のクロックツリーセルと、クロック同期回路の前段でかつ第1のクロックツリーセルより後段に設けられた第二のクロックツリーセルと、第二のクロックツリーセルの前段に設けられたクロック分岐点とを備える。クロック同期回路は第二のクロックツリーセルで遅延調整されたクロック信号が供給される第一のクロック同期回路とクロック分岐点でクロックツリー回路から出力されるクロック信号が供給される第二のクロック同期回路とを備える。

(もっと読む)

半導体装置

【課題】第1電源で動作する第1回路および第1電源とは異なる第2電源により動作する第2回路を有する半導体装置において、第1回路から第2回路に供給する信号におけるジッタの発生の抑制を図る。

【解決手段】第1電源線5(AVD)および第2電源線6(AVS)に接続された第1回路1と、第3電源線7(VDD)および第4電源線8(VSS)に接続された第2回路4(3)と、前記第1回路から出力される第1信号を受け取って前記第2回路に第2信号を供給するバッファ11と、前記第1電源線と前記第3電源線との電位差に応じて前記バッファの遅延時間を制御する制御部10と、を備えるように構成する。

(もっと読む)

半導体装置

【課題】 半導体装置におけるクロックスキューを低減する。

【解決手段】 第1のサブクロックツリー802と、第2のサブクロックツリー803とを有し、それぞれのサブクロックツリーにおける相対位置の等しい末端クロックドライバの出力クロックの位相が一致するように、可変遅延素子805で遅延させたクロックを第2のサブクロックツリー803に入力する。

(もっと読む)

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

電子回路装置

【課題】パルス幅を意図的に変化させるNRZ等の信号の伝送において、パルス幅のバラツキの低減を図り、さらにジッタの低減も図る。

【解決手段】2個のエッジ検出回路11,12と、2個の可変遅延回路13,14と、SRラッチ回路15とを備え、可変遅延回路13,14のそれぞれの入力にエッジ検出回路11,12の出力を接続し、SRラッチ回路のS入力およびR入力それぞれに可変遅延回路13,14の出力を接続する。前記SRラッチ回路15が、可変遅延回路13,14の出力のパルス終端側エッジを検出してセット/リセット動作を行う。

(もっと読む)

マルチクロックネットワークを備えたデジタルデバイス用共振クロックおよびインターコネクトアーキテクチャ

バッファなしでクロックおよびデータ信号を分配する共振ドライバを使ったクロック、データ分配ネットワークが提案されており、低ジッター、低スキュー、低エネルギー消費、そして緩いタイミング要求が実現される。このようなネットワークは、概してFPGAのようなPLD用アーキテクチャに適用可能であり、同様に、マイクロプロセッサ、ASIC、SOCなど、複数のクロックネットワークとクロック周波数、ハイパフォーマンスおよび低電力クロッキング仕様をもつ他の半導体デバイスにも適用可能である。  (もっと読む)

(もっと読む)

1 - 20 / 43

[ Back to top ]