Fターム[5J039MM13]の内容

Fターム[5J039MM13]に分類される特許

1 - 20 / 41

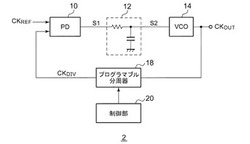

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の検査方法

【課題】ジッタ耐性検査における検査コストの低減を図りつつ、入力される主信号の特性劣化を抑制できる半導体集積回路を提供する。

【解決手段】半導体集積回路101は、主信号にジッタ信号が付加されてなる検査信号を生成する機能を有し、ジッタ信号の基となる信号を生成するジッタ信号生成部50と、電源線Vccと接地線GNDとの間に介在し、電源線Vccからの電力供給を受けて外部からの主信号を増幅して出力するバッファ回路10と、電源線Vccとバッファ回路10との間およびバッファ回路10と接地線GNDとの間に介在し電源線Vccからバッファ回路10への供給電力をジッタ信号の基となる信号の大きさに基づいて変化させることにより主信号にジッタ信号を付加するジッタ信号付加部30とを備える。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を含むSSCG回路であって、出力クロック信号のジッタを低減する。

【解決手段】SSCG回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた第1の移相量で変化させるように、さらに、所定の範囲内で周期的に変化する第2の移相量を第1の移相量に加算するように、位相選択回路6を制御する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

ジッタ付加装置及びジッタ付加方法

【課題】ジッタ付加対象である対象信号に付加するジッタのパラメータを簡便に設定できる。

【解決手段】ジッタ付加対象となる対象信号に対して任意に設定したジッタを付加するジッタ付加装置1において、位相変調量と変調周波数の2つのパラメータで座標軸が構成される2次元グラフデータからなり、機器毎に設定されたジッタ設定可能範囲が示されるパラメータグラフ情報を表示する表示部15と、パラメータグラフ情報が表示される同一画面上に表示されたポインタPで当該パラメータグラフ情報のジッタ設定可能範囲内の任意の位置を選択する際に操作される操作部11と、ポインタの座標位置に応じて前記対象信号に付加するジッタの各パラメータを設定する制御部13とを備えた。

(もっと読む)

半導体設計装置

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

クロック生成回路

【課題】小規模な回路で、クロックノイズが小さなクロック信号を生成可能なクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1の電流生成回路と、第1の電圧生成回路と、第1の比較回路と、第2の電流生成回路と、第2の電圧生成回路と、第2の比較回路と、クロック出力回路と、制御回路と、を備える。クロック出力回路は、第1および第2の比較結果が変化するタイミングに同期して位相が変化するクロック信号を生成する。制御回路は、前記クロック信号に同期して乱数を生成し、この乱数に応じて、第1の電流、第2の電流、第1の閾値および第2の閾値電圧のうち、少なくとも1つを可変制御する。

(もっと読む)

受信機器及び画像形成装置

【課題】周波数を周期的に増減させた拡散クロック信号を用いてデータを受信する場合に生じ得る通信の不成立を未然に防止でき、確実にEMI低減効果を得ることができる受信機器及び画像形成装置を提供する。

【解決手段】拡散クロック信号に基づいて、複数のビットを含むフレーム単位でデータを受信する際、受信速度に基づいて受信すべきデータのビット当たりの受信時間を算出し、該ビット当たりの受信時間に応じて前記拡散クロック信号の変更周期を調整する。

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

1/fゆらぎ信号発生回路

【課題】

複数出力の、且つそれぞれの出力が異なる値の1/fゆらぎ信号を発生させ、複数の白熱電球やLED素子の発光をそれぞれに接続された1/fゆらぎ信号によって駆動し、イルミネーション効果を実現する。

【解決手段】

複数段のLFSR(リニアフィードバックシフトレジスタ)で構成されたGold系列の乱数発生回路において、各LFSR段のシフトレジスタ中の任意のレジスタのビット出力の値を、排他的論理和素子で構成された複数の加算器で加算し、それぞれの加算器の出力をシリアル−パラレル変換器に入力し、パラレルビットの値として、複数の乱数値を同時に出力

し、複数のデジタル・フィルタに入力し、複数の個々異なる1/fゆらぎ信号を同時に発生させることができる。

(もっと読む)

システムにおけるフォールトトレラントなスペクトラム拡散クロック信号の提供

【課題】システムにおけるフォールトトレラントなスペクトラム拡散クロック信号を提供する。

【解決手段】フォールトトレラントなスペクトラム拡散クロック信号を供給するために、それぞれスペクトラム拡散制御回路を有する複数の処理モジュールが提供される。冗長なクロック供給源のクロック信号は、前記複数の処理モジュールに対して供給されるファイルオーバー制御ロジックは前記複数の処理モジュールそれぞれにおいて使用するために前記冗長なクロック供給源から前記クロック信号のうちの対応する1つを選択する。周波数拡散が、少なくともいくつかの前記複数の処理モジュールそれぞれにおいて前記対応する選択されたクロック信号に適用される。

(もっと読む)

ジッタ発生器

【課題】簡単な構成で出力信号のジッタ量を設定することを可能にしたジッタ発生器を提供する。

【解決手段】出力信号を伝送するための第1の信号線と、第1の信号線に隣接する第2および第3の信号線と、を有し、第2および第3の信号線のそれぞれは第1の信号線に対して任意の配線カップリングノイズを与える。出力信号を伝送する第1の信号線は、隣接する第2および第3の信号線のそれぞれとの距離や信号線の長さに対応する配線カップリングノイズが第2および第3の信号線から与えられ、与えられた配線カップリングノイズに応じたジッタを発生する。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

オーディオ装置及びオーディオ処理方法

【課題】従来技術における高周波クロック信号が生成する電磁妨害(EMI)を軽減させる。

【解決手段】本発明一実施例は、オーディオ装置を提供する。オーディオ装置は、デジタルマイクモジュールとオーディオコーデックを有する。デジタルマイクモジュールは、スペクトラム拡散クロックに基づき外部音源を捉えて、デジタル音源信号を発生する。オーディオコーデックは、クロック発生モジュール、格納ユニット、オーディオコーデックコアを有する。クロック発生モジュールは、クロック信号とスペクトラム拡散クロックを発生する。格納ユニットは、スペクトラム拡散クロックに基づきデジタルマイクモジュールからの第一デジタル音源信号を一時記憶し、クロック信号に基づき第一デジタル音源信号を出力する。オーディオコーデックコアは、デジタル−アナログ変換回路とアナログ−デジタル変換回路を有する。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

リタイミング回路及び分周システム

【課題】クロック信号の同期エッジのタイミングと入力信号のエッジのタイミングが一致したときの誤動作を防止することができるリタイミング回路及び分周システムを提供することを課題とする。

【解決手段】第1及び第2のクロック端子に差動クロック信号を入力し、第1及び第2の入力端子に第1の差動信号を入力し、第1及び第2の出力端子から第2の差動信号を出力する第1のフリップフロップ回路(102)と、前記第2の差動信号を構成する第1及び第2の信号が同相になると同相検出信号を出力する同相検出回路(105)と、前記同相検出信号のカウント値をカウントするカウンタ(106)と、前記カウンタのカウンタ値に応じて前記第1のフリップフロップ回路の前記第1及び第2のクロック端子に入力する前記差動クロック信号の位相を切り換えるセレクタ(101)とを有することを特徴とするリタイミング回路が提供される。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

1 - 20 / 41

[ Back to top ]