Fターム[5J042BA11]の内容

論理回路 (4,317) | 論理回路の種類 (1,203) | 構成要素がマトリックス状に配置されたもの (595) | PLA (556) | 再プログラムが可能なもの (269)

Fターム[5J042BA11]に分類される特許

141 - 160 / 269

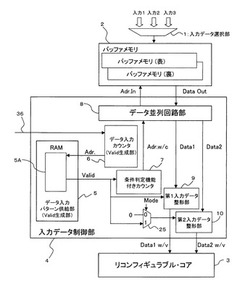

集積回路及びリコンフィギュラブル回路の入力データ制御方法

【課題】入力データをリコンフィギュラブル回路で確実に処理できるようにする。

【解決手段】本集積回路は、再構成可能に相互に結合される複数の演算器を含むリコンフィギュラブル回路3と、入力データ制御部4とを備える。そして、入力データ制御部4によって、リコンフィギュラブル回路3の構成に応じてデータが入力されるように入力データが制御される。

(もっと読む)

半導体装置

【課題】動的に回路構成を再構成可能な半導体装置にて、回路構成の再構成に係る制御情報量を低減できるようにする。

【解決手段】コンフィグレーションデータを記憶する制御データ用メモリ24と、演算器26とを有し、コンフィグレーションデータに応じて回路構成を再構成可能な複数の演算部22と、コンフィグレーションデータを制御データ用メモリから出力させるための構成指定データを記憶するコンフィグレーションメモリ13Aとを備え、コンフィグレーションメモリにはコンフィグレーションデータを記憶せずに、制御データ用メモリからコンフィグレーションデータを出力させるための情報のみを記憶するだけで、コンフィグレーションデータを供給することができるようにする。

(もっと読む)

データ処理装置

【課題】コンフィグの実行パターンが処理の進行過程で変更される場合であってもコンフィグデータデータを遅滞なくロードできるデータ処理装置を提供する。

【解決手段】複数の素子を適宜組み合わせて構成される複数の回路エレメントにより構成されたプロセッサエレメントアレイ38を備え、プロセッサエレメントアレイ38に実装する種々の回路構成を示すコンフィグデータを複数記憶部20に記憶しておき、予め設定された処理の実行時にプロセッサエレメントアレイ38に実装する順番に応じて、次に実装する回路構成を示すコンフィグデータを示すポインタが対応付けされたコンフィグ実行パターンリストに従って前記記憶手段に記憶されたコンフィグデータを読み出して前記エレメントアレイに実装するに際し、処理の進行に伴い、必要な回路構成だけを実装すべくポインタを付け替える。

(もっと読む)

情報処理システム

【課題】実行中の処理より優先度が高い処理を割り込ませて実行させる場合でも、該割り込み処理を迅速に行なうことができる情報処理システムを提供する。

【解決手段】ローカルメモリ22に、プログラマブル論理回路21の再構成に使用する、予め優先度が設定された複数個の回路情報を格納しておき、予め指定された回路情報の使用順序と回路情報に予め設定された優先度とに基づいて、ローカルメモリ22からプログラマブル論理回路21を再構成するための回路情報を選択し、該選択した回路情報を使用してプログラマブル論理回路21を再構成する。

(もっと読む)

プログラム可能テストクロックコントローラを使用した電子回路のスキャンベーステスト用に構成可能なテストクロックを生成するためのテストクロック制御構造

【課題】スキャンチェーンのテストクロックを生成して電子回路のスキャンベースのテストを実施するためのシステム、構造、及び方法が開示される。

【解決手段】1つの実施形態では、テストクロック制御構造は、プログラム可能テストクロックコントローラを含む。プログラム可能テストクロックコントローラは、構成可能なテストクロックを生成するためのテストクロックジェネレータを含む。コントローラはまた、構成可能なテストクロックでスキャンチェーン部分を駆動するスキャンレイヤインタフェースと、スキャンチェーン部分を制御するための制御情報にアクセスするように構成された制御レイヤインタフェースを含む。

(もっと読む)

光再構成ゲートアレイの再構成制御装置及びその方法

【課題】光再構成ゲートアレイの各種論理演算回路を正確且つ確実に書込むと共に、各々を迅速に起動して論理演算を高速化できる光再構成ゲートアレイの再構成制御装置を提供する。

【解決手段】再生光のレーザ光1aを発光して照射するレーザアレイ1と、予め格納された記録情報に基づいてレーザ光1aの照射により光パターン2aを射出すると共に、光再構成に関する制御信号光2bを射出するホログラムメモリ2と、光パターン2aに基づいてアレイ状に配列された複数の論理演算セルを各種の論理演算回路に再構成し制御信号光2bに基づいて光制御信号S4を出力する光再構成型ゲートアレイ3と、レーザアレイ1で発光されるレーザ光1aの照射を制御する再生光照射制御手段4とを備える構成により、各種の論理演算回路を書込みエラーを生じることなく、正確且つ確実に書込みが実行できると共に、各種論理演算回路を連続して順次高速に論理演算を実行できる。

(もっと読む)

論理動作回路、論理切換方法及び電子機器

【課題】 実装の高密度化や多機能化が進む状況下においても、部品点数の増加や基板面積の拡大、基板数の増加を招くことなく、実行効率を向上可能とする。

【解決手段】 基板A上に搭載された論理動作回路1が、プログラム可能な論理回路であるプログラマブルデバイス(PLD/FPGA)10と、時系列的に同時動作しない論理グループが書き込まれた複数の記憶手段(ROM21〜2n)と、指示信号にもとづき複数の記憶手段の中から一つの記憶手段を選択する選択手段と、選択された記憶手段内の論理をプログラマブルデバイスに書き込む書込手段とを備えた。

(もっと読む)

集積回路及びその回路設定生成方法

【課題】 一度マッピングツールで回路設定をしておくだけで簡単に複数の回路設定が得られる集積回路及びその回路設定生成方法を提供することを課題とする。

【解決手段】 再構成可能集積回路を構成する基本タイルのアレイ間の配線の少なくとも一部が、n(nは、1以上の整数とする)次元のトーラス状に接続されている集積回路及び再構成可能集積回路上に実現する同一の機能を有するがその性能が異なる確率変数に従う複数の異なる回路設定を、一つの回路設定を基本タイルのアレイのトーラス状に接続された方向に沿って移動させることにより作成することを特徴とする集積回路の回路設定生成方法により解決される。

(もっと読む)

再構成可能な集積回路デバイス

【課題】再構成可能な集積回路デバイスを搭載したシステムにおいて、容易かつ確実にハードウエアの破壊を回避することができる再構成可能な集積回路デバイスの提供を目的とする。

【解決手段】内部回路21に関する設定情報の記憶領域24aと外部端子22に関する設定情報の記憶領域24bを備え、前記記憶領域の設定情報の書き換えが可能な集積回路デバイスであって、内部回路21に関する設定情報の書き換えは任意とされ、外部端子22に関する設定情報の書き換えは制限されている。外部端子22に関する設定情報の書き換えの制限は、例えば、1回に限定されているか又はプロテクト機能解除を必要とする構成を用いることができる。

(もっと読む)

集積回路のための再構成可能論理ファブリックおよび再構成可能論理ファブリックを構成するためのシステムおよび方法

本発明によれば、集積回路のための非同期再構成可能論理ファブリックおよび非同期再構成可能論理ファブリック内に実装されるべき非同期回路を設計するための方法が、ここに提供される。  (もっと読む)

(もっと読む)

プログラマブル論理デバイス、回路情報入力制御装置および半導体装置

【課題】データ転送用に特別な回路を専用に用意することなく、データの通信部分が処理性能全体のボトルネックとならないようにすることができるとともに、メモリに記録するのと同程度の回路間の設計の独立性を確保することができるプログラマブル論理デバイスを提供する。

【解決手段】処理回路部において論理回路Aと論理回路Bとを続けて実行する際に(S1〜S5)、処理回路部が論理回路Aの実行終了後に(S6のYes)、回路情報入力制御部の制御によって論理回路Aと論理回路Bのどちらでも利用するデータの転送を行うためのデータ転送用論理回路である論理回路Tに切り替え(S7)、処理回路部が論理回路Tによるデータ転送の実行を終了した後(S8のYes)、回路情報入力制御部の制御によって論理回路Bに切り替える(S9〜S10)。

(もっと読む)

フィールドプログラマブルプロセッサアレイ

【課題】高密度回路のレイアウト、処理装置間の効率の良い相互接続、および処理装置を相互接続可能にする自由度のある方法を提供すること。

【解決手段】回路エリア12のいくつかは、少なくとも1つのそれぞれの入力信号経路(an,aw、be,bs,hci,vci)におけるデータの操作を実行し、少なくとも1つの出力信号経路(fn,fe,fs,fw,vco,hco)によってデータを送出するためのそれぞれの処理装置を備える。その他の回路エリアはそれぞれのスイッチングセクション14を備え、処理装置およびスイッチングセクションが、各行および各列内において交互に配列されている。スイッチセクションの大部分はそれぞれ、同じ列および同じ行におけるスイッチングセクションに隣接した処理装置の信号経路の一部の間にプログラマブル接続16,18,20を備える集積回路を提供する。

(もっと読む)

低電圧差動信号ドライバ、低電圧差動信号を駆動する方法及びシステム

【課題】低い伝送速度で大きな出力電圧振幅をもたらし且つ高い伝送速度で低い出力電圧振幅を単独のドライバでもたらすこと。

【解決手段】低電圧差動信号(LVDS)ドライバは、信号を駆動するよう動作する少なくとも2つのプログラマブルフィンガと、少なくとも2つのプレドライバとを含む。プレドライバの各々は1つのプログラマブルフィンガに関連し且つ該関連するプログラマブルフィンガをイネーブルに又はディセーブルにする。イネーブルにされたプログラマブルフィンガは信号を駆動し且つ当該ドライバの容量負荷に寄与し、ディセーブルにされたプログラマブルフィンガは信号を駆動せず且つ当該ドライバの容量負荷に寄与しない。

(もっと読む)

プログラマブルロジックデバイス

【課題】 内蔵するプログラマブルエリアに書き換え可能な論理回路を備えたプログラマブルロジテックデバイスにおいて、論理回路の書き換えのバージョンを確実で簡便に知ることが可能で且つプログラマブルエリアを大きく使用することを目的とする。

【解決手段】 プログラマブルエリア5において、最初の書き込みで、その書き込みの内容に対応した論理回路6、バージョン情報回路7及びバージョンデータを取り出すI/Oセル8が書き込まれ、2回目以降の論理回路の書き込みで、バージョン情報回路7が対応して更新させる構成とした。

(もっと読む)

集積回路装置

【課題】無効なデータを含むデータ列に対して精度の高い演算を行なうことができる集積回路装置を提供する。

【解決手段】データセット1を順番に、クロックに同期して遅延させた後に出力するための遅延回路62と、遅延回路62から出力されるデータセットをクロックに同期してセットするための遅延出力レジスタ65と、遅延回路62に入力されるデータセット1のトークン5が無効なときは遅延回路62の遅延を停止し、入力されるデータセット1のトークン5を遅延出力レジスタ65にセットするための遅延制御回路70とを含む遅延エレメント60を含む集積回路装置を提供する。

(もっと読む)

半導体装置

【課題】 パイプライン型に接続した複数のリコンフィギュラブル回路のそれぞれに、データを演算する実行回路を遅延無く構築することのできる半導体装置の提供。

【解決手段】 データ処理前に回路情報の幾つかを記憶し、データ処理時に規則信号に基づいて回路情報の一つを出力する回路情報制御部101と、その回路情報で実行回路を構築してデータを演算し演算結果を出力する演算器100と、その演算結果を保持し次のサイクルで出力するデータレジスタ102と、規則信号を保持し次のサイクルで出力する制御レジスタ103とをそれぞれ備える複数の演算ユニット10A〜Eを直列に接続した演算パイプラインと、前記演算パイプラインの初段の演算ユニットへの規則信号とデータとを出力するよう制御するコントローラ11とを備える。

(もっと読む)

プログラマブルロジックデバイス

【課題】従来のリコンフィギュアラブルコアを搭載したLSIでは、機能切り替え可能というリコンフィギュアラブルコアの特長を活かしきれず、ハードブロックを用いる従来技術よりもコストパフォーマンスの点で劣っていた。

【解決手段】リコンフィギュアラブルコアの機能切り替え可能という特長を活かすためには、LSI外部からLSI内部へのコンフィギュレーションデータの読み込みが、適切なタイミングで、高速に実現される必要がある。

コンフィギュレーションデータを格納したLSI外部のメモリとLSI内部のコンフィギュレーションデータ格納メモリ間に専用バスを設けること、あるいはLSI内部のコンフィギュレーションデータ転送に関わるブロックに対し、他ブロックとは独立のクロックドメイン、独立の電源ドメインを設定することにより上記課題を解決した。

(もっと読む)

再構成可能なマルチ処理粗粒アレイ

マルチ処理法で少なくとも2つの処理スレッドを同時処理するよう調整された信号処理デバイスである。デバイスはデータに関しワードレベル又はサブワードレベルの動作を実行する複数ファンクションユニットと、複数ファンクションユニットを相互接続する手段であって、動的スイッチされ複数相互接続構成をサポートし少なくとも一つの相互接続構成が複数ファンクションユニットを夫々所定のトポロジを備える少なくとも2つの非オーバーラップの処理ユニット中に相互接続する手段を含み、信号処理デバイスは更に個々の制御モジュールが処理ユニットの一つに割り当てられる少なくとも2つの制御モジュールを含む。本発明は更に信号処理デバイスでアプリケーション実行する方法、信号処理デバイスで実行されるコンパイルコードを取得しアプリケーションが信号処理デバイスで実行される方法を最適化するべくアプリケーションソースコードをコンパイルする方法を示す。  (もっと読む)

(もっと読む)

リコンフィグラブル回路

【課題】回路規模を削減し、かつ演算器群の出力端子及び入力端子の接続可能な組み合わせ数を増やすことができるリコンフィグラブル回路を提供することを課題とする。

【解決手段】演算器群(111〜11n)の出力端子及び入力端子間の接続を制御するネットワーク回路(105)と、前記演算器群及びネットワーク回路の間に接続される第1のセレクタ(106)とを有し、前記第1のセレクタは、第1の制御信号が第1の状態のときには前記演算器群の第1の端子と前記ネットワーク回路の第1の端子とを接続しかつ前記演算器群の第2の端子と前記ネットワーク回路の第2の端子とを接続し、第1の制御信号が第2の状態のときには前記演算器群の第1の端子と前記ネットワーク回路の第2の端子とを接続しかつ前記演算器群の第2の端子と前記ネットワーク回路の第1の端子とを接続することを特徴とするリコンフィグラブル回路が提供される。

(もっと読む)

論理プログラマブルデバイス保護回路

【課題】たとえ不都合な回路構成データが従来のセキュリティメカニズムを通過し、論理プログラマブルデバイスに入力されたとしても、当該デバイスおよび周辺回路に不具合を及ぼすことを防ぐ。

【解決手段】論理プログラマブルデバイスに入力された回路構成データ12を検査し、回路構成データ12から構成される回路が所定の条件を満足するか判定する構成回路検証部312と、該判定の結果に応じて、回路構成データ12から構成される回路が及ぼす不具合を防止するための保護動作を行う回路保護部320とを備える。

(もっと読む)

141 - 160 / 269

[ Back to top ]