Fターム[5J042BA11]の内容

論理回路 (4,317) | 論理回路の種類 (1,203) | 構成要素がマトリックス状に配置されたもの (595) | PLA (556) | 再プログラムが可能なもの (269)

Fターム[5J042BA11]に分類される特許

61 - 80 / 269

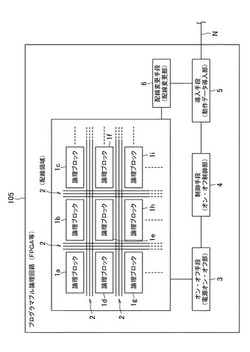

プログラマブル論理回路、半導体集積回路装置、情報処理システムおよび制御プログラム

【課題】効率的に消費電力を低減して省エネルギー性を向上させることのできるプログラマブル論理回路を提供する。

【解決手段】外部からのアクセスによりその論理演算処理が変更可能な複数の論理ブロック(1a〜1i)と、該論理ブロックの間の接続を外部からのアクセスにより変更可能な配線領域2と、各論理ブロック毎に電源をオン・オフ可能なオン・オフ手段(電源オン・オフ部3)と、システムの動作モードに対応させた動作データを導入する導入手段(動作データ導入部5)と、導入された動作データに基づいて指定された論理ブロックの電源をオン・オフさせる制御手段(オン・オフ制御部4)と、電源がオンされた論理ブロックについて、配線領域における各論理ブロック間の配線状態を動作データに含まれる回路データに基づいて変更する配線変更手段(配線変更部6)とを少なくとも備える。

(もっと読む)

動的再構成装置

【課題】実行中の処理の終了を待つことなく、演算内容を割り当てることができるようにして、処理全体の高速化を図る。

【解決手段】実行する処理の演算内容と上記処理を実行する際に必要なPE3の個数を記憶している処理基幹メモリ5と、動的再構成回路2を構成しているPE3の中で、現在処理を実行していないPE3を検出する空き領域検出部6と、空き領域検出部6により検出されたPE3の中から、処理基幹メモリ5により記憶されている個数分のPE3を選択する回路構成生成部7とを設け、マッピング制御部8が回路構成生成部7により選択されたPE3に対して上記演算内容を割り当てるように構成する。

(もっと読む)

ソフトエラーアップセット不感性を有する揮発性記憶素子

高エネルギーの原子粒子衝突に曝される際に、ソフトエラーアップセット事象に対して不感性を呈する記憶素子が提供される。記憶素子はそれぞれ、2つのアドレストランジスタと、双安定要素を形成するように相互接続される4つのトランジスタの対とを含む、10個のトランジスタを有してもよい。トゥルーおよびコンプリメントクリアライン等のクリアラインは、あるトランジスタの対と関連している正の電源端子および接地電源端子にルーティングされてもよい。クリア操作の際、トランジスタの対の一部または全部は、選択的にクリアラインを使用して、電力供給を停止することが可能である。これは、論理0値が、アドレストランジスタを介して駆動されるクリア操作を促進し、クロスバー電流サージを低減させる。  (もっと読む)

(もっと読む)

集積回路における故障耐性

【課題】 集積回路内の故障耐性を定めるシステム及び方法を提供する。

【解決手段】 集積回路内の故障耐性を定めるシステムは、集積回路によって保持されるプログラム可能論理デバイスを含むことができる。本システムはまた、プログラム可能論理デバイスによって保持される設定可能メモリを含んで、プログラム可能論理デバイスの一部分の機能及び/又は接続を制御することができる。本システムは、プログラム可能論理デバイスにより保持され、ユーザ及び/又は設定可能メモリと通信するユーザ論理をさらに含むことができる。ユーザ論理は、ユーザ要求の変化に基づいて設定可能メモリ内の破損データを識別することができる。

(もっと読む)

半導体装置

【課題】可変論理機能を実現するための記憶回路を論理回路と等価な回路として扱う構成において可変論理に対する機能設定の負担を軽減する。

【解決手段】半導体装置はアクセス制御装置(2)の制御を受ける機能再構成メモリ装置(8)を有し、機能再構成メモリ装置はアクセス制御装置からのアクセス要求を受け、インタフェース制御回路に複数の機能再構成セル(20)と機能再構成セルに一対一対応で設けられ機能再構成セルからの出力を受けて演算を行う可変演算セル(101)が接続される。機能再構成セルの制御回路は第1の動作モードで記憶回路の制御フィールドとデータフィールに初期設定された真理値データのようなデータを、第2の動作モードにおいて制御フィールドのデータに基づいて自律的に制御することによって論理動作を行う。可変演算セルは記憶回路の制御フィールドから出力される制御データなどに基づいて演算動作が可能にされる。

(もっと読む)

スイッチングボックス回路、スイッチングブロック回路、およびFPGA回路

【課題】高集積化および低消費電力化を可能にする。

【解決手段】第1乃至第4の方向にそれぞれ設けられた第1乃至第n(≧1)の信号線と、前記第1乃至第4の方向にそれぞれ設けられた第1乃至第nの入出力部であって、各方向における第i(1≦i≦n)の入出力部は、一端が対応する方向の第iの信号線に接続する第1乃至第nの入出力部と、第1乃至第2nの接続端子と、前記第1乃至第4の方向にそれぞれ設けられ、各方向において前記第1乃至第nの入出力部のそれぞれと、前記第1乃至第2nの接続端子のそれぞれを接続するためにそれらの間に1個ずつ設けられ、ゲートにクロック信号を受ける2n2個のスピンMOSFETと、を備えている。

(もっと読む)

プログラマブルコントローラおよびそれを用いたシステム

【課題】FPGAを用いて、高速応答を必要とする制御システムに組み込み可能としたプログラマブルコントローラを提供すること。

【解決手段】本プログラマブルコントローラ3は、シーケンス制御用ハードウエア論理回路が動作プログラムとして電源立ち上げ時に外部パーソナルコンピュータからロードされるFPGA10と、入力機器から入力信号を取り込むと共に制御信号に応じて出力信号を出力機器へ出力するもので、FPGAに接続されたI/O部7と、を備え、FPGA10は、内部ハードウエア論理回路でI/O部7からの入力信号を処理すると共に、I/O部7に制御信号を出力し、I/O部7は、FPGA10からの制御信号に応答して出力信号を出力する。

(もっと読む)

FPGAのコンフィギュレーション回路

【課題】 FPGAをコンフィギュレーションする際に、コンフィギュレーション専用フラッシュROMを用いていたが、このフラッシュROMの起動時間が長いのでコンフィギュレーションに時間がかかり、FPGAが起動するまでの時間が長くなってしまうという課題を解決する。

【解決手段】 2バイト以上のデータバス幅を有する汎用メモリにコンフィギュレーションデータを書き込み、このメモリの出力を一括してラッチ回路に取り込み、バイト単位でFPGAに出力するようにした。FPGAのコンフィギュレーション準備時間待つだけでコンフィギュレーションを開始することができるので、FPGAの起動時間を短くすることができる。また、複数バイトのデータを一括してラッチ回路に取り込み、このラッチ回路からバイト単位でFPGAにコンフィギュレーションデータを出力するようにしたので、フラッシュROMのようなアクセス時間が長くかつ安価なメモリを使用することができる。

(もっと読む)

データ処理装置

【課題】再構成可能なデータ処理装置を提供する。

【解決手段】エレメント(RXE)53は、4系統の入力61と、4系統の出力62と、4系統の入力61から任意の入力データを選択する入力インタフェース63と、この入力インタフェース63により選択された入力データφiを論理演算してデータを出力する演算コア65と、4系統の入力61と演算コア65の出力データφoとを任意に選択して4系統の出力62へ接続可能な出力インタフェース64とを備えている。演算コア65は、論理を変更可能な演算エレメントとしての機能を果たす。また、入力インタフェース63は、4系統の入力61から任意の1ビットを選択するための16対1のセレクタ63sが複数配置された構成となっている。出力インタフェース64は、演算コア65からの出力φoと4系統の入力61のルーティングを兼ねた7対1のセレクタ64sが複数配置された構成となっている。

(もっと読む)

ビデオ用およびその他の用途に用いられるクロスポイント・スイッチ

スイッチ再構成タイミング要件の異なる複数のデータフォーマットを同時にサポートするクロスポイント・セレクタスイッチは、演算スイッチ・データに応じて、その出力を選択的にその入力のそれぞれからデータを受け取るように接続する構成可能なスイッチ部と、このスイッチ部に演算スイッチ・データを供給するように動作可能に接続されている構成部とを備えている。構成部は、スイッチ部の複数の異なる構成をサポートするスイッチ構成データを記憶し、また、構成部は、スイッチ部の異なる構成とそれぞれ関連付けられた異なる演算更新コマンドを受け取って、異なる演算更新コマンドのどれを受け取ったのかに基づき、記憶しているスイッチ構成データで演算スイッチ・データを更新することでスイッチ部を再構成するように動作する。 (もっと読む)

プログラマブルロジックデバイスおよびそれを用いた信号処理回路

【課題】電源が遮断されても機能を維持可能なPLDを提供する。

【解決手段】リコンフィギュアラブル回路10は、その回路形態がコンフィギュレーションデータCONFに応じて設定される。コンフィギュレーションメモリ20は、リコンフィギュアラブル回路10と付随して設けられ、リコンフィギュアラブル回路10のコンフィギュレーションを設定するコンフィギュレーションデータCONFを保持する。コンフィギュレーションメモリ20は、コンフィギュレーションデータCONFの各データを保持する複数のメモリセルを含む。各メモリセルは、フリップフロップFFと、対応するフリップフロップの状態を保持する不揮発性メモリMnvを含む。複数のメモリセルのフリップフロップは、デイジーチェインを構成するように直列に接続され、コンフィギュレーションデータCONFが、当該デイジーチェインを経由してロード可能に構成されている。

(もっと読む)

相変化メモリデバイスを有する分圧器を含む不揮発性メモリ回路

第一相変化メモリ(PCM)デバイス、および第一PCMデバイスに結合された第二PCMデバイスを有する分圧器を含むメモリ回路を記述する。1つの実施形態では、第一PCMデバイスはセット抵抗の状態にあり、第二PCMデバイスはリセット抵抗の状態にある。また、1つの実施形態では、分圧器は、更に、第一PCMデバイスに接合された第一スイッチ、ならびに第一スイッチおよび第二PCMデバイスに結合された第二スイッチを含む。1つの実施形態では、メモリ回路は、更に、分圧器に結合されたハーフラッチ、ならびにハーフラッチおよび分圧器に結合されたカスケードトランジスタを含む。  (もっと読む)

(もっと読む)

コンフィギュレーション方法及びコンフィギュレーション装置並びにコンフィギュレーションプログラム

【課題】 部品点数や冗長ビット数の大幅な増加をともなわずに、プログラマブルデバイスの数やベンダーの種類の増加に対応できるコンフィギュレーション方法及びコンフィギュレーション装置並びにコンフィギュレーションプログラムを提供することを課題とする。

【解決手段】 本コンフィギュレーション方法は、制御部の各ポートに接続された複数のプログラマブルデバイスに転送する複数のコンフィギュレーションデータを、不揮発性メモリのビット列単位で割り当て、前記ビット列の先頭に前記ポート別識別情報を付与し、前記不揮発性メモリに格納するデータ格納ステップと、前記不揮発性メモリに格納された前記複数のコンフィギュレーションデータを、制御部の各ポートに接続された対応するプログラマブルデバイスに転送するデータ転送ステップと、を有することを要件とする。

(もっと読む)

相互接続構造および論理回路装置

【課題】外部配線と複数の論理セルを含む論理セル群とを相互に接続する相互接続構造、および相互接続構造を有する論理回路装置に関し、論理のファンクション表現の柔軟性を低下させることなく配線リソースのオーバヘッドを低減させることを目的とする。

【解決手段】論理回路装置における相互接続部1が、外部配線と論理セル群2の入力線と相互接続関係を規定する接続規定手段を有し、論理セル群の複数の論理セルの中で対象となるファンクションを考慮して、論理のファンクション表現に関する柔軟性を保ちつつ、相互接続部の入力線の数が相互接続部の出力線の数より少ない構成、および、接続規定手段により規定される組み合わせ数が相互接続部の入出力の全ての組み合わせ数より少ない構成の少なくとも一方が実現されるように構成される。複数の論理回路装置のクラスタ化により形成されるクラスタ構造を有する論理回路装置も提供される。

(もっと読む)

カウント装置

【課題】 カウント入力回路への被カウント信号配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とする。

【解決手段】 入力回路(11−1〜4)の各出力端とカウンタ(13−1〜4)の各入力端との間には分配切替回路(12)が介在され、分配切替回路は、入力回路の各出力端のそれぞれに接続される入力側端子(IN0〜IN1)と、カウンタの各入力端のそれぞれに接続される出力側端子(OUT1〜OUT4)とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされる。

(もっと読む)

半導体集積回路

【課題】機能を柔軟に制御可能なアナログの機能ICを提供する。

【解決手段】アナログブロック10は、所定のアナログ信号処理を実行する。デジタルブロック20は、再構成可能に構成され、所定のデジタル信号処理を実行してアナログブロック10を制御する。FeRAM30は、デジタルブロック20の回路構成のコンフィギュレーションデータを格納する。機能IC100は、FeRAM混載プロセスを用いてひとつの半導体基板上に一体集積化され、アナログブロック10の動作状態が、デジタルブロック20の構成状態に応じて変更可能である。

(もっと読む)

プログラマブル配線の電源を安全にオンする方法および装置

【課題】プログラマブル配線を安全、単純かつスケーラブルな方法で電源をオンする、より良い方法およびデバイスを提供する。

【解決手段】プログラマブル配線のロード線を交差するプログラマブル配線の複数のドライバ線に接続する方法および装置であって、プログラマブル配線のロード線を交差する関連のドライバ線に接続するよう操作可能である接続セルを有し、この接続セルは、接続信号を受け取るために設けられた接続信号受け取り手段と、アクティベーション信号を受け取るために設けられたアクティベーション信号受け取り手段とを備える。さらに、プログラマブル配線のロード線を、プログラマブル配線の交差する関連のドライバ線に接続するために設けられた接続手段、一連のセルの次のセルへアクティベーション信号を伝播するアクティベーション信号伝播手段を備える。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

半導体集積回路

【課題】回路構成を再構成可能であって、パイプライン処理と逐次処理を同時に且つ効率良く実行可能な半導体集積回路を提供する。

【解決手段】外部プログラムのデコード結果に応じて回路構成を再構成可能な複数の処理部を備えた半導体集積回路にて、内部プログラムを記憶する第1処理部、内部プログラムの命令をデコードして制御信号を生成する第2処理部、制御信号を受けて処理を行う第3処理部、第1の記憶領域と第2の記憶領域を有する第4処理部を備え、第1動作モードでは、第4処理部の一方の記憶領域は第1〜第4処理部からなる第1のネットワーク構成に接続されて第3処理部の処理結果を保持し、他方の記憶領域は第2のネットワーク構成に接続されるようにして、第1及び第2のネットワーク構成により逐次処理及びパイプライン処理をそれぞれ実行でき、かつ第4処理部を同時にアクセスできるようにする。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

61 - 80 / 269

[ Back to top ]