Fターム[5J042BA11]の内容

論理回路 (4,317) | 論理回路の種類 (1,203) | 構成要素がマトリックス状に配置されたもの (595) | PLA (556) | 再プログラムが可能なもの (269)

Fターム[5J042BA11]に分類される特許

21 - 40 / 269

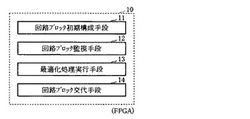

FPGA、FPGAを用いた回路再構成システム、方法およびプログラム

【課題】回路の一部に不具合が生じて新たな回路を同一基板内に再構成する場合に、この新たな回路との関係で伝送される信号のタイミングに不具合が生じないようにすることが可能なFPGA、FPGAを用いた回路再構成システム、方法およびプログラムを得ること。

【解決手段】回路ブロック監視手段12が回路ブロックを構成する論理部に不具合があることを検出すると、これに代わる新しい回路ブロックを構成するとき最適化処理実行手段13は論理部同士を接続する接続部による信号の伝達タイミングを前の回路ブロックの接続部と可能な限り同一になるように最適化する。回路ブロック交代手段14は新しい回路ブロックの運用を開始させる。

(もっと読む)

スピンMOSFETを用いたメモリ回路、メモリ機能付きパストランジスタ回路、スイッチングボックス回路、スイッチングブロック回路、およびフィールドプログラマブルゲートアレイ

【課題】高速、不揮発性、低消費電力のメモリ回路を提供する。

【解決手段】一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFET10と、一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFETもしくは第1導電型のMOSFET12と、ノード40にゲート電極が接続され一方のソース/ドレイン電極が出力端子37に接続されたpチャネルスピンMOSFETもしくはpチャネルのMOSFET14と、ノード40にゲート電極が接続され、一方のソース/ドレイン電極が出力端子37に接続されたnチャネルスピンMOSFETもしくはnチャネルのMOSFET16と、出力端子37と、を備え、第3トランジスタ14と第4トランジスタ16はインバータ回路を構成し、第3トランジスタ14および第4トランジスタ16の少なくとも一方がスピンMOSFETであり、出力端子37からインバータ回路が出力される。

(もっと読む)

半導体集積回路

【課題】 消費電力を削減した半導体集積回路を提供すること。

【解決手段】 本発明の実施形態による半導体集積回路は、第1の電源と第2の電源との間に2つの不揮発メモリと複数のスイッチング素子が接続されたメモリセルを複数含む半導体集積回路であって、少なくとも2つの前記メモリセルの出力配線が接続され、出力配線が接続されたメモリセルに含まれるスイッチング素子の制御ゲートに入力信号もしくはこの入力信号の反転信号が入力されて、出力配線が接続されたメモリセルの少なくとも1つのメモリセルに含まれる前記入力信号もしくはこの入力信号の反転信号が入力されたスイッチング素子が非導通となり、少なくとも1つのメモリセルに含まれる前記入力信号もしくはこの入力信号の反転信号が入力されたスイッチング素子が導通する。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

リコンフィギュラブルロジックブロック、並びに、これを用いたプログラマブル論理回路装置、及び、テクノロジマッピング方法

【課題】デバイスの小面積化と低消費電力化を実現することが可能なリコンフィギュラブルロジックブロック、並びにこれを用いたプログラマブル論理回路装置、及び、テクノロジマッピング方法を提供する。

【解決手段】最大K入力(x[0]〜x[K−1])のリコンフィギュラブルロジックブロック(K−A2LUT)は、m入力(y[0]〜y[m−1]、ただしmはKよりも小さくyはxに属する)の第1ルックアップテーブル1と、n入力(z[0]〜z[n−1]、ただしnはKよりも小さくzはxに属する)の第2ルックアップテーブル2と、p入力(c[0]〜c[p−1]、ただしpはKよりも小さくcはxに属する)の組み合わせ回路3と、組み合わせ回路3の出力に応じて第1ルックアップテーブル1と第2ルックアップテーブル2のいずれか一方を選択するセレクタ4と、を有する。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

情報処理装置

【課題】集積回路の回路情報を記憶するメモリの書き換えを行う際に、電源遮断等の異常が発生しても安全に元の状態に復旧する。

【解決手段】FlashROM2は、装置全体の電源を投入した際にFPGA1より読み出される回路情報が格納される第1の領域と、第1の領域の回路情報とは異なる回路情報を格納される第2の領域とを有し、装置全体の電源を投入した際は、FPGA1はFlashROM2の第1の領域から回路情報を読み出し、この回路情報によりFPGA1内部の回路を構成し、FlashROM2の第2の領域に正常な回路情報が格納されていることを検査し、正常な回路情報が格納されていると判断した場合は、FlashROM2のアドレスを変更する手段により、アドレスを変更し、FPGA1の回路情報の更新を行うことで、FlashROM2の第2の領域から回路情報を読み出し、この回路情報によりFPGA1内部の回路を構成し、プロセッサ5のリセットを解除する。

(もっと読む)

画像処理システム

【課題】異常が発生した場合に、より確実に正常な状態に復帰することができる画像処理システムを提供する。

【解決手段】FPGA2は、FPGA1の異常を検出する異常監視部を搭載する。コンフィグレーション制御部19は、FPGA2の異常監視部がFPGA1の異常を検出した場合に、FPGA1を使用せずに画像処理を行うため、FPGA1以外のFPGAに対して、FPGA1の通常のコンフィグレーション時に使用する回路情報とは異なる回路情報を用いて再コンフィグレーションを行う。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

プログラム可能なロジックデバイスの性能特性を調整する装置と方法

【課題】供給電圧及び電力消費を調整すること。

【解決手段】プログラム可能なロジックデバイス(programmable logic device){ピーエルデー(PLD)}は該ピーエルデー内の回路の少なくとも1部分(ブロック、サブブロック、又は領域の様な)の供給電圧を制御する回路を有する。該回路は又該ピーエルデー内のノイズをフイルターする。該供給電圧を制御することは、速度及び電力消費の様な、種々の性能特性をトレードオフすることを可能にする。

(もっと読む)

再構成可能な論理装置

【課題】再構成可能な論理装置を提供する。

【解決手段】第1論理ブロックと、第2論理ブロックとを含む少なくとも2つの論理ブロック;第1論理ブロックに連結される複数の第1グローバル配線と、前記第2論理ブロックに連結される複数の第2グローバル配線と、を含むグローバル配線グループ;複数の第1グローバル配線と、複数の第2グローバル配線とが交差する領域にそれぞれ配される複数の第1不揮発性メモリ素子を含み、論理装置の動作をリアルタイムで再構成するために、複数の第1不揮発性メモリ素子それぞれに保存された第1データを基に、複数の第1グローバル配線及び第2グローバル配線のルーティングを制御するグローバル制御部;を含む再構成可能な論理装置である。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

プログラマブル論理回路装置およびその回路決定方法

【課題】論理回路の冗長性を排除することで、面積効率を高めることが可能なプログラマブル論理回路装置およびその回路決定方法を提供することを目的とする。

【解決手段】プログラマブル論理回路は、構成データによる回路変更および配線スイッチ部による配線の入れ替えにより、一の論理関数を実現するゲート回路を、該一の論理関数とNPN同値類に属する他の論理関数のみを実現するゲート回路と共通させている。この回路変更は、N操作のためのプログラマブルNOTゲートによる入力反転部と、2入力NANDゲートまたは2入力ORゲートが、二分木の木構造で、それぞれの接続線の間にプログラマブルNOTゲートを介在させて接続された基本回路と、N操作のためのプログラマブルNOTゲートによる出力反転部とに、構成データを与えることにより行う。

(もっと読む)

集積回路

【課題】ユーザによってプログラミング可能な集積回路を複数用いるシステムの設計・検証期間を短縮する。

【解決手段】集積回路であるフィールド・プログラマブル・ゲートアレイ1は、外部からユーザによってプログラミング可能な論理回路である処理ブロック2と、外部からの入力データI1a,I1bを内部クロックCKでリタイミングするFIFOレジスタ3−1,3−2と、処理ブロック2の出力データとFIFOレジスタ3−2の出力データのうちどちらか一方を選択して外部に出力するセレクタ4−1と、処理ブロック2の出力データとFIFOレジスタ3−2の出力データのうちどちらか一方を選択して入力データとして処理ブロック2に入力するセレクタ4−2とを有する。

(もっと読む)

半導体装置

【課題】プログラム可能な半導体装置において、クロック周波数を保証しつつ、複数の演算命令の組み合わせで形成される演算処理を効率的に実行できる。

【解決手段】本開示の一実施形態は、一定のクロック信号に同期して演算を行う半導体装置であって、演算制御情報を出力する制御部13と、データを記憶する記憶部11と、第1のデータに対して第1の演算制御情報に従い演算を行う演算ユニット100と、第2のデータに対して第2の演算制御情報に従い演算を行う演算ユニット101とを備える。演算ユニット100は、演算回路を複数個備える。演算ユニット101は、論理ゲート段数n(n>m)の演算回路を少なくとも1個備える。

(もっと読む)

スピンMOSFETおよびリコンフィギャラブルロジック回路

【課題】スピンMOSFETのソース/ドレイン領域におけるMTJの強磁性体に垂直磁化膜を用いても、隣接トランジスタへの漏れ磁界による影響を抑制し、シフト調整を可能にし、チャネル領域中のスピン緩和を抑制するスピンMOSFETを提供する。

【解決手段】下地層65の上に設けられた磁化の向きが膜面に垂直でかつ不変な第1強磁性層72と、第1強磁性層72上に設けられたチャネルとなる半導体層74と、半導体層74上に設けられた、磁化の向きが膜面に垂直でかつ可変な第2強磁性層78と、第2強磁性層78上に設けられたトンネルバリア80と、トンネルバリア80上に設けられた、磁化の向きが膜面に垂直かつ不変で第1強磁性層72の磁化の向きと反平行な磁化の向きを有する第3強磁性層82と、半導体層74の側面に設けられたゲート絶縁膜90aと、半導体層74と反対側に位置するように設けられたゲート電極76と、を備えている。

(もっと読む)

プログラマブル論理回路装置及び画像処理装置

【課題】 節電効率を向上させることができるプログラマブル論理回路装置及び画像処理装置を提供する。

【解決手段】 本発明のプログラマブル論理回路装置100は、素子間の接続の変更により再構成される回路を備える複数の再構成領域R0−R5と、複数の再構成領域R0−R5の各々に対して、実行させる処理を割り当てて、複数の再構成領域R0−R5の各々が実行する処理の状態に基づいて、複数の再構成領域R0−R5を選択的に再構成して節電状態にする管理領域R0及びR5と、管理領域R0及びR5が複数の再構成領域R0−R5を選択的に再構成するタイミングを調整する同期管理部22及び42と、を備える複数のプログラマブル論理回路部50及び60を有し、同期管理部22は、他の同期管理部42と同期して、タイミングを調整する。

(もっと読む)

21 - 40 / 269

[ Back to top ]