Fターム[5J042CA28]の内容

Fターム[5J042CA28]に分類される特許

1 - 20 / 35

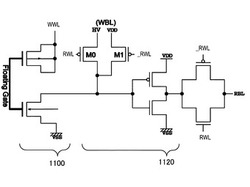

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源遮断後の起動時間が短く、高集積化及び低消費電力化を図ることが可能であるプログラマブルロジックデバイスを提供する。

【解決手段】入出力ブロックと、論理エレメントを有する複数の論理ブロックと、該複数の論理ブロックを接続する配線とを有するプログラマブルロジックデバイスにおいて、論理エレメントは、コンフィギュレーションデータが保持されたコンフィギュレーションメモリ及び選択回路を有するルックアップテーブルを有する。また、コンフィギュレーションメモリは、酸化物半導体膜をチャネル領域に有するトランジスタと、該トランジスタ及び選択回路の間に設けられた演算回路とを有するメモリ素子を複数有し、入力信号に応じて選択回路によりコンフィギュレーションデータを選択的に切り替えて出力する。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後の論理ブロックの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】プログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

多値ハザード除去回路

【課題】ディジタル信号から多値ハザードを除去する。

【解決手段】トランジスタ1、2、17と抵抗20、21が構成する多値判別手段、この判別手段の出力信号に基づいて動作するトランジスタ22〜25とダイオード36が構成するオン・オフ駆動手段、及びこのオン・オフ駆動手段がオン・オフ駆動するトランジスタ3、5が構成する双方向性プル・スイッチング手段、が『フージ(Hooji)代数』を具体化した1多値論理回路を構成する。この多値論理回路、プル・ダウン用抵抗26及びD型フリップ・フロップ27の入力部に有る2値判別手段の組合せが、多値信号を2値信号に変えると同時に多値ハザードを2値ハザードに変える。同期信号により制御されたD型フリップ・フロップ27がその2値ハザードを除去した2値信号を出力する。

(もっと読む)

半導体集積回路、半導体集積回路の構成変更方法

【課題】再構成可能デバイスの回路面積を縮小する。

【解決手段】 本発明による半導体集積回路は、複数の機能ブロック10と、複数の構成情報が格納された複数の構成情報メモリ11と、自身に入力される構成情報に応じたスイッチング動作によって、機能ブロック10間の接続を制御する複数のプログラマブルスイッチ12、13とを具備する。複数のプログラマブルスイッチ12、13は、複数の構成情報メモリ11のうち、共通の構成情報メモリ11内に格納された構成情報を利用する。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

走査駆動部及び有機電界発光表示装置

【課題】PMOSトランジスタのみで論理和を実現することのできる論理ゲートを提供する。

【解決手段】本発明の論理ゲートは、複数の入力信号に対応して第1ノードN1の電圧を制御する第1駆動部10と、第1ノードN1の電圧値を制御する第2駆動部12と、第1ノードN1に印加される電圧値に対応して第1電源VDDと出力端子Voutとの接続要否を制御する第3駆動部14と、第3駆動部14と第2電源VSSとの間に接続される制御トランジスタM8と、制御トランジスタM8のゲート電極と第2電源VSSの接続要否を制御する第4駆動部16とを具備し、第1駆動部〜第4駆動部を構成するトランジスタ及び制御トランジスタM8はPMOSのみで形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】従来のプログラマブルな半導体装置であるFPGAやMPLDはコストパフォーマンスが悪く、かつ長い信号線に対する配慮が不充分であった。

【解決手段】メモリと、アドレス−データ対を有する複数のMLUTから構成されるMLUTブロックにフリップフロップを内蔵した。また隣接するMLUT間の近距離配線には交互配置配線を導入し、隣接していないMLUT間の配線には専用の離間配線、更にはトーラス配線網を設けた。

(もっと読む)

ルックアップテーブル、半導体集積回路、ルックアップテーブルの製造方法、および半導体集積回路の製造方法

【課題】製造が容易で集積度が高く動作の速い低廉なルックアップテーブルを短期間で開発すること。

【解決手段】

ルックアップテーブル200は、入力端子101と、出力端子102と、入力端子101の個数により決定される入力パターン数に対応したビア挿入箇所と、トランジスタにより構成される選択回路と、プリチャージ回路とを備える。ビア挿入箇所は、単一のビア層が有している。ビア挿入箇所の中から組合せ回路に応じてビアが挿入され、挿入されたビアを介して入力端子101と出力端子102とが接続される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応している場合、出力端子102にはVSSが出力される。入力端子101に入力される入力パターンが、ビアが挿入されたビア挿入箇所に対応していない場合、出力端子102にはプリチャージ回路によりVDDが出力される。

(もっと読む)

相変化メモリデバイスを有する分圧器を含む不揮発性メモリ回路

第一相変化メモリ(PCM)デバイス、および第一PCMデバイスに結合された第二PCMデバイスを有する分圧器を含むメモリ回路を記述する。1つの実施形態では、第一PCMデバイスはセット抵抗の状態にあり、第二PCMデバイスはリセット抵抗の状態にある。また、1つの実施形態では、分圧器は、更に、第一PCMデバイスに接合された第一スイッチ、ならびに第一スイッチおよび第二PCMデバイスに結合された第二スイッチを含む。1つの実施形態では、メモリ回路は、更に、分圧器に結合されたハーフラッチ、ならびにハーフラッチおよび分圧器に結合されたカスケードトランジスタを含む。  (もっと読む)

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

プログラマブル配線の電源を安全にオンする方法および装置

【課題】プログラマブル配線を安全、単純かつスケーラブルな方法で電源をオンする、より良い方法およびデバイスを提供する。

【解決手段】プログラマブル配線のロード線を交差するプログラマブル配線の複数のドライバ線に接続する方法および装置であって、プログラマブル配線のロード線を交差する関連のドライバ線に接続するよう操作可能である接続セルを有し、この接続セルは、接続信号を受け取るために設けられた接続信号受け取り手段と、アクティベーション信号を受け取るために設けられたアクティベーション信号受け取り手段とを備える。さらに、プログラマブル配線のロード線を、プログラマブル配線の交差する関連のドライバ線に接続するために設けられた接続手段、一連のセルの次のセルへアクティベーション信号を伝播するアクティベーション信号伝播手段を備える。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

1 - 20 / 35

[ Back to top ]