Fターム[5J049AA20]の内容

Fターム[5J049AA20]に分類される特許

1 - 19 / 19

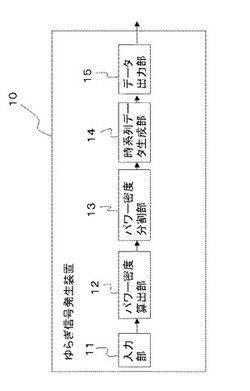

ゆらぎ信号発生装置、ゆらぎ信号発生方法、及びゆらぎ信号発生プログラム

【課題】様々な傾きを有したゆらぎを発生させるとともに、人の要求する山場(ピーク)位置もある程度設定できるゆらぎ信号発生装置を提供する。

【解決手段】ゆらぎ信号発生装置10は、パワー密度を算出する関数とパワー密度を算出する関数のパラメータを入力する入力部11と、入力部によって入力されたパラメータとパワー密度を算出する関数に基づいて、各周波数のパワー密度を算出するパワー密度算出部12と、パワー密度算出部によって算出された各周波数のパワー密度を正弦波成分と余弦波成分に分けるパワー密度分割部13と、パワー密度分割部によって分割された成分に基づいて逆フーリエ変換により時系列データを生成する時系列データ生成部14と、時系列データに基づいて出力データを生成し出力するデータ出力部15と、を備えた。

(もっと読む)

物理乱数生成装置及び物理乱数生成回路

【課題】方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供する。

【解決手段】出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備する。ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から前回サンプリングされた値を差し引いた値が乱数値として出力され、真正度の高い乱数が得られる。

(もっと読む)

周波数シンセサイザ

【課題】不要波成分を確実に抑圧することのできる周波数シンセサイザを得る。

【解決手段】クロック信号源1と、クロック信号Cのクロック周波数において互いに90度位相差となる第1および第2のクロック信号C1、C2に電力分配する90度電力分配回路12と、クロック信号Cに同期して、外部からの制御信号kに応じた第1および第2のデジタル信号A1、A1を生成するデジタル振幅データ生成回路50と、第1のクロック信号C1に同期して、第1のデジタル信号A1に応じた第1のアナログ信号B1を生成するDAC10と、第2のクロック信号C2に同期して、第2のデジタル信号A2に応じた第2のアナログ信号B2を生成するDAC11と、第1および第2のアナログ信号B1、B2を合成する合成回路13とを備えている。

(もっと読む)

物理乱数生成装置

【課題】

物理乱数発生源から取り出したデジタルデータとしての物理素乱数から複数個の物理乱数を高速に生成する。

【解決手段】

ホワイトノイズを発生させる物理乱数発生源と、前記ホワイトノイズを入力してデジタルデータとしての物理素乱数に変換するアナログ・デジタル変換機構と、前記物理素乱数を複数個入力して物理素乱数配列を生成する物理素乱数配列生成機構と、前記物理素乱数配列を入力してホワイトノイズ配列を生成するホワイトノイズ配列生成機構と、前記ホワイトノイズ配列を入力して複数の物理乱数を生成するホワイトノイズ合成機構と、前記生成された複数の物理乱数を入力して物理乱数データとして外部に出力する外部出力インターフェースとを有する。

(もっと読む)

データ生成装置

【課題】任意のワード長の並列データを生成できるようにする。

【解決手段】波形メモリ66は、Mビット並列データから構成されるデータ列を記憶する。シーケンス・メモリ60は、シーケンス情報と、データ列中の最後のデータからいくつのデータを破棄するかを示すデータ破棄情報とを記憶する。シーケンス62と波形メモリ制御回路64は、シーケンス情報を用いて波形メモリ66からデータ列を読み出す。バレル・シフタ68は、データ破棄情報に基づくデータ廃棄又はデータ・シフトによってデータ列の最後の並列データの有効なビット数がM−Jとなる場合に、そのデータ列の次のデータ列中のデータをJビットだけシフトする。データ・シフト制御回路は、データ・シフト及びデータ破棄情報に基づいてデータ列中のデータの有効又は無効を示すデータ・イネーブルを生成する。結合回路72は、データ・イネーブルを用いて、データ列の有効なデータを結合する。

(もっと読む)

ワンダ発生装置及びディジタル回線試験装置

【課題】簡易な構成で所望のワンダを有する信号を発生することができるワンダ発生装置、及び当該ワンダ発生装置を備えるディジタル回線試験装置を提供する。

【解決手段】ワンダ発生装置1は、ダイレクトディジタルシンセサイザ(DSS)14に発生させる信号の中心周波数を規定するデータを設定する周波数設定部11と、所定のワンダを発生させるためのワンダデータを記憶するワンダメモリ12と、周波数設定部11で設定されたデータとワンダメモリ12から読み出されたワンダデータとを加算する加算器13と、加算器13の加算結果を用いて所定周波数の信号を出力するDSS14とを備える。

(もっと読む)

物理乱数生成装置及び物理乱数生成回路

【課題】方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供する。

【解決手段】出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備する。ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から前回サンプリングされた値を差し引いた値が乱数値として出力され、真正度の高い乱数が得られる。

(もっと読む)

パルス幅変調回路

【課題】、三角波信号の周期が離散的に変化されるにもかかわらず、該周期を時間的基準として活用することが可能なパルス幅変調回路を提供することにある。

【解決手段】

コンデンサ(CT)の充放電電流によって規定される周期をもつ一定振幅の三角波信号を発生する三角波発生手段(11)と、三角波信号に同期するタイミングでコンデンサ(CT)の充放電電流を基準電流値から離散的に変化させる電流変調手段(13)と、三角波信号と被変調信号とを比較することによってパルス幅変調信号を発生する比較手段(12)と、を備える。電流変調手段(13)は、三角波信号の連続する2周期の一方および他方の周期に対して等しい値の離散的変化成分を割り当てるとともに、離散的変化成分を一方および他方の周期においてそれぞれ基準電流値に加算および減算するように構成される。

(もっと読む)

乱数発生器

【課題】アナログ入力信号から導き出され、かつ高いエントロピを有するディジタル出力信号を生成できる乱数発生器を提供する。

【解決手段】シグマデルタ変調器を備え、このシグマデルタ変調器は、第1電圧範囲全体にわたってノイズに起因して変化するアナログ入力信号を受け取り、この信号に調節信号を加算して加算出力信号を形成し、この信号を受け取って、その信号に応じてフィルタ処理済み出力信号を生成し、この信号を受け取り、この信号を量子化器しきい値と比較し、比較結果に応じてディジタル出力信号の2つの所定の電圧レベルの一方を選択することによってディジタル出力信号を形成し、ディジタル出力信号を受け取り、任意の所与の瞬時においてこの信号に応じて調節信号を生成することにより、加算出力信号の振幅と量子化器しきい値との間の絶対差が第1電圧範囲よりも小さくなるようにする。

(もっと読む)

連続時間カオスを使用した乱数の発生

連続時間カオス振動子に基づく新規乱数発生方法、及び乱数発生器(RNG)が提示される。出力列の統計的品質を最大限に高めるため、及びパラメータ変動やアタックに対して強固にするため、オフセットと周波数の補正ループが付加される。一次セクションが分布に応じて領域に分割される場合、発生ビット列はFIPS‐140‐2とNIST800‐22統計的テスト一式の両方で使用されるテストを後処理なしでパスすることを、我々は数値的及び実験的の両方で証明している。この新手法で提示される数値的及び実験的結果は提案の回路の実現可能性を証明するだけでなく、高性能IC‐RNGの核としてのその使用も促す。離数時間カオス地図、ノイズソースの増幅、及び振動子ジッタサンプリングに基づくRNGを比較して、連続時間カオス振動子に基づくRNGは、後処理なしに、非常に速く、かつ一定のデータ速度を提供できることが分かる。結論として、我々は、提案の回路は集積回路で実現することが可能であり、提案の新手法で連続時間カオスを利用することは、非常に高いスループットで乱数を発生させることにおいて非常に有望であることを予測することができる。 (もっと読む)

パルス信号生成回路

【課題】パルス信号生成回路において、スペクトラム拡散変調とパルス幅変調とを共に実現する。

【解決手段】擬似乱数発生回路10から出力されたデジタルランダム信号S0をD/A変換回路20によりアナログランダム電圧信号S1に変換する。加算器30は、信号S1と中心周波数設定電圧S2とを加算し周波数制御電圧信号S3を出力する。鋸波生成回路40は、信号S3に対応して周波数が変動する鋸波電圧を生成する。コンパレータ50は、鋸波電圧S4とデューテイ比設定電圧S5との大小に応じたパルス信号S6を出力する。このパルス信号S6は、デューテイ比設定電圧に対応するデューテイ比を有し、周波数制御電圧信号S3に対応して周波数が変動する。

(もっと読む)

乱数生成装置及び乱数生成方法

【課題】物理的条件や製造誤差によっても周期性を有さない乱数生成を行う。

【解決手段】抵抗とコンデンサとコイルと非線形受動素子とが接続されて発振回路を構成すると共に、前記抵抗とコンデンサとコイルの内少なくとも1素子の値を可変する素子値変更手段を備えたアナログカオス回路10と、前記アナログカオス回路10へ入力信号を供給する信号源20と、前記アナログカオス回路10の出力を所定周期にて取り出しディジタル化して下位側所定ビットを抽出する抽出部30と、前記抽出部30により抽出された所定回分のビットを並べて乱数とする乱数構成部40と、前記抽出部30の抽出周期に同期して前記素子値変更手段を制御し、素子値の変更を行う変更制御手段50とを具備する。

(もっと読む)

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

半導体集積回路

【課題】 スイッチ回路によりデジタル信号のビット番号をランダムに入れ替える。

【解決手段】 スイッチ回路SWCは、デジタル入力信号INのビット番号を選択信号SELに応じて順次シフトし、デジタル出力信号OUTとして出力する。スイッチ制御回路SCNTは、ランダムな値に変化するシフト信号SFTを受け、ビット番号とシフト信号SFTが示す値とを演算することで次のビット番号を生成し、生成したビット番号を選択信号SELとして順次出力する。スイッチ制御回路SCNTによりランダムなビット番号が生成されるため、スイッチ回路SWCは、デジタル入力信号INのビット番号を規則性のないランダムな順序でシフトしてデジタル出力信号OUTとして出力できる。デジタル出力信号OUTをD/A変換部DAPに供給することで、D/A変換の精度を向上できる。

(もっと読む)

ドライブパルス列を供給するドライブ回路およびドライブパルス列の供給方法

【課題】ライブパルス列をフレキシブルに形成するドライブ回路を提供する。

【解決手段】マトリクス素子を備えたスイッチングマトリクスが設けられており、マトリクス素子は期間のうちの少なくとも1つと、少なくとも1つの制御パラメータからなるただ1つの組にその都度割り当てられており、n個のパルス発生器のうちの1つの丁度1つのスイッチング素子に対する制御信号を出力する。

(もっと読む)

パルス駆動型ジョセフソン波形発生方法及び発生回路

【課題】 ジョセフソン接合素子をパルス駆動し、大出力と精度を同時に実現して任意波形を発生させるパルス駆動型ジョセフソン波形発生方法および装置を提供するものである。

【解決手段】 入力バルスとして、従来の波形を時間軸でみて主として一つの大きな尖頭値を有する波から構成され、かつ波の最大値と最小値の比が大きく、周波数軸でみて出力波形の周波数と重畳しない領域の二つの周波数f1およびf2で規定される幅を持つ波形で置き換えることにより、任意信号出力においても波形精度を高める。換言すると、入力信号(最終的に出力させたい信号)が波形発生回路に残っていると、この入力信号が途中の回路素子に作用して変化した信号が最終的に出力に現れ、欲しい信号のみが出力されなくなる場合が発生する。これをなくすために、周波数スペクトル上で入力信号成分を除いた信号を使って最終出力を得る。

(もっと読む)

波形発生装置

【目的】 外部から入力したトリガ信号に応じて任意の波形データを優先順位の高い方から順次出力する波形発生装置を提供する。

【構成】 外部入力制御部11からトリガ信号が入力されると、このトリガ信号と、現在出力している波形データとの優先度を比較し、現在出力している波形データの方がトリガ信号よりも優先度が高い場合は、状態遷移制御部2にトリガ信号が一旦記憶され、現在出力している波形データの出力が完了した後、トリガ信号に応じた波形データに切り替えて出力する。現在出力している波形データの方がトリガ信号よりも優先度が低い場合は、現在出力している波形データの出力を停止し、トリガ信号に応じた波形データに切り替えて出力する。

(もっと読む)

複合ノイズ発生器

【課題】 任意の特性を有する複合ノイズを容易にかつ安定して生成可能とする複合ノイズ発生器を提供する。

【解決手段】 予めガウス性ノイズ信号の波形データを任意のエンベロープ波形で選択的に発生するためのゲートが組み込まれ、外部からのパラメータによって波形データの特性を任意に制御可能とするFPGA11を備える。このFPGA11を制御用コンピュータ12によってパラメータ制御することで複合ノイズの波形データを発生し、D/A変換器13によってアナログ信号に変換出力する。ノイズのパラメータとして、平均電力、時間率の振幅確率分布(タイムベースAPD)、交差率分布(CRD)、継続時間分布(BDD)、発生頻度分布(OFD)、およびエンベロープ信号波形を任意に選択可能とした結果、プログラムによる自動的な制御が可能となる。

(もっと読む)

乱数発生器のための方法および装置

乱数を発生するための方法および装置が開示されている。一つの観点において、無線通信装置中での使用のための乱数を発生する方法は、乱数を発生し、その発生した乱数のサンプルを収集し、平均値、標準偏差および、またはエントロピーのような少なくとも1つのメトリックを計算する。その方法はさらに、そのメトリックを対応する基準値と比較し、その発生した乱数が所望の分布を達成するように前記比較の結果に基づいてメトリックを調整する。別の観点において、乱数を発生する装置は、乱数を調整するためにフィードバック値および乱数を発生するハードウェアコンポーネントおよびアナログ雑音発生器を備えている。その装置はさらに、乱数を調整するための制御アルゴリズムを行わせる命令を実行することのできるプロセッサを備えている。 (もっと読む)

1 - 19 / 19

[ Back to top ]