Fターム[5J055AX10]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | スイッチの基本性能向上 (933) | 駆動能力の制御 (142) | スルーレートを制御できるもの (75)

Fターム[5J055AX10]に分類される特許

1 - 20 / 75

半導体装置

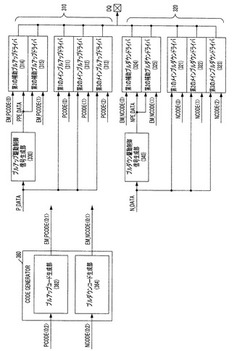

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

スイッチング素子の駆動装置及びスイッチング素子の駆動方法

【課題】スイッチング損失の増大を抑制しつつ、より高い周波数帯で発生するスイッチングノイズを抑制できるスイッチング素子の駆動装置を提供する。

【解決手段】スルーレート調整部は、NチャネルMOSFETを介してDCモータに出力される電圧波形のスルーレートを変化させ、キャリア周波数によって決まる周波数帯よりも高い周波数帯域に現れるスイッチングノイズの周波数成分を分散させてピークレベルを低下させる。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

スイッチング回路

【課題】電力効率を低下させずに高速動作可能なスイッチング回路を提供する。

【解決手段】スイッチング回路は、入力電圧を第1の電圧に変換する第1のDC/DCコンバータB1と、制御信号に応じて第1の電圧を出力するか否か切り替える第1のスイッチ回路C1と、第1のスイッチ回路からの電圧の過渡特性を制御する第1の制御回路D1と、高圧側電源に一端が、出力端子に他端が接続され、第1の制御回路からの電圧に応じてオンオフされる第1の能動素子A1と、入力電圧を第2の電圧に変換する第2のDC/DCコンバータB2と、制御信号に応じて第1のスイッチ回路とは相補的に第2の電圧を出力するか否か切り替える第3のスイッチ回路C3と、第3のスイッチ回路からの電圧の過渡特性を制御する第2の制御回路D2と、出力端子に一端が、低圧側電源に他端が接続され、第2の制御回路からの電圧に応じてオンオフされる第2の能動素子A2とを備える。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

半導体装置

【課題】ドライブ能力およびスルーレートを調節可能な出力ドライバを備え、従来よりも微細化することができる半導体装置を提供する。

【解決手段】半導体装置は、コア回路から転送されるデジタルデータを出力するために複数のサブドライバを含む出力ドライバODと、サブドライバを選択するセレクタとを備える。各サブドライバは、デジタルデータに従って出力データを立ち上げまたは立ち下げるために、第1の電源PS1と出力配線WOUTとの間に接続された出力トランジスタTP30と、出力トランジスタTP30のゲートと第2の電源VSSとの間に直列に接続されたスイッチングトランジスタTN33およびスルーレート調整トランジスタTN34とを備える。各スルーレート調整トランジスタTN34は、出力データの立ち上がりまたは立ち下がりのスルーレートを決定するために調整されたゲート電位をセレクタによって選択的に与えられる。

(もっと読む)

負荷駆動装置の製造方法

【課題】負荷駆動装置において負荷を駆動するためのスルーレートが狙い値となるように負荷駆動装置を製造する。

【解決手段】まず、半導体基板に第1基準電源32、スイッチング素子34、電流生成部35、およびオペアンプ33を備えた駆動回路30を形成する。この場合、第1基準電源32の第1基準電圧を調整することにより、負荷10に流す定電流の大きさを調整する。続いて、電流生成部35で生成されるテール電流が大きくなるようにテール電流のトリミングを行うことでオペアンプ33のスルーレートを調整する。これにより、オペアンプ33がスイッチング素子34を駆動したときに負荷10に流れる定電流が一定値に達するまでの定電流の立ち上がりの傾きを狙い値に調整することができる。

(もっと読む)

半導体チップおよびそれを用いた画像表示装置

【課題】画像表示装置の昇圧回路の高効率化を図ることが可能な半導体チップと、それを用いた画像表示装置を提供する。

【解決手段】この携帯電話機では、昇圧回路8のトランジスタ12の前段にバッファ14を設け、バッファ14の入力ノードの寄生容量値をトランジスタ12のゲートの寄生容量値よりも小さく設定し、トランジスタ12およびバッファ14を1つの半導体チップ21に搭載する。したがって、トランジスタ12のゲートにおけるPWM信号φPのレベル変化の鈍りを抑制することができ、昇圧回路の高効率化を図ることができる。

(もっと読む)

負荷駆動装置

【課題】複数の負荷の駆動状態に応じて、スイッチング損失の低減とノイズの抑制とを図ることができる負荷駆動装置を提供する。

【解決手段】複数の負荷2A〜2Dについて個別に設けられ、半導体スイッチング素子5,6により前記負荷をスイッチング駆動する複数の負荷駆動手段3A〜3Dで、台形波傾き制御プリドライバ7が、NチャネルMOSFET5,6のゲートに対してそれぞれ台形波状のパルス信号を出力する場合に、台形波の立上り及び立下りの傾きを変更可能に構成し、4チャネル駆動の場合は傾きを大きく、1チャネル駆動の場合は台形波の傾きを小さくする。

(もっと読む)

バッファ回路

【課題】スルーレートが高いバッファ回路を提供する。

【解決手段】単極性の複数のトランジスタと、容量素子と、を有し、該バッファ回路の利得が、前記複数のトランジスタのすべての利得により決定される構成としたバッファ回路を提供する。駆動能力が高く、且つ高周波における利得が高いバッファ回路を得ることができる。このようなバッファ回路はスルーレートも高いものとなる。該バッファ回路を構成する単極性の複数のトランジスタはPチャネル型トランジスタであってもよいし、Nチャネル型トランジスタであってもよい。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

駆動電圧制御装置

【課題】演算増幅器の能力を高めても、液晶パネルの負荷回路の時定数以上の速度で駆動できない。

【解決手段】出力切替スイッチSxが、負荷回路2に正極側の負荷駆動電圧を供給する正極側のバッファの出力を選択したとき、負極側のバッファの出力端子と負極側の負荷駆動電圧よりも低い負極側のブースト電圧の電源との間に介挿された負極側の昇圧制御スイッチTR2がオンする一方、負極側の入力信号をインピーダンス変換して負荷回路2に負極側の負荷駆動電圧を供給する負極側のバッファの出力を選択したとき、正極側のバッファの出力端子と正極側の負荷駆動電圧よりも高い正極側のブースト電圧の電源との間に介挿された正極側の昇圧制御スイッチTR1がオンするように、タイミング制御部3が制御する。

(もっと読む)

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

1 - 20 / 75

[ Back to top ]