Fターム[5J055AX27]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | 誤動作防止 (777) | ノイズ対策 (690) | スイッチングノイズ対策 (555) | 貫通電流の対策 (114)

Fターム[5J055AX27]に分類される特許

101 - 114 / 114

MOS型半導体集積回路装置

【課題】本発明は、スタンバイ時におけるリーク電流を削減し、動作遷移時における貫通電流の発生及び誤動作を防止する。

【解決手段】それぞれPチャネル及びNチャネルMOSトランジスタを有し、前段の出力信号が後段に入力信号として供給されるように多段接続された複数のMOS型回路12〜15と、複数のMOS型回路のうち、最終段からみて奇数段目のMOS型回路15、13それぞれの電源供給ノードと電源電圧VDDの供給ノードとの間に挿入されたトランジスタ16と、複数のMOS型回路のうち、最終段からみて偶数段のMOS型回路14、12それぞれの電源供給ノードと電源電圧VDDの供給ノードとの間に挿入されたトランジスタ17と、それぞれスタンバイ状態にされている複数のMOS型回路12〜15をスタンバイ状態からアクティブ状態に復帰させる際に、始めにトランジスタ17が導通し、この後、トランジスタ16が導通するように制御する制御回路20とを具備する。

(もっと読む)

コンピュータ監視装置

【課題】 単一または複数のコンピュータの動作を監視して当該コンピュータをリセットする機能を有するコンピュータ監視装置に関し、リセットラインに接続されるコンピュータの数を増加させた場合でも、出力回路部の出力レベルが低下するのを防止し、貫通電流等により出力回路部のトランジスタが破壊されるのを防止することを目的とする。

【解決手段】 第1の電源と第2の電源との間にプッシュプル形式で接続される第1のトランジスタ11と第2のトランジスタ12を含み、当該トランジスタのいずれか一方からリセット信号を供給する出力ノードを有する出力回路部1と、出力ノードのレベルを検出する出力レベル検出部2と、出力レベル検出部の検出結果に応じて、入力ノードから当該トランジスタのいずれか一方に入力される入力信号のレベルを変化させ、当該トランジスタのいずれか一方を動作状態から非動作状態に切り替える入力レベル制御部3とを備える。

(もっと読む)

駆動回路

【課題】 駆動回路の回路規模や素子数の増大を抑制する。

【解決手段】 ソースドライバ17には、タイミング回路19、レベルシフト回路L1乃至L4、レベルシフト回路L00、レベルシフト回路L04、レベルシフト回路LM−4、出力バッファ回路Bu1乃至Bu5、出力バッファ回路BuM、出力端子Out1乃至Out5、及び出力端子OutMが設けられている。

レベルシフト回路L00、レベルシフト回路L04、及びレベルシフト回路LM−4は、それぞれ出力バッファ回路Bu1乃至Bu5、BuMの隣接する4個に、例えば、レベルシフト回路L00は出力バッファ回路Bu1乃至Bu4に接続されている。レベルシフト回路L1乃至L4は、レベルシフト回路L00、レベルシフト回路L04、及びレベルシフト回路LM−4を補完する役目を有し、それぞれ隣接する4つ出力端子の内のひとつに接続されている。

(もっと読む)

レベルシフタ回路

【課題】CMOSゲートのみで貫通電流を防止するレベルシフタ回路を提供する。

【解決手段】入力端子50からの入力信号Vinと遅延部21で遅延させた入力信号Vin’を、第1の電源電圧の低電位電圧VDDLが供給されるNORゲート22とANDゲート23に入力、各々出力をゲート電圧VG1とゲート電圧VG2とする。レベルシフト部10用で、第2の電源電圧の高電位電圧VDDHが供給される第2の電源電圧端子30に接続されたPMOSトランジスタ1,2のゲートとドレインを交差接続し、各々のドレインとソースが接地端子40に接続されたNMOSトランジスタ4,5のドレインとを接続する。NMOSトランジスタ4,5のゲートにはNORゲート22出力とANDゲート23出力を接続する。NMOSトランジスタ5のドレイン電圧VD2をPMOSトランジスタ3とNMOSトランジスタ6に接続し、出力信号Voutを出力端子70から出力する。

(もっと読む)

ドライバ回路

【課題】 高速動作と低消費電力を両立させることが可能なドライバ回路を提供する。

【解決手段】 低電位側電源を基準とした論理信号Xが入力されて、高電位側電源Vccを基準とした論理信号Yを生成するドライバ回路であり、レベルシフト回路10、出力回路20、第1の検出制御回路30、および第2の検出制御回路40から構成される。ここでは、レベルシフト回路10に入力する論理信号Xおよび反転された論理信号X*によって、プルダウン回路21とトランジスタQ11,Q21とを相補的にオンオフ駆動し、第1の検出制御回路30からの制御信号out1に基づいて駆動回路11を流れるドレイン電流I1を制御するとともに、第2の検出制御回路40からの制御信号out2に基づいてプルダウン回路21を流れるドレイン電流I2を制御している。

(もっと読む)

入出力回路および半導体入出力装置

【課題】 消費電力の増大を防止することが可能な入出力回路および半導体入出力装置を提供する。

【解決手段】 トライステート出力回路(入出力回路)1は、イネーブル信号oeに基づいて出力パッドPADoを駆動するP−MOSトランジスタ65と、P−MOSトランジスタ65のゲートに接続されたノードpgの電位を制御するためのP−MOSトランジスタ64と、イネーブル信号oeの信号レベルが遷移した際に所定時間幅のパルス信号oe5および−oe5を出力するワンショットパルス発生回路10と、パルス信号oe5および−oe5が出力されている期間、P−MOSトランジスタ64を制御するためのバイアス電圧Vbiasを生成し、バイアス電圧VbiasをP−MOSトランジスタ64のゲートに印加するバイアス回路30とを有する。

(もっと読む)

波形整形回路

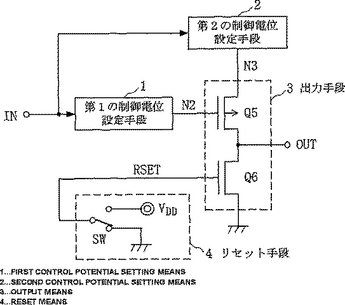

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

駆動回路

【課題】 低電圧電源から供給される電源電圧VDDが推奨動作電源電圧より低下しても、CMOS出力部等のプッシュプル出力部での貫通電流の発生を防ぐ駆動回路を提供する。

【解決手段】 ソースが高電圧電源に接続されドレインがIN4に接続されゲートがIN5に接続されたP型MOSトランジスタ2、ソースが高電圧電源に接続されドレインがIN5に接続されゲートがIN4に接続されたP型MOSトランジスタ3、ソースが接地されドレインがIN4に接続されゲートが低電圧信号を受けるN型MOSトランジスタ5、及び、ソースが接地されドレインがIN5に接続されたN型MOSトランジスタ6を有するレベルシフト部13と、P型MOSトランジスタ1及びN型MOSトランジスタ4を有するCMOS出力部14とを備え、P型MOSトランジスタ2の駆動電流は、N型MOSトランジスタ5の駆動電流より大きい。

(もっと読む)

プログラム可能なデッドタイム挿入機能を有するゲートドライバ

【課題】集積回路に組み込む新規なデッドタイム生成器であって、集積回路が、ハイサイドゲートドライバとローサイドゲートドライバとを含むものを提供すること。

【解決手段】本デッドタイム生成器は、ハイサイドゲートドライバとローサイドゲートドライバが、出力スイッチのオン時間の間にデッドタイムが生じるように出力スイッチを駆動する。また、デッドタイム設定要素が接続されている外部のデッドタイム設定端子を有する回路を集積回路の内部に備えている。更に、デッドタイム生成器は、デッドタイム設定端子におけるある範囲のデッドタイム設定値に対する段階的なデッドタイムを提供する回路を備えている。デッドタイム生成器は、デッドタイム設定端子における複数の範囲のデッドタイム設定値に対する、対応する複数の段階的なデッドタイムを生じさせる。

(もっと読む)

半導体回路

【課題】 LSIのパワーオルエリアの電源投入・遮断時に貫通電流や誤動作を発生させることなく、確実に電源遮断状態に移行させる。

【解決手段】 パワーオフエリアにマスクレジスタ19を設け、電源遮断の前にこのマスクレジスタ19に“L”のマスク信号をセットする。バックアップエリア側では、パワーオフエリアから与えられるマスク信号を保持すると共に、このマスク信号が無電圧状態となったときには“L”を保持するラッチ回路33Aを設け、このラッチ回路33Aで保持したマスク信号を用いて、パワーオフエリア側との間の入出力信号をマスクする。

(もっと読む)

出力バッファ回路

【課題】電源端子と基準電位点間に並列接続される複数の出力バッファに適用した場合、同時スイッチング時における貫通電流の大きさを減少でき、電源の電流容量が少なくて済み、また外部負荷によらず貫通電流を抑制可能とする。

【解決手段】電源端子と基準電位点間に並列接続された複数の出力バッファと、これらの出力バッファのうち第1の出力バッファを除く他の出力バッファの入力側に設けられる複数の判定回路で構成され、第n(nはn≧2の整数)の出力バッファの入力側の判定回路は、第1〜第n−1の出力バッファがスイッチング中であるか否かを判定し、前記第1〜第n−1の出力バッファのいずれかがスイッチング中であると判定した場合には、前記第nの出力バッファのスイッチングが前記第1〜第n−1の出力バッファのいずれかのスイッチングと同時に行われないように制御する判定手段とを備える。

(もっと読む)

ゲートドライブ回路、ハイサイド側ドライブモジュールおよびドライブ装置

【課題】外乱ノイズや寄生容量の影響を受けにくく、貫通電流によるスイッチングデバイスの破壊を抑制するゲートドライブ回路を得る。

【解決手段】パルス信号からデッドタイム期間が削除されたデッドタイム信号を入力し、エッジトリガ回路13は、パルス信号からデッドタイム期間を削除したデッドタイム信号を入力しデッドタイム信号の立上りエッジ信号と立下りエッジ信号とを生成し、レベルシフト回路15は、デッドタイム信号とその反転信号と立上りエッジ信号と立下りエッジ信号とを入力し、これらの4つの信号に基づいてスイッチングデバイス71の駆動信号を生成する。

(もっと読む)

インバータ回路とこれを用いた圧電発振器

【課題】CMOSインバータの貫通電流は、このインバータを用いた装置の電力消費量を増大させ、特に携帯機器においては電池の寿命を短くする。

【解決手段】従来のCMOSインバータと同じ回路のP-MOSTQ1のソースS回路に、別のP-MOSTQ3を直列に追加接続し、そのゲートと回路の入力端間を遅延回路Z1で接続し、また、前記CMOSインバータのN-MOSTQ2のソース回路に、別のN-MOSTQ4を直列に追加接続してそのゲートと回路の入力端間を遅延回路Z2で接続した回路構成にする。

(もっと読む)

スイッチング回路における不感時間制御

DC−DC変換器は、入力端子(37)と接地端子(38)との間に直列に接続された2つの電界効果トランジスタ(35,36)を有する。両方のトランジスタ(35,36)がオフとなるときの不感時間の調整は、トランジスタ(35,36)の一方又は双方のドレイン(39,44)及びソース(43,40)に直接かけられてケルビンフィードバック接続部(71,72,67,68)を設けることによって行い、信号ラインの抵抗及びインダクタンスを回避するようにしている。  (もっと読む)

(もっと読む)

101 - 114 / 114

[ Back to top ]