Fターム[5J055AX39]の内容

Fターム[5J055AX39]に分類される特許

1 - 20 / 81

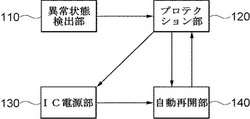

自動回復回路付き制御IC、制御ICの自動回復回路、パワ変換システム及び制御ICの自動回復方法

【課題】予備電源を備えなくても、制御ICが保護モードにて出力以外に自動復元の動作を行って、一定時間後自動に正常動作する。

【解決手段】システムまたは制御ICの異常状態を検出する異常状態検出部110と、異常状態の検出に応じて、保護モードに変更し、該保護モードにて自動回復信号を入力されて動作モードに変更するプロテクション部120と、入力電源からの電力の供給後、IC電源が予め決められた高電圧に到達すると、電力供給遮断信号に応じて入力電源からの電力の供給を遮断し、入力電源からの電力の供給及び遮断を繰り返すIC電源部130と、保護モードの開始に応じて、IC電源部130の電力供給信号及び電力供給遮断信号が交互に繰り返されるクロックをカウントし、該カウント数が予め決められた値に到達すると、プロテクション部120に自動回復信号を供給する自動再開部140とを含む。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

電源電圧検出回路

【課題】低電圧状態を検出し、システムへの通知やシステムの停止等を行う電源電圧検出回路において低電源電圧時の誤動作を回避する電源電圧検出回路を提供する。

【解決手段】基準電圧Vrefを生成する回路200の出力にプルアップ回路250を設け、基準電圧Vrefを生成する回路200を電源電圧VE(100)までプルアップする。さらに、R1(341),R2(342)から成る検出抵抗に直列にスイッチS1(347)を設け、基準電圧Vrefを生成する回路200によって、上記スイッチS1(347)をオン/オフする。そうしておいて低電源電圧時に上記プルアップ回路250により基準電圧Vref(225)を上記電源電圧VE(100)までプルアップさせると共に、上記スイッチS1(347)をオフし分圧値VI(345)を強制的に低下させることで、Vref>VIの状態を保持し、比較器330からの誤信号出力を回避する。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

過電圧保護回路

【課題】電圧伝達経路における電圧降下が小さい過電圧保護回路を提供する。

【解決手段】入力電圧と第1の電圧とを入力して、昇圧した第2の電圧を、電圧伝達経路110の遮断または導通を制御するスイッチ回路SWのMOSトランジスタPSWのゲートに供給する昇圧回路CPと、MOSトランジスタPSWのゲートに蓄積された電荷を放電する放電回路DCGとを備える。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

インジケータ駆動回路

【課題】電源電圧の変動によるインジケータの光源のちらつきを抑制するインジケータ駆動回路を提供する。

【解決手段】インジケータ駆動回路1は、2つのnpnトランジスタQ2,Q6からなるカレントミラー回路200と、カレントミラー回路200の制御側のトランジスタQ2に制御電流を供給する電流源であるpMOSトランジスタQ3,Q4と、被制御側のpMOSトランジスタQ6に流れる電流により駆動され、インジケータのLED30をオンオフさせるpMOSトランジスタQ5を備える。電流源100からカレントミラー回路200へ流す制御電流は、外部からの制御信号によりnMOSトランジスタQ1を介して切り換えられる。電流源100を構成する2つのトランジスタQ3,Q4をカスコード接続で構成することで、カレントミラー回路200に流れる電流に対する電源VCCの変動の影響を小さくする。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

負荷駆動装置

【課題】 負荷への通電を妨げることなく、昇圧した電圧が低下することを防止することができる負荷駆動装置を提供する。

【解決手段】 複数相の駆動回路のうちの少なくとも2相間において昇圧用コンデンサ47,67と第3の電源45,65との接続部に設けられ、昇圧された電圧が出力される昇圧電源端子10,13同士の電気的な接続または遮断を選択する少なくとも1つのスイッチ回路102と、少なくとも1つのスイッチ回路102を制御する少なくとも1つのスイッチ制御回路110とを備えている。

(もっと読む)

負荷制御装置

【課題】制御対象負荷の数が増えたとしてもオンオフ両タイミングをずらすことができ、電源変動勾配を抑制できるようにした負荷制御装置を提供する。

【解決手段】マイコンは、メモリのオンタイミング記憶領域に複数の負荷間で互いに重ならないようにオンタイミングのフラグを記憶させる。また、メモリのオフタイミング記憶領域に対し複数の負荷間で互いに重ならないようにオフタイミングのフラグを記憶させる(S10〜S14)。マイコンは、これらのオンタイミング、オフタイミングに応じて複数の負荷を駆動制御する(S15)。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

電源復帰検出回路

【課題】電圧比較器を用いることなく、電源遮断ブロックの電源復帰を検出する。

【解決手段】電源遮断ブロック1に配置された信号遅延回路11と、電源が常時供給される常時オンブロック9に配置された測定パターン生成回路13、測定パターン検出回路15及び遅延時間測定回路17を備えている。遅延時間測定回路17は、測定パターン生成回路13から送信された測定パターンが信号遅延回路11を介して測定パターン検出回路15に到達するまでの遅延時間を測定する。電源遮断ブロック1の電源が遮断状態から投入状態に切り替えられた後、上記遅延時間が信号遅延回路11の設計値に基づく所定の遅延量以内になったときに、電源遮断ブロック1の電源が復帰したと判断する。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】プラス端子P11とマイナス端子P12より電力が供給されて駆動する制御回路10により、FET(T1)のオン、オフを切り替えて、負荷RLの駆動、停止を制御する場合に、マイナス端子P12とグランドとを接続するアース線に、抵抗R5とダイオードD1の並列接続回路を設ける。従って、入力スイッチSW1の投入時にプラス端子11とマイナス端子12の間に配置されたコンデンサC1の放電電流I2が流れる場合であっても、抵抗R5の電圧降下VR5によりマイナス端子P12の電圧をグランドレベルよりも相対的に低くすることができ、コンデンサC1の両端電圧VC1を拡大させて、放電電流I2を抑制し、電圧V1の低下を抑えることができる。

(もっと読む)

1 - 20 / 81

[ Back to top ]