Fターム[5J055BX41]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | リセット回路 (286)

Fターム[5J055BX41]の下位に属するFターム

電源電圧低下の検出を行うもの (160)

Fターム[5J055BX41]に分類される特許

1 - 20 / 126

電圧検出回路

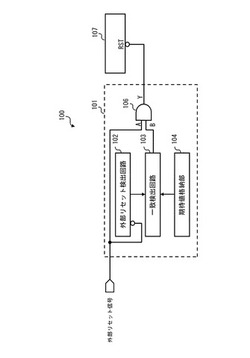

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

パワーオンリセット回路、固体撮像素子、およびカメラシステム

【課題】基準信号の精度を維持しつつスタンバイ時の電流低減を図ることが可能なパワーオンリセット回路、固体撮像素子、およびカメラシステムを提供する。

【解決手段】基準信号生成部は、少なくとも外部電源電圧検出器用基準信号を生成する第1の生成部と、記内部電源電圧検出器用基準信号を生成する第2の生成部と、を含み、第1の生成部は、電源起動時に外部電源電圧検出器用基準信号を生成可能となり、第2の生成部は、制御部からの起動信号を受けて内部電源電圧検出器用基準信号を生成可能となり、制御部は、スタンバイ期間が経過すると、起動信号を基準信号生成部の第2の生成部および内部電源電圧の生成系に出力する。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】ノイズや縮退故障等による意図しないリセット信号の解除を防止することが可能なリセット信号生成回路及びそれを備えた半導体集積回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路は、基準リセット信号RESETZを第1ノードに伝達するための信号線ROUT11と、基準リセット信号RESETZの反転信号を第2ノードに伝達するための信号線ROUTZ12と、第2ノードに伝達された信号の反転信号を出力するINV回路104と、第1ノードに伝達された信号の論理値と、INV回路104の出力信号の論理値と、が一致しない場合、基準リセット信号RESETZに関わらずリセット信号IN_RESZをアクティブにするAND回路105と、を備える。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

バンドギャップ基準電圧回路及びこれを用いたパワーオンリセット回路

【課題】バンドギャップ基準電圧回路100を確実に起動させることができる。

【解決手段】電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前には、pMOSトランジスタP6により電源VddとpMOSトランジスタP4のソース端子との間を開放させている。このため、電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前に、抵抗素子R3aによってコンデンサC1から電荷を放出させて、コンデンサC1のプラス電極の電位をpMOSトランジスタP4のゲート端子の電位の閾値よりも低くすることができる。電源電圧が上昇してpMOSトランジスタP6が電源VddとpMOSトランジスタP4のソース端子との間を接続すると、pMOSトランジスタP4がオンして、電源VddからpMOSトランジスタP6、P4を通してスタートアップ電流をnMOSトランジスタN1、N2のゲート端子に流すことができる。

(もっと読む)

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

電圧検知回路

【課題】高精度で低コストの電圧検知回路を提供する。

【解決手段】パワーオンリセット回路は、分圧回路1、バイポーラトランジスタQ1,Q2、抵抗素子R1,R2、およびベース電流補償回路10を備える。分圧回路1の出力電圧VINがバンドギャップ電圧VBGの場合、バイポーラトランジスタQ1,Q2のコレクタ電流I1,I2が一致する。電圧補償回路10は、電流I1に基いてバイポーラトランジスタQ1,Q2のベース電流の和に相当する電流I6を生成し、その電流I6をバイポーラトランジスタQ1,Q2のベースに供給する。したがって、バイポーラトランジスタQ1,Q2の各々のベース電流が大きい場合でも、高い検出精度が得られる。

(もっと読む)

半導体装置

【課題】電源投入時に、ノイズの影響により誤ってリセット信号が出力されることを防止できる半導体装置を提供すること。

【解決手段】半導体装置100は、レギュレータ11、第1のパワーオンリセット回路12、第2のパワーオンリセット回路13及び制御回路14を有する。レギュレータ11は、電源線VL11を介して電源VS11から供給される第1の電圧に基づいて、第1の電圧よりも小さい第2の電圧を生成する。第1のパワーオンリセット回路12は、電源投入後の第1の電圧が検出閾値Vt12まで上昇したことを検出し、第1のリセット信号R_12を出力する。第2のパワーオンリセット回路13は、電源投入後の第2の電圧が検出閾値Vt13まで上昇したことを検出し、第2のリセット信号R_13を出力する。制御回路14は、第1のリセット信号R_12及び第2のリセット信号R_13の論理積である第3のリセット信号R_Cを出力する。

(もっと読む)

スタートアップ回路

【課題】イネーブル等の制御信号を用いず、且つスタートアップ動作が完了した後は消費電流が極少なるスタートアップ回路を提供する。

【解決手段】2つの電流ルートの電流が0値で且つノードN11が高電位になる第1安定状態と、前記2つの電流ルートの電流が0値以外で同値になり且つノードN11が前記高電位よりも低い第1所定値になる第2安定状態をもつ対象回路のためのスタートアップ回路において、ノードN11の電位が第1所定値を超えているとき検出出力を出力するトランジスタMN21と、MN21が検出出力を出力するときバイアス電圧を生成するトランジスタMN23と、MN23でバイアス電圧が生成されるとノードN11の電位を低下させるトランジスタMN22とを備える。ノードN11の電圧が第1所定値に達すると、MN21が検出出力の出力を停止し、MN23がバイアス電圧の生成を停止し、MN22が動作を停止する。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

リセット回路

【課題】ウォッチドッグのための特殊な構成を追加することなく、マイコンラッチ時に自動的かつ確実にマイコンにリセットをかける

【解決手段】水晶振動子Xtalを用いた水晶発振回路からクロック信号を入力されるマイコン200のリセット回路100であって、マイコン200は、出力がHighとLowとで周期的に変動するGPIO端子201を備え、クロック信号の入力が停止されたときに自動的にリセット状態となる構成とされ、リセット回路100は、GPIO端子201の出力をコンデンサを用いて平滑し、平滑電圧がHighとLowの中間電位のときは水晶振動子Xtalの負性抵抗より小さい抵抗を発生して水晶振動子Xtalに印加し、平滑電圧がHighとLowのいずれかになると水晶振動子Xtalの負性抵抗以上の抵抗を発生して水晶振動子Xtalに印加する。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

リセット回路および半導体装置

【課題】 クロックゲーティング状態にあるときにも、初期化対象の論理回路の初期値を後段の論理回路に出力する。

【解決手段】 クロックに同期して動作する論理回路をリセットするリセット回路は、論理回路の出力信号を受け、論理回路がリセットされたときの出力信号の初期値と論理回路から受けた出力信号とのいずれかを出力する出力選択部と、論理回路をリセットするためのリセット信号を受け、出力選択部から初期値がリセット信号に応答して出力されるように出力選択部を制御する制御部とを有している。

(もっと読む)

パワーオンリセット回路

【課題】面積の小さいパワーオンリセット回路を提供する。

【解決手段】電源端子と接地端子との間に設けられる容量及び電流源と、容量と電流源の接続点を入力端子に接続するインバータと、を備えたパワーオンリセット回路に、電源電圧の立ち上がりを検出すると、容量をディスチャージするディスチャージ回路を設けた。ディスチャージ回路は、容量と電流源を備えているが、この容量の容量値は小さくて良いので、パワーオンリセット回路の面積が小さくなる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

リセット回路及び半導体集積回路

【課題】低電圧で動作可能なリセット回路を提供する。

【解決手段】リセット回路50Aは、Pチャネルの第1トランジスタ11を備え、第1電流i1が第1の値を超えると第1信号D1をアクティブとする第1回路10Aと、Nチャネルの第2トランジスタ21を備え、第2電流i2が第2の値を超えると第2信号D2をアクティブとする第2回路20Aと、電源電圧Vddの供給開始から、所定時間が経過した後に第3信号D3をアクティブとする第3回路30Aと、第1信号D1、第2信号D2、及び第3信号D3の全てがアクティブになるとリセット解除を指示するリセット信号RESを生成する論理回路40とを備える。

(もっと読む)

1 - 20 / 126

[ Back to top ]