Fターム[5J055CX19]の内容

電子的スイッチ (55,123) | 用途(負荷、信号の種類) (3,195) | 負荷・用途 (2,057) | スイッチング電源、DC−DCコンバータ等 (214)

Fターム[5J055CX19]に分類される特許

1 - 20 / 214

発振回路、およびDC−DCコンバータ

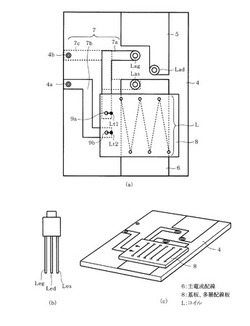

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

スイッチ素子駆動回路

【課題】グランド端子からグランド電位の供給を受けることなく、スイッチ素子をオン状態に維持することを可能とするスイッチ素子駆動回路を提供する。

【解決手段】本発明によるスイッチ素子駆動回路(100)は、電源と負荷との間に接続されたスイッチ素子を駆動するためのスイッチ素子駆動回路であって、前記電源と前記負荷との間に設けられた電圧降下素子(10)と、前記電圧降下素子の端子間に発生する電圧を動作電源として該電圧を昇圧し、該昇圧により得られた電圧から前記スイッチ素子を制御するための制御信号を生成する信号生成部(20)とを備える。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

駆動回路および電流制御回路

【課題】ペルチェ素子を加熱および冷却を切替えて使用する。

【解決手段】一端が負荷と接続され、他端が負荷を駆動する駆動用電源と接続され、少なくとも、入力端子に入力される第1の制御信号に応じてオン状態およびオフ状態を切り替える第1のスイッチング素子と、一端が負荷および第1のスイッチング素子の一端と接続され、他端が基準電位と接続され、第2の制御信号に応じてオン状態およびオフ状態を切り替える第2のスイッチング素子と、第2のスイッチング素子がオフ状態である場合に、第1のスイッチング素子の入力端子に電圧を供給する電圧供給部と、第1の制御信号および第2の制御信号のそれぞれを、第1のスイッチング素子および第2のスイッチング素子のそれぞれに供給し、第1のスイッチング素子と第2のスイッチング素子とを交互にオン・オフ動作させる制御部とを備える。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

ゲートドライブ回路

【課題】オンデューティが50%以上のパルス信号でもスイッチング素子のゲートをドライブできる安価なゲートドライブ回路。

【解決手段】直流電源Vcc1の両端にトーテムポール接続され且つ各ベースにパルス信号が入力されるトランジスタQ2,Q3と、直流電源Vcc2の両端にトーテムポール接続され且つ各エミッタがスイッチング素子Q1のゲートに接続されるトランジスタQ4,Q5と、一次巻線P1がトランジスタQ2,Q3の各エミッタとトランジスタQ2,Q3の一方のコレクタとにコンデンサC1を介して接続され、二次巻線S1がトランジスタQ4,Q5の各ベースとトランジスタQ4,Q5の各エミッタとに接続されたトランスT1とを有し、パルス信号Vinの最大オンデューティは、トランスT1の一次巻線電圧VpとトランジスタQ4,Q5のベース−エミッタ間順方向電圧とに基づいて決定される。

(もっと読む)

ドライブ回路

【課題】ベース電流による電力損失を低減するドライブ回路を提供する。

【解決手段】BJT21のベース端子にベース電流を供給するドライブ回路1は、BJT21のベース電流を生成するベース回路部30と、制御端子に供給される制御電圧に基づき、ベース電流を生成するための駆動電圧をベース回路部30に供給するドライブ部10と、BJT21のベース端子とBJT21のエミッタ端子との間に発生する第1のベース−エミッタ間電圧Vbeを検出し、検出した第1のベース−エミッタ間電圧Vbeに応じたベース電流をBJT21に供給するように制御電圧を制御して、ドライブ部10に供給するベース電流制御部50とを備える。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

電源回路

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

電圧レギュレータ

【課題】ノーマリオン型のトランジスタをオンオフ駆動できるようにする。

【解決手段】電圧レギュレータは,入力電圧に接続されたノーマリオン型の第1のトランジスタと,第1のトランジスタと出力端子との間に設けられたインダクタと,第1のトランジスタとインダクタとの接続ノードとグランド電圧との間に設けられた還流回路と,第1のトランジスタのゲートに駆動信号を供給する駆動回路と,グランド電圧に接続され,第1のトランジスタのオンオフ動作により接続ノードに生成されるパルス信号に基づいて負電圧を生成し,負電圧を駆動回路に供給する負電圧生成回路とを有する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置、及び、回路

【課題】 絶縁ゲート型スイッチング素子のゲートの電位を制御する半導体装置であって、低速スイッチング用と高速スイッチング用とで共通して使用可能な半導体装置を提供する。

【解決手段】 絶縁ゲート型スイッチング素子のゲートの電位を制御する信号を出力する半導体装置であって、第1信号出力端子を有しており、第1電位と第1電位よりも高い第2電位の間で変動する基準信号の入力を受けるか、または、内部で前記基準信号を生成することが可能であり、前記基準信号が第1電位にあるときには第3電位となり、前記基準信号が第2電位にあるときには第3電位よりも高い第4電位となる信号を第1信号出力端子に出力する第1動作と、前記基準信号が第1電位にあるときには第4電位となり、前記基準信号が第2電位にあるときには第3電位となる信号を第1信号出力端子に出力する第2動作とを切り換えて実行することができる。

(もっと読む)

1 - 20 / 214

[ Back to top ]