Fターム[5J055DX22]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | MOSFET、MISFET (1,263)

Fターム[5J055DX22]に分類される特許

101 - 120 / 1,263

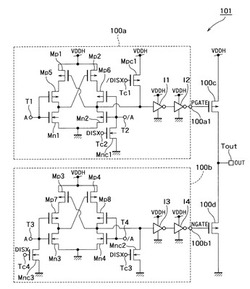

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

電源電圧検出回路

【課題】簡単な構成で電源投入時にも精度よく電源電圧の状態を検出する。

【解決手段】第1スイッチ(122)と第2スイッチ(124)とは直列に接続されてスイッチ部を形成し、第1スイッチ(122)は、基準信号に基づいて開閉が制御される。判定信号生成回路(110)は、第1電源電圧(VDD)と第2電源電圧(VSS)とに基づいて電源電圧判定信号(VG)を生成し、第2スイッチ(124)は、電源電圧判定信号(VG)に基づいて開閉が制御される。第1負荷素子(126)は、第1電源電圧(VDD)とスイッチ部との間に直列に挿入される。スイッチ部は、基準信号(Vref)が所定の第1電圧を超え、電源電圧判定信号(VG)が所定の第2電圧を超えたとき回路を閉成して第1負荷素子(126)に電流を供給し、第1負荷素子(126)とスイッチ部との接続ノードから第1電源電圧(VDD)の状態を示す第1出力信号(VOUT)を出力する。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】上限あるいは下限付近のデューティー比でも効率よく容量性負荷を駆動する。

【解決手段】駆動波形信号をパルス変調して変調信号を生成し、電力増幅した後に平滑フ

ィルターを通すことによって生成した駆動信号を容量性負荷に印加する。デジタル電力増

幅器から平滑フィルターに流れる電流の方向が一変調周期内で逆転する条件下では、その

一変調周期内での電流の最大値および最小値の絶対値が所定の閾値以上となるようにキャ

リア周波数を変更する。一変調周期内で平滑フィルターを流れる電流の最大値および最小

値の絶対値が所定の閾値を下回ると、電力増幅時に大きな損失が発生する。従って、所定

の閾値を下回らないようにキャリア周波数を変更してやれば、効率よく電力増幅を行って

容量性負荷を駆動することが可能となる。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

電圧出力回路

【課題】プッシュ・プル接続された二つのスイッチ素子のON/OFFを切り換えること

によって生じる電力損失を抑制する。

【解決手段】プッシュ・プル接続された二つのスイッチ素子に対して並列に還流ダイオー

ドを設けておく。そして、何れのスイッチ素子もOFFの期間(デッドタイム期間)では

、ONにしようとする方のスイッチ素子に設けられた還流ダイオードに順方向電圧がかか

ったら、デッドタイム期間を終了して、一方のスイッチ素子をONにする。こうすれば、

二つのスイッチ素子の寄生容量での電荷の回生および充電が完了した後に、スイッチ素子

をONに切り換えることができるので、ONにしようするスイッチ素子の寄生容量に蓄え

られた電荷が、ONにしたスイッチ素子を流れて電力損失が発生することを回避すること

が可能となる。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

アナログスイッチ回路

【課題】高位電源の電位より高い又は低位電源の電位より低い伝送信号を、MOSトランジスタを用いたアナログスイッチにより好適に阻止可能なアナログスイッチ回路を提供する。

【解決手段】第1のアナログスイッチ11と、第1のアナログスイッチ11の制御端子11cに至る制御信号経路21上に設けられた第2のアナログスイッチ12と、伝送信号の電位が所定の高電位レベルより高い場合又は伝送信号の電位が所定の低電位レベルより低い場合に第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡するよう構成された第3のアナログスイッチ13と、を備え、第2のアナログスイッチ12は、少なくとも第3のアナログスイッチ13が第1のアナログスイッチ11の一方の入出力端子11aと制御端子11cとを短絡する場合に、所定のレベルの電位が印加されてオフするようMOSトランジスタを用いて構成される。

(もっと読む)

負荷駆動回路

【課題】複数の電源電圧条件に対して電流制限特性が追従し、負荷特性に適した電流制限を行なう負荷駆動回路を提供する。

【解決手段】図1に示す負荷駆動回路は、電源及び負荷に接続された出力MOSトランジスタと、出力MOSトランジスタの出力電圧に応じて、出力MOSトランジスタに流れる出力電流を複数段階の制限電流に制限すると共に、制限電流が切り替わる際の出力電圧を電源電圧の変化に基づいて切り替える電流制限値切り替え回路と、を備える。その結果、段階的に電流制限を行い、過剰な電流制限となることを妨げ、負荷条件の拡大を図る。さらに、電流制限値の切り替えを電源電圧に対応させて行なうため、当初の電源電圧条件とはことなる電源電圧で使用したとしても、電流制限特性が電源電圧の変動に追従し、全体として負荷特性に適した電流制限を行なうことができる。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

リーク補償された電子スイッチ

【課題】電子スイッチの開放されたスイッチを通したリーク電流は、信号クロストークを引き起こす。

【解決手段】スイッチング用の電子回路は少なくとも4個の電子スイッチ200のセット100を備える。第1サブセット110の少なくとも2個の電子スイッチ210,230は直列接続され、第2サブセット120の少なくとも2個の電子スイッチ220,240は直列接続される。前記第1サブセット110の第1電子スイッチ210に接続される第1バッファ310、及び前記第2サブセット120の第2電子スイッチ220に接続される第2バッファ320を備え、前記第1バッファ310は開状態における前記第1電子スイッチ210を通した電圧降下を最小化し、前記第2バッファ320は開状態における前記第2電子スイッチ220を通した電圧降下を最小化する。また2個のサブセット110,120の間に配され、グランドに接続されたスイッチ410を備える。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

インジケータ駆動回路

【課題】電源電圧の変動によるインジケータの光源のちらつきを抑制するインジケータ駆動回路を提供する。

【解決手段】インジケータ駆動回路1は、2つのnpnトランジスタQ2,Q6からなるカレントミラー回路200と、カレントミラー回路200の制御側のトランジスタQ2に制御電流を供給する電流源であるpMOSトランジスタQ3,Q4と、被制御側のpMOSトランジスタQ6に流れる電流により駆動され、インジケータのLED30をオンオフさせるpMOSトランジスタQ5を備える。電流源100からカレントミラー回路200へ流す制御電流は、外部からの制御信号によりnMOSトランジスタQ1を介して切り換えられる。電流源100を構成する2つのトランジスタQ3,Q4をカスコード接続で構成することで、カレントミラー回路200に流れる電流に対する電源VCCの変動の影響を小さくする。

(もっと読む)

101 - 120 / 1,263

[ Back to top ]