Fターム[5J055DX22]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | MOSFET、MISFET (1,263)

Fターム[5J055DX22]に分類される特許

141 - 160 / 1,263

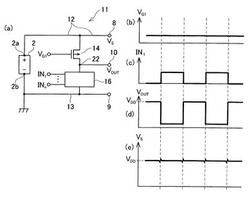

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線Npと第1の二次巻線S1と第1の二次巻線の極性とは逆極性を持つ第2の二次巻線を有する2以上の二次巻線とを有し一次巻線に駆動信号が印加されるトランスDT1、第1の二次巻線からの信号によりオンオフ制御される第1スイッチング素子Qh、第2の二次巻線からの信号によりオンオフ制御される第2スイッチング素子Ql、第1の二次巻線の一端と第1スイッチング素子の制御端子との間に接続され第1スイッチング素子を駆動する第1駆動部Q11,Q12、第2の二次巻線の一端と第2スイッチング素子の制御端子との間に接続され第2スイッチング素子を駆動する第2駆動部Q21,Q22、第1の二次巻線電圧を倍電圧整流平滑して第1駆動部に供給する倍電圧整流平滑回路D11,D12,C11,C12、第2の二次巻線電圧を倍電圧整流平滑して第2駆動部に供給する倍電圧整流平滑回路D21,D22,C21,C22を有する。

(もっと読む)

スイッチング駆動回路

【課題】オンオフ動作させる外部機器のEMIによる誤作動を確実に防ぐスイッチング駆動回路を提供する。

【解決手段】スイッチング駆動回路1は、LED4をオンオフ動作させるスイッチ素子であるpMOSトランジスタT1と、pMOSトランジスタT1のゲートソース間の抵抗10と、抵抗10に制御電流を供給するnpnトランジスタT4を含むカレントミラー回路と、抵抗10及びnpnトランジスタT4との間に設けられる遮断回路としてのnMOSトランジスタT5とを備える。制御信号がLED4を消灯制御するローレベルLのときにnMOSトランジスタT5を同時にオフすることで、EMIの影響により抵抗10から流れ込出す電流を遮断する。これにより、LED4の誤点灯を確実に防ぐ。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

適応型優先順位スキームを適用するためのクロスバー回路、およびそのようなクロスバー回路の動作方法

【課題】クロスバー回路のコンフリクトを解決する。

【解決手段】クロスバー回路はデータ入力経路12およびデータ出力経路50のアレイを有し、各交差点にはルーティング値を記憶するようにプログラム可能な構成記憶回路と、伝送回路と、アービトレーション回路とを備えるクロスバーセル20が提供される。アービトレーション回路は、適応型優先順位スキームを適用するために、同じデータ出力経路と関連する他のクロスバーセルのアービトレーション回路と組み合わせて動作して、該複数のビット線上の電圧を選択的に修正するように動作可能である。同じデータ出力経路に複数の伝送要求がある場合、同じデータ出力経路と関連する唯一のクロスバーセルの構成記憶回路は、第1の値にプログラムされるルーティング値を有し、適応型優先順位スキームに従い複数の伝送要求間のコンフリクトを解決する。さらに、各クロスバーセルは優先順位記憶回路を備える。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

周波数監視回路

【課題】より適切に安定した周波数監視を行うことが可能な周波数監視回路を提供する。

【解決手段】ウォッチドッグタイマ回路16は、キャパシタCの充放電を行う充放電部161と、充電電圧VCを基準電圧Va〜Vcと比較して比較信号Sa〜Scを生成する比較部162と、クロック信号CLKの周波数監視結果に応じたリセット信号S2を出力するリセット出力部163と、クロック信号CLKと比較信号Sa〜Scに基づいて充放電部161とリセット出力部163を制御する制御部164と、を有し、比較部162は、基準電圧Va〜Vcとして、上限電圧Vaと下限電圧Vbのほかに、中間電圧Vcを備えており、制御部162は、充電電圧VCと上限電圧Va及び下限電圧Vbとの比較結果のほか、クロック信号CLKのパルスエッジ到来時における充電電圧VCと中間電圧Vcとの比較結果に基づいて、リセット信号S2の論理レベルを決定する。

(もっと読む)

ゲート駆動回路

【課題】MOSFETで発生するホットキャリア量を抑制して高信頼性のゲート駆動回路を提供する。

【解決手段】NOEMI回路を有するゲート駆動回路10において、ゲートチャージアップ用の回路12を構成するpチャネルMOSFET(QP1)とゲートディスチャージ用の回路13を構成するnチャネルMOSFET(QN1)に同型NOEMI回路14,15を直列接続することで、QP1,QN1で発生するホットキャリア量を抑制することができる。

(もっと読む)

電力制御器システム

【課題】落雷などの故障過渡電流が流れる間はスイッチング装置を開いて過電流が流れるのを防止する一方、その間、負荷電流が中断されない電力制御器システムを提供する。

【解決手段】電力制御器システム10は、電気経路31内に設けられた、負荷20に電流を供給するスイッチング装置30を備える。スイッチング装置30の両端間の電圧または電流が所定のレベルを超えたとき、制御器50がスイッチング装置10を開くように構成する。スイッチング装置30が開いているときも、並列電気経路60を負荷に接続する回路11内の誘導素子32に蓄積された誘導エネルギーの放散により、負荷電流61が並列電気経路60および負荷20に流れ続ける。

(もっと読む)

電源回路

【課題】電源回路を備える装置の低消費電力化と、電源回路が発生させる出力電圧の安定化とを両立させる。

【解決手段】負荷へ供給するための出力電圧を入力電圧に基づいて発生させる一対のMOSトランジスタで構成された電圧発生部と、入力電圧および出力電圧の電圧値を検出する検出部と、検出された電圧値に応じて電圧発生部の駆動を制御する駆動部とを有する電源回路において、負荷の動作状態に応じて駆動部を制御することにより、一対のMOSトランジスタの不感帯の幅を変化させる制御部を有する。

(もっと読む)

負荷駆動回路

【課題】ハイサイドスイッチとして用いられるNチャネル型のMOSFETのターンオフ動作に際し、簡単な構成でオフ時間Toffと立下り時間Tfの最適化が可能な負荷駆動回路を提供する。

【解決手段】電源3と負荷1との間に接続されたハイサイドスイッチとしてパワーMOSFET2を用いた負荷駆動回路10であって、パワーMOSFET のゲート電圧Vgと電源3の電源電圧Vpとを比較する比較回路11と、パワーMOSFET2のターンオフ動作においてパワーMOSFET2のゲート端子から電荷を放電させる遮断回路12とを具備し、遮断回路12によってパワーMOSFET2のゲート端子から電荷を放電させる放電速度は、ゲート電圧Vgが電源電圧Vpより高い場合の放電速度よりも、ゲート電圧Vgが電源電圧Vpより低い場合の放電速度が遅くなるように設定されている。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

サンプルホールド回路

【課題】インバータなどの遅延が無視できない高速動作時において、クロックフィールドスルーの影響を改善するのが困難

【解決手段】MOST4はソース端子に入力されるアナログ入力信号を矩形波パルスのサンプル信号によりオンオフしてサンプリングする。MOST5はMOST4のドレイン端子にソース端子およびドレイン端子が接続されサンプル信号の極性を反転した反転サンプル信号によりオンオフしてMOST4の寄生容量を補償する。論理回路10,11はサンプル信号と反転サンプル信号の位相差を検出して誤差信号を出力する。MOST6,7はMOST5のソース端子およびドレイン端子にソース端子およびドレイン端子が接続され、位相差を補償する。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

高圧パルス発生装置

【課題】小型且つ低価格な高圧パルス発生装置を提供する。

【解決手段】高圧パルス発生装置は、パルス信号を発生するパルス発生部1と、高圧側電圧VDDを生成する高圧側電源2と、低圧側電圧VSSを生成する低圧側電源3と、前記パルス信号に応じて、入力された前記高圧側電圧VDDと前記低圧側電圧VSSとを何れか一方ずつ交互に出力端子O1から出力するスイッチング部4と、前記パルス信号の周波数と、前記高圧側電圧VDDと、前記低圧側電圧VSSとを制御する制御部5と、を備える。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

MOSFETの電流判定装置

【課題】MOSFETのオン抵抗の温度特性に追随して高精度で電流レベル判定を行う。

【解決手段】MOSFET1に一体に感温素子4が設けられ、ドレイン/ソース間電圧Vdsと温度検出信号Vfを検出する。電圧Vdsは電圧検出部6に入力され、感温素子4の電圧Vfは第1および第2の補正回路8、9に入力される。MOSFET1のオン抵抗Ronの温度特性を第1および第2の温度領域のそれぞれに対応した近似直線で近似し、傾きを変えるように補正回路8、9で演算処理する。予め設定された判定電流値をRonの温度特性を考慮して判定電圧生成部11で判定電流に相当する判定電圧Vdsrefを生成する。これにより、比較器13で判定電流以上の電流がMOSFET1に流れたか否かを精度よく判定できる。

(もっと読む)

半導体装置及びこれを備える情報処理システム

【課題】並列接続された複数の入力回路のうち使用する入力回路を切り替える際に生じる出力ノードの信号ノイズ(ハザード)を防止する。

【解決手段】それぞれが、入力信号INが供給される一つの入力ノードN10に接続し、出力信号OUTを供給する一つの内部出力ノードN11に接続し、互いに電気的特性が異なる第1及び第2の入力回路100A,100Bと、切り替え信号SELを生成し、切り替え信号SELによって、入力回路100A,100Bを制御する入力制御回路300とを備える。入力制御回路300は、入力回路100A,100Bのいずれか一方を活性から非活性へ、いずれか他方を非活性から活性へ切り替えるとき、入力回路100A,100Bが同時に活性状態となる時間を含むように制御する。これにより、入力回路100A,100Bの切り替えに伴う信号ノイズ(ハザード)の発生が防止される。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

141 - 160 / 1,263

[ Back to top ]