Fターム[5J055DX22]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | MOSFET、MISFET (1,263)

Fターム[5J055DX22]に分類される特許

81 - 100 / 1,263

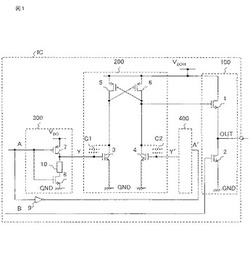

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

駆動回路、駆動信号出力回路及びインクジェットヘッド

【課題】出力する駆動信号の遅延を小さくし且つ小型化した安価な駆動回路、駆動信号出力回路及びインクジェットヘッドを実現することである。

【解決手段】駆動回路30は、負荷を駆動するプッシュ側のMOSFET32及びプル側のMOSFET33と、アノード、カソードがMOSFET32のゲート、ソースに接続されたツェナーダイオード38と、アノード、カソードがMOSFET33のソース、ゲートに接続されたツェナーダイオード39と、昇圧回路31の出力端とMOSFET32のゲートとに接続された抵抗36と、昇圧回路31の出力端とMOSFET33のゲートとに接続された抵抗37と、抵抗36、抵抗37に並列に接続されたスピードアップコンデンサ42,43と、を備える。MOSFET32,33のソースが高圧側、グランドに接続され、MOSFET32,33のドレインが互いに接続される。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチング回路装置及びそれを有する電源装置

【課題】スイッチング時の電流の急激な変化を抑制しオン状態でのオン抵抗を抑制する。

【解決手段】電源回路内の第1のノードと第2のノードとの間に設けられるスイッチング回路装置であって,前記第1または第2のノードにインダクタが接続され,第1のノードと第2のノードとの間に設けられ第1のゲート幅を有する第1のトランジスタと,第1のノードと第2のノードとの間に第1のトランジスタに並列に設けられ第1のゲート幅より大きい第2のゲート幅を有する第2のトランジスタと,電源回路の出力電圧に応じて生成される制御信号に応答して,第1のトランジスタをオン,オフに駆動する第1の駆動信号と,第2のトランジスタをオン,オフに駆動する第2の駆動信号とを,時間的にずらして出力する駆動信号生成回路とを有する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

過電流保護電源装置

【課題】直流電源11からスイッチ用のFET12を経て負荷14へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】FETのドレイン・ソース間電圧に比例した電流Iを生成する電流変換回路4と、容量素子を含む一次遅れ回路として構成された過電流検出用電圧発生回路6とを直列接続し、その接続点Sの電圧を過電流検出用電圧VS とする。過電流検出回路5から制御回路3へ過電流検出信号が入力されて来たとき、制御回路3はFET12をオフする。過電流検出用電圧発生回路6の回路定数の設定を工夫することにより、VS を速やかに大になるようにすることが出来、1種類の保護回路で大過電流時にも保護が出来る。

(もっと読む)

DC−DCコンバータ

【課題】耐高電圧スイッチ回路を通常のMOSトランジスタを用いて構成するとともに、論理回路を停止する時間を大幅に削減して低電力性能を向上させるために、初期化を高速に行うことができるDC−DCコンバータを提供する

【解決手段】チャージポンプ回路1と、その電源のオン・オフを行う第1のスイッチ用MOSトランジスタ3から構成されるDC−DCコンバータにおいて、チャージポンプ回路1の電源オフ時に、チャージポンプ回路の出力端子の寄生容量に充電された電荷を直列接続された第2および第3のスイッチ用MOSトランジスタ4,5を介して放電する構成である。

(もっと読む)

ドライバ回路

【課題】 出力オフ時のスイッチング時間を短くすることのできるドライバ回路を提供する。

【解決手段】 実施形態のドライバ回路は、を駆動する出力用MOSトランジスタMV1が、電源端子VDDと誘導性負荷RLが接続される出力端子OUTとの間に接続され、抵抗R1が、出力用MOSトランジスタMV1のゲート端子とゲート電圧印加端子VGとの間に接続され、ゲート電圧印加端子VGに一端が接続された抵抗R2と、一端が抵抗R2の他端に接続され、他端が接地端子GNDに接続され、出力用MOSトランジスタMV1を制御する制御信号VSWにより導通が制御されるNMOSトランジスタMD1とを備える。さらに、このドライバ回路は、一端が抵抗R1の他端に接続され、他端が出力端子OUTに接続され、NMOSトランジスタMD1の一端から出力される信号により導通が制御されるPNPトランジスタQ1を備える。

(もっと読む)

高周波スイッチモジュール

【課題】スイッチポート切替時間が短く、かつ低消費電力、低面積を同時に満たす高周波スイッチモジュールを提供する。

【解決手段】デコーダ3は、前記スイッチポートを切替える制御信号CNTに応答し、スイッチ7を制御するためのスイッチ制御信号SWCNTを生成して、スイッチ切替タイミング検出器は、スイッチ制御信号SWCNTに応答し、スイッチ切替え検出信号t_swを生成し、周波数制御信号生成器は、スイッチ切替え検出信号t_swに応答し、周波数制御信号ICONT、CCONTを生成し、負電圧発生回路は、周波数制御信号ICONT、CCONTに応答し、前記負電圧発生回路内で生成したクロック信号の周波数を2つ以上のそれぞれ異なる周波数に切替つつ、負電圧出力信号NVG_OUTを生成し、スイッチ7は、スイッチ制御信号SWCNTと前記負電圧出力信号NVG_OUTに応答し、複数の高周波信号ポート間の経路を切替える。

(もっと読む)

パルス生成回路、パルス生成方法、走査回路、表示装置、及び、電子機器

【課題】自身の回路動作によって所望の遷移速度のパルス信号を生成可能なパルス生成回路、その生成方法、パルス生成回路を用いる走査回路、当該走査回路を用いる表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】2つの電源の間に直列に接続され、入力パルスの論理に応じて相補的にオン/オフ動作を行う2つのスイッチ素子を有し、パルス消滅時に所望の遷移速度のパルス信号を生成するパルス生成回路において、2つの電源のうち、入力パルスと同じ極性側の一方の電源を固定の電源電圧とし、他方の電源を複数の電源電圧間で切り換え可能とする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3を介して、入力電圧Vin2がトランジスタT2のゲートに入力される。そのため、入力電圧Vin1,Vin2がともにハイとなったときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

スイッチおよびそのスイッチを用いたスイッチ回路

【課題】スイッチ用のトランジスタに発生する寄生ダイオードを介して内部に流入するESDによる負電流から内部回路を保護する。

【解決手段】第4nチャネルMOSFET(Mn4)は、ソース端子とバーグゲート端子間が接続されている。スイッチ素子は、第4nチャネルMOSFET(Mn4)のソース端子とグラウンド電位との間に接続され、第4nチャネルMOSFET(Mn4)のオフ時に第4nチャネルMOSFET(Mn4)のソース端子をグラウンド電位にする。保護回路40は、第4nチャネルMOSFET(Mn4)のソース端子と上記スイッチ素子の入力端子の接続点と、グラウンド電位との間に設けられ、静電気放電による第4nチャネルMOSFET(Mn4)のドレイン端子から流入する負電流をグラウンド電位に流す。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

過電圧保護回路

【課題】電圧伝達経路における電圧降下が小さい過電圧保護回路を提供する。

【解決手段】入力電圧と第1の電圧とを入力して、昇圧した第2の電圧を、電圧伝達経路110の遮断または導通を制御するスイッチ回路SWのMOSトランジスタPSWのゲートに供給する昇圧回路CPと、MOSトランジスタPSWのゲートに蓄積された電荷を放電する放電回路DCGとを備える。

(もっと読む)

電圧変換回路及び不揮発性半導体記憶装置

【課題】チャージポンプ回路を駆動するクロックバッファ回路に流れる瞬時電流を抑制すること。

【解決手段】

第1のトランジスタ(T11)のドレインを第1のキャパシタ(C11)によって第1の制御信号(DCLK10)に応じて昇圧駆動する第1のバッファと、第1のトランジスタ(T11)のゲートを第2のキャパシタ(C12)によって第2の制御信号(GCLK10)に応じて昇圧駆動する第2のバッファとから構成される電圧変換回路おいて、

第1のバッファは,第1の制御信号(DCLK10)の遷移時の駆動能力が,第2の制御信号(GCLK10)の遷移時の駆動能力よりも低いことを特徴とする電圧変換回路。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

スイッチング回路およびスイッチング回路を用いた撮像装置

【課題】EM−CCDのCMG駆動回路からEM−CCDの出力信号への飛び込みを低減しながら、負荷容量CMG電圧の振幅の減衰を防ぎ、矩形波特性を改善する。

【解決手段】論理バッファとPchMOSとNchMOSのゲート間にフェライトビーズとダイオードの並列接続を挿入し、MOSがターンオフする方向にダイオードが接続されているスイッチング回路において、PchMOSのドレインソース間導通抵抗が2オーム以上あり、PchMOSのドレインとNchMOSのドレインとが1オーム以上の抵抗で接続され、PchMOSのドレインと容量負荷間に、スイッチング基本波周波数におけるインピーダンスがスイッチング基本波周波数における前記容量性負荷のインピーダンスの1/2より低いインピーダンスのフェライトビーズを直列接続する。

(もっと読む)

81 - 100 / 1,263

[ Back to top ]