Fターム[5J055DX60]の内容

Fターム[5J055DX60]に分類される特許

1 - 20 / 54

駆動回路および電流制御回路

【課題】ペルチェ素子を加熱および冷却を切替えて使用する。

【解決手段】一端が負荷と接続され、他端が負荷を駆動する駆動用電源と接続され、少なくとも、入力端子に入力される第1の制御信号に応じてオン状態およびオフ状態を切り替える第1のスイッチング素子と、一端が負荷および第1のスイッチング素子の一端と接続され、他端が基準電位と接続され、第2の制御信号に応じてオン状態およびオフ状態を切り替える第2のスイッチング素子と、第2のスイッチング素子がオフ状態である場合に、第1のスイッチング素子の入力端子に電圧を供給する電圧供給部と、第1の制御信号および第2の制御信号のそれぞれを、第1のスイッチング素子および第2のスイッチング素子のそれぞれに供給し、第1のスイッチング素子と第2のスイッチング素子とを交互にオン・オフ動作させる制御部とを備える。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

電磁石制御装置

【課題】簡素な構成の信号処理部で、複雑な波形の電流信号を発生させ、ドライバーを介して該電流信号に応じた波形の電流を各電磁石の励磁コイルに通電できる電磁石制御装置を提供すること。

【解決手段】複数の電磁石10を備え、各電磁石10の励磁コイルXに所定波形の励磁電流を通電することにより、隔壁で仕切られた空間内に発生したプラズマ分布を能動的に制御する電磁石制御装置であって、所定波形の励磁電流信号を生成する信号処理部13と、該信号処理部13からの所定波形の励磁電流信号S2を増幅して各電磁石10の励磁コイルに通電するドライバー11と、当該電磁石装置の各部に電力を供給する電源部17とを備えた電磁石制御装置。

(もっと読む)

負荷駆動回路

【課題】誘導性負荷の逆起電力による負荷駆動装置における誤動作を防止する。

【解決手段】出力トランジスタQN1にオン電流が流れている場合、第2トランジスタMN4aは、出力トランジスタQN1のソースに供給された電源電圧を第1トランジスタMN2のバックゲートに供給する。一方、出力トランジスタQN1においてオン電流の逆方向の負電流が流れている場合、第2トランジスタMN4aは、出力トランジスタQN1のドレインに供給された電源電圧を第1トランジスタMN2のバックゲートに供給する。

(もっと読む)

ゲート駆動回路

【課題】MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することのない、ゲート駆動回路を提供する。

【解決手段】パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

(もっと読む)

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

モータ制御装置

【課題】従来技術によれば、過電流が発生した場合、比較器が過電流閾値との比較を行い、MOSFETをオフさせる構成となっている。この構成ではMOSFETをオフした場合にMOSFETのドレイン・ソース間電圧がVB−GNDの値となり、その後に比較器がモニターした場合、ドレイン・ソース間電圧が過電流閾値を越えてしまうため、比較器は再び過電流と検知してしまうため、正常状態に復帰することができない。

【解決手段】過電流時に、MOSFESTのドレイン・ソース間電圧が過電流閾値よりも大きくなった場合、MOSFETをオフする。その後、CPUがモータ端子の天絡、地絡を検出するために、モータ端子電圧のA/D値を用いて故障の診断を行う。その際、過電流検知の方法としてはコンパレータを用いるシートベルトリトラクタ用モータ制御装置を提供する。

(もっと読む)

スイッチ回路

【課題】高い周波数においても大電力を扱う用途に適用できるスイッチ回路を提供する。

【解決手段】スイッチング素子である電界効果トランジスタに並列に接続されており、夫々炭化珪素(SiC)及び窒化ガリウム(GaN)からなる2つのショットキバリアダイオード(SBD)について、順方向に導通し始めるオン電圧の高低に応じて、順方向の電圧に対する電流の変化率が大小となるようにする。これにより、オン電圧が低い方のGaNからなるSBDから環流電流を先に導通させ、順方向の電圧の上昇と共に、オン電圧が高い方のSiCからなるSBDへより多くの環流電流を分流させるように導通させて、環流電流による導通損失を各SBDに分散させる。

(もっと読む)

スイッチ回路に給電する供給回路

エネルギ効率を改善するよう、スイッチ回路(2)に給電する供給回路(1)は、電源(7)から第1の量の入力電力を受けて、スイッチ回路(2)の制御部(3)を有する出力回路(5)へ第1の量の出力電力を供給する第1の供給モードと、第2の量の入力電力を受けて、第2の量の出力電力を供給する第2の供給モードとを有する。第1の量の出力電力は、第2の量の出力電力よりも大きい。第2の量の入力電力は、零よりも大きく、且つ、スイッチ回路(2)を動作させるのに必要なスイッチ電力の量よりも小さい。スイッチ回路(2)は、負荷(8)を切り換えるリレーを有してよい。第1の量の入力電力は、リレーの主接触部を介して到達してよい。スイッチ(47)は、出力信号レベルを切り替えてよい。リレーは、双安定リレーであってよい。  (もっと読む)

(もっと読む)

出力回路およびモータ駆動装置

【課題】パワートランジスタの誤動作を防止する。

【解決手段】パワートランジスタM1は、出力端子POUTと電源端子PVCCの間に設けられる。プリドライバ10は、電源端子PVDDと第2端子P2の間に直列に接続され、制御信号S1に応じて相補的にオン、オフが制御されるハイサイドトランジスタM2およびローサイドトランジスタM3を含み、2つのトランジスタの接続点の電位を、パワートランジスタM1の制御端子に出力する。定電圧回路20は、第2端子P2を所定の電圧VL(=Vref)に安定化させる。定電圧回路20の出力トランジスタM4は、第2端子P2と接地端子PGNDの間に設けられる。差動アンプ24は、第2端子P2の電位VLが所定の目標値Vrefに近づくように、出力トランジスタM4の制御端子の電圧Vg4を調節する。フィードバックキャパシタC1は、第2端子P2と出力トランジスタM4の制御端子の間に設けられる。

(もっと読む)

スイッチング回路及び電力変換回路

【課題】スイッチング回路や電力変換回路について、単アーム構造の場合でも導通制御端子電源の自給化を可能とする。

【解決手段】スイッチ素子17と制御端子電源用コンデンサ21を備え、制御端子電源用コンデンサの放電によりスイッチ素子のゲート端子に電圧を印加するようにされているスイッチング回路について、制御端子電源用コンデンサの負側端子は、主電源5の基準電圧端子18に接続するとともに、ハーフブリッジ回路22を介してゲート端子に選択的に接続できるようにし、制御端子電源用コンデンサの正側端子は、ハーフブリッジ回路24を介して主電源の正側端子15とスイッチ素子のソース端子に対して選択的に接続できるようにする。そして制御端子電源用コンデンサは、正側端子が主電源に接続することで充電がなされる一方で、負側端子がゲート端子に接続し、正側端子がソース端子に接続することで放電する。

(もっと読む)

PWM信号生成回路、D級増幅器及びその駆動方法

【課題】クラスD増幅器へのPWM信号の印可のオン/オフ時にポップノイズを発生させないこと。

【解決手段】パワー・オン状態になる又はアン・ミュート状態にされたことを示す第1状態を、またはパワー・オフにされ又はミュート状態にされる第2状態を検出する。第1状態検出時、それぞれ漸増する幅を有する複数のパルスとその後のデューティ50%のパルス列を含む差動PWM信号を生成してマルチプレクサ経由で増幅器に送り、オーディオ・プロセッサの出力が安定状態になるとこれを増幅器にマルチプレクサ経由で送る。第2状態検出時、オーディオ・プロセッサの出力が安定状態の場合に、それぞれ漸減する幅を有する複数のパルスとその後の無信号のパルス列を含む差動PWM信号を生成し、同時に、この生成したパルスをマルチプレクサを介して増幅器に送る。ここで、漸増/漸減するパルスのパルス数と各幅は本発明に開示した方程式を満足する関係にある。

(もっと読む)

レベルシフト回路

【課題】外的要因により発生するコンデンサの充放電による信号伝達不良を防止して、確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態を第1コンデンサC1を介してセットするセットレベル回路20aと、第2電圧レベルの論理状態を第2コンデンサC2を介してリセットするリセットレベル回路20bと、セットレベル回路のセット信号とリセットレベル回路のリセット信号とによりローサイドスイッチQ1に直列に接続されたハイサイドスイッチQ2をオン/オフ駆動する駆動回路24と、第1コンデンサ及び第2コンデンサに流れる電流の内の少なくともいずれか一方を検出する電流検出回路15,16,を備える。

(もっと読む)

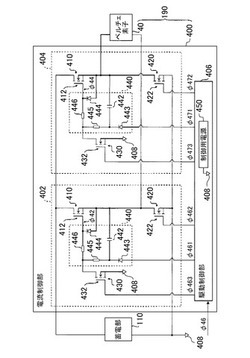

Hブリッジ回路

【課題】MOSFETの切り替え時に発生する回生電流が周辺回路に与える影響を低減することができるHブリッジ回路を提供する。

【解決手段】寄生NPNトランジスタTr2は、寄生NPNトランジスタTr1よりも、LDMOS20(MOSFETQ2)への距離が近いため、電流増幅率hFEも大きい。このように意図的に発生させた寄生NPNトランジスタTr2からドレインへの電流供給が増加することで、ISO端子6やVDD端子7を介して周辺回路から引き抜かれる電流量が減少する。

(もっと読む)

モータ駆動回路及びモータ駆動回路の検査方法

【課題】複数のFETのゲートリーク電流をまとめて測定することができる。

【解決手段】電流計38の他端を、モータ駆動回路10の端子28及び30と接続した状態で、検査用探針40の他端を検査用パッド42に接触させると、検査用パッド42を介して、P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bのゲート端子に電圧が印加される。P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bのゲート端子に電圧が印加されると、ゲートリーク電流が、P−MOSFET24A及び24B、並びにN−MOSFET26A及び26Bの各々のゲート・ソース間を流れ、端子28及び30を介して電流計へ流れ、電流計によってゲートリーク電流が検出され、ゲートリーク電流の大きさが正常時のゲートリーク電流値より大きいか否かを判断することにより、モータ駆動回路を検査することができる。

(もっと読む)

半導体装置

【課題】貫通電流の防止機能を含む半導体装置を半導体基板上に1チップ化する場合に、従来の半導体製造工程を活用することができるようにした半導体装置の提供。

【解決手段】この発明は、ローサイドスイッチを構成するトランジスタQN2のゲート・ソース端子間にダイオード接続されるトランジスタQN5と、ローサイドスイッチを構成するトランジスタQN4のゲート・ソース端子間にダイオード接続されるトランジスタQN6と、を備えている。そして、トランジスタQN5のしきい値電圧がトランジスタQN2のしきい値電圧よりも相対的に低くなっている。また、トランジスタQN6のしきい値電圧がトランジスタQN4のしきい値電圧よりも相対的に低くなっている。

(もっと読む)

半導体装置

【課題】プリドライバ回路のトランジスタサイズを小さくしてICのチップエリア占有面積を小さくすること可能である上に、出力回路のスイッチング素子の駆動の高速化を図ることが可能な半導体装置の提供。

【解決手段】この発明は、少なくともMOSトランジスタQN1、QN2を直列接続してなる出力回路2と、MOSトランジスタQN1を駆動するプリドライバ回路3Aと、を備えている。プリドライバ回路3Aは、MOSトランジスタQN1を駆動する低耐圧トランジスタであるMOSトランジスタQN36を含み、このMOSトランジスタQN36は半導体基板と分離層を介して形成するようにした。

(もっと読む)

過電流保護回路及びD級アンプ

【課題】本発明は、D級アンプの破壊を防止する。

【解決手段】本発明は、PWM信号S22A及び当該PWM信号S22Aの波形が反転したPWM信号S22Bと、パルス信号S31とをそれぞれ合成することによりPWM出力信号S24A及びS24Bを生成し、電流検出部132によってD級アンプIC105へ流れる電流を電圧として検出し、また出力段112から出力されるPWM出力信号S25Aの電圧、及び出力段113から出力されるPWM出力信号S25Bの電圧を検出することにより、過電流が信号処理部111又はアンプ制御部114へ流れているか否かを検出し、過電流を検出するとバッテリ2から信号処理部111及びアンプ制御部114と出力段112及び出力段113とへ流れる電流を遮断することにより、D級アンプIC105の破壊を未然に防止することができる。

(もっと読む)

過電流保護回路及びD級アンプ

【課題】本発明は、D級アンプの破壊を防止する。

【解決手段】本発明は、電流検出部32によってD級アンプIC5へ流れる電流を電圧として検出し、また出力段12から出力されるPWM出力信号S5Aの電圧、及び出力段13から出力されるPWM出力信号S5Bの電圧を検出することにより、過電流が信号処理部11又はアンプ制御部14へ流れているか否かを検出し、過電流を検出するとバッテリ2から信号処理部11及びアンプ制御部14と出力段12及び出力段13とへ流れる電流を遮断することにより、D級アンプIC5の破壊を未然に防止することができる。

(もっと読む)

1 - 20 / 54

[ Back to top ]