Fターム[5J055EY01]の内容

Fターム[5J055EY01]の下位に属するFターム

Fターム[5J055EY01]に分類される特許

1,461 - 1,471 / 1,471

フェイルセイフな方法で誘導負荷を遮断するための装置および方法

【課題】誘導負荷54の遮断時の誘導電圧の大きさを監視することにより、誘導負荷54をフェイルセイフな方法で遮断する。

【解決手段】入力側の遮断信号20,22または24を受信すれば少なくとも1つのスイッチング素子26により負荷54を遮断する。遮断時に負荷54において誘導電圧Uiが発生するが、この誘導電圧Uiは閾値スイッチ38,40,41,44により制限されている。閾値スイッチ38,40,42,44は、監視回路68,70により監視されており、閾値スイッチ38,40,42,44の1つが故障すれば監視回路68,70において誤差信号が発生する。

(もっと読む)

信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅器及びプロセッサ

【解決手段】信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅及び処理回路が与えられる。入力データ信号は複数の信号利得に従って処理される。生成された信号は複数の信号値を有し、所定の下側及び上側閾値と比較される。所望の出力信号は、最大値が所定の下側閾値を横切らない場合には最大サンプル信号値であり、複数のサンプル信号値の内の隣接する大きいものが所定の上側閾値を横切る場合には最小サンプル信号値であり、一対のサンプル信号値の大きい方が所定の上側閾値を横切りかつ小さい方の値が所定の下側閾値を横切らない場合には複数のサンプル信号値の内の相互に隣接する一対の小さい方であり、大きい方の値が所定の下側閾値を横切りかつ所定の上側閾値を横切らない場合には一対のサンプル信号値の小さい方と大きい方との組み合わせである。 (もっと読む)

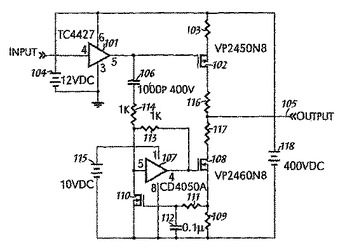

静電結合を用いた高電圧パルスドライバ

高電圧システムに共通する、高電源リプルにおいて有用である静電結合を用いた高電圧ドライバである。それは、デューティサイクルの最大範囲を許容するが、変圧器の磁気の制限はなく、または、光学式の結合方法における複雑さの増加もない。それはまた、出力駆動ラインにアークする高電圧によって作成される過渡電圧においても、強固である。本発明はまた、特に例示的ディスプレイの応用における使用のために、低コストでの静電結合の使用を再構築するが、静電結合に特有の制限はない。  (もっと読む)

(もっと読む)

半導体スイッチ回路

入力端子と出力端子との間に第1、第2、第3半導体スイッチを直列接続して挿入し、入力端子に接続された第1半導体スイッチ及び出力端子に接続された第3半導体スイッチのそれぞれに第1、第2電圧印加手段を並列接続し、それぞれの電圧印加手段を、利得が約+1の状態に設定され、入力側が入力端子及び出力端子に接続された直流増幅器と、電圧印加手段用半導体スイッチとの直列接続回路で構成し、この電圧印加手段用半導体スイッチの一端を第1と第2半導体スイッチの接続点Jまたは第2と第3半導体スイッチの接続点Kに接続し、スイッチ制御手段が第1〜第3半導体スイッチと電圧印加手段用半導体スイッチを逆モードでをオン及びオフ状態に制御し、第1〜第3半導体スイッチがオフ状態に制御されたときに、第1及び第2電圧印加手段が入力端子及び出力端子の電位を接続点J及びKに印加するように構成した半導体スイッチ回路。 (もっと読む)

半導体集積回路装置及びそれを用いた電源電圧監視システム

本発明に係る半導体集積回路装置であるリセットIC(1)は、入力電圧(Vin)を基準電圧と比較して入力電圧(Vin)の立ち上がり、立ち下がりを検出する検出回路(4)と、検出回路(4)からの立ち上がり検出信号を、接続端子(CT)を介して接続されたコンデンサ(C)を充電することにより遅延させるとともに第1電圧の出力信号(Vout)が与えられることによりコンデンサ(C)を放電する遅延回路(8)と、遅延回路(8)により遅延された立ち上がり検出信号を保持する保持回路(9)と、保持回路(9)で保持された立ち上がり検出信号により第1電圧となる出力信号(Vout)を生成するとともに検出回路(4)からの立ち下がり検出信号により第2電圧となる出力信号(Vout)を生成するドライバ(10)を備える。 (もっと読む)

電力変換回路及び電力制御回路の動作及び回路

通常、並列なMOSFETは、電源用途において単一のゲート信号で駆動されるため、MOSFET間のカレントシェアリングが個々のMOSFETの特性に関して自動的に規定される。これは、MOSFET間の電流分布の大規模な非均一性をもたらす可能性がある。本発明によれば、MOSFETのオン抵抗の個々の制御が与えられ、このことが、並列化されたMOSFET間での改善されたカレントシェアリングを可能にする。  (もっと読む)

(もっと読む)

電流検出式の双方向スイッチおよびプラズマディスプレイ用の駆動回路

【解決手段】開示される双方向スイッチ(20)は、第1および第2の半導体スイッチング素子(22)と、これらのスイッチング素子に直列に接続されることによって直列回路を形成する電流センサ(RS)と、これら第1および第2のスイッチング素子がほぼ同時にオン・オフされるようにこれら第1および第2のスイッチング素子のオン・オフ操作を制御する駆動回路(30)であって、制御入力に応じてこれら第1および第2のスイッチング素子をオンにしたり電流センサの電流がほぼゼロ電流近くまで低下する際にこれら第1および第2のスイッチング素子をオフにしたりする駆動回路と、を備える。また、このような双方向スイッチ(20)を用いたプラズマディスプレイパネル(PDP)用の放電サステイン駆動回路も開示される。 (もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

整流器

【課題】 簡易な構成で、低損失で交流を整流することができる整流器を提供することである。

【解決手段】 p型半導体からなるベースBとサブエミッタSは、互いに接しないようにして、n型半導体からなるコレクタCに接合されている。n型半導体からなるエミッタEは、ベースBに接合されている。ベースB−エミッタE間には抵抗器Rが接続され、サブエミッタSにはバイアス用電源VBの正極が接続され、エミッタEには負極が接続される。コレクタCとエミッタEが実質的に同電位となったとき、ベースB−サブエミッタS間が導通して抵抗器Rに電圧降下が生じるが、コレクタC−エミッタE間は導通しない。コレクタCを基準としたエミッタEの電圧が更に低下すると、コレクタC−エミッタE間が導通する。

(もっと読む)

電流−電圧変換回路

【課題】 操作が容易でしかも簡単な構成により、過大電流入力による内部増幅器の飽和動作を極小にし、かつ過大電流入力後の正常出力への復帰時間を短縮することが可能な電流−電圧変換回路を提供する。

【解決手段】 電流入力端子2と、第1の増幅器4と、電圧出力端子3とを備え、入力した電流Iinを電圧Vccに変換し、この変換した電圧Vccを出力する電流−電圧変換回路において、電流入力端子2に、第1の増幅器4の飽和動作時に入力した電流Iinを接地GND10側へ分流する分流回路5を設けたことを特徴とする。

(もっと読む)

複合形小電流スイッチ回路

【課題】 端末側の通信線に障害が生じ絶縁不良となった場合でも局側交換機においてその障害の検出が可能なこと。

【解決手段】 端末側の通信線に異常が生じると、片線側の入力端子L1A、抵抗2を通った電流はPUT6のゲートに流れ、抵抗2には電圧降下V2dが生じる。これによりPUT6のゲート電圧はV2dだけ低くなる。高抵抗8により、PUT6のアノード、ゲート間の電位差もほぼV2dとなり、PUT6のアノード、カソード間はONし、入力端子L1A、抵抗7、PUT6、ダイオード4、抵抗5、出力端子L1B、通信線の障害点のルートが構成される。他線側も同様にPUT35のアノード、カソード間はONとなる。流入する電流が小電流であってもPUT6、PUT35はONを継続し、PUT6、PUT35を通して通信線の障害点までの回路が構成され、局側交換機により障害を検出することができる。

(もっと読む)

1,461 - 1,471 / 1,471

[ Back to top ]