Fターム[5J055EZ17]の内容

Fターム[5J055EZ17]に分類される特許

1 - 20 / 31

誘導性負荷の駆動回路

パワー半導体素子の駆動回路

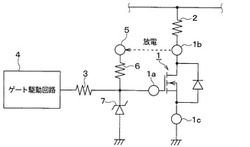

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

半導体スイッチ

【課題】半導体スイッチにおいて、エネルギー効率を高くする。

【解決手段】半導体スイッチ1は、LED2を駆動回路3により駆動して発光させ、LED2から発光された光を受光部4により受光する。駆動回路3は、バイポーラトランジスタ31と、コイル32と、ダイオード33等を有する。バイポーラトランジスタ31は、導通状態と非導通状態とに切換えられ、導通状態のときに、電源からLED2に電流が供給される状態にし、非導通状態のときに、電源からLED2に電流が供給されない状態にする。コイル32は、LED2に直列に接続されており、バイポーラトランジスタ31が導通状態から非導通状態になったときに、自己誘導作用によって誘導起電力を発生する。ダイオード33は、LED2及びコイル32に並列に接続されており、バイポーラトランジスタ31が非導通状態のときに、コイル32が発生する誘導起電力によって、LED2に電流を還流させる。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

微小電気機械システム(MEMS)アレイを含む電力切替システム

【課題】微小電気機械システム(MEMS)アレイを含む電力切替システムを提供すること。

【解決手段】切替システム(4)は、ダイオードブリッジを形成する複数のダイオードと、複数のダイオードに接近して結合された微小電気機械システム(MEMS)スイッチアレイ(12)とを含む。MEMSスイッチアレイ(12)は(M×N)アレイをなして電気的に接続される。(M×N)アレイは、第2のMEMSスイッチ脚部(44)に並列に電気的に接続された第1のMEMSスイッチ脚部(40)を含む。第1のMEMSスイッチ脚部(40)は直列に電気的に接続された第1の複数のMEMSダイを含み、第2のMEMSスイッチ脚部(44)は直列に電気的に接続された第2の複数のMEMSダイを含む。

(もっと読む)

電源供給装置、情報処理装置

【課題】

サージ電圧を効果的に低減するとともに、簡易な回路構成で消費電力を低減した電源供給装置及び情報処理装置を提供する。

【解決手段】

電源供給装置は、交流電力が入力される入力端子と、前記入力端子に入力される交流電力を整流する整流回路と、前記整流回路で整流された電力を平滑化する平滑用キャパシタと、前記平滑用キャパシタの両端子間に直列に接続される、トランス用一次巻線及びスイッチング素子と、前記トランス用一次巻線に結合されるトランス用二次巻線と、前記トランス用二次巻線に接続される出力端子と、前記スイッチング素子に並列に接続されるスナバ回路であって、第1キャパシタ及び第2キャパシタの並列回路と、前記並列回路に直列に接続される抵抗器とを有するスナバ回路とを含む。

(もっと読む)

半導体素子の駆動装置

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1の半導体素子駆動回路13は、ゲート抵抗21と、電圧源22と、di/dt帰還部23と、バッファ111と、を備えている。バッファ111は、従来良く使われる方式であるトランジスタ111ta,111tbで構成されるIGBT駆動用のバッファ回路の少なくとも一部である。di/dt帰還部23は、トランス121と、抵抗122と、を備えている。即ち、トランス121が、di/dt検出部及びゲイン部に対応する。なお、電圧源22とバッファ111とを結ぶ経路に抵抗122が直列接続され、抵抗122の両端が、トランス121の2次側に接続されており、当該経路上の抵抗122の両端の間が、電圧源に対応する。

(もっと読む)

半導体装置、スナバデバイス

【課題】放熱設計や配線設計によるコストを抑制するスナバデバイスを備えた半導体装置の提供を目的とする。

【解決手段】本発明の半導体装置は、スイッチングトランジスタ1と、スイッチングトランジスタ1と同一導電性基板(フレーム)上に実装されるリカバリーダイオード2及びスナバデバイス6とを備える。スナバデバイス6は、スイッチングトランジスタ1の出力端子C−基準端子E間に接続されたSiC−MOSFET3と、SiC−MOSFET3のゲート端子G−ドレイン端子D間に形成されたツェナーダイオード4と、SiC−MOSFET3のゲート端子G−ソース端子S間に形成された抵抗器5とを備える。スイッチングトランジスタ1の基準端子E、SiC−MOSFET3のソース端子、リカバリーダイオード2のアノード端子が共通接続される。

(もっと読む)

ゲート駆動回路の電源装置

【課題】初期充電回路が不要な自己給電形のゲート駆動回路の電源装置を提供することである。

【解決手段】電力用半導体スイッチ素子(3)に並列接続された、スナバダイオード(35)とスナバコンデンサ(37)とからなる直列回路と、端子電圧をゲート駆動回路(11)に電源電圧として印加する電源用コンデンサ(51)と、スナバコンデンサ(37)の正電位側端子と電源用コンデンサの正電位側端子間に介在されて、電源用コンデンサ(51)に充電電流を流すノーマリオンタイプのスイッチ素子(43)と、 ノーマリオンタイプのスイッチ素子(43)を制御するスイッチ制御回路と、を備える。スイッチ制御回路は、電源用コンデンサ(51)の端子電圧が所定値以上になったときにノーマリオンタイプのスイッチ素子(43)をオフさせるように構成される。

(もっと読む)

パワースイッチング素子直列電圧制限回路

【課題】 パワースイッチング素子直列電圧制限回路を提供する。

【解決手段】 パワースイッチング素子直列電圧制限回路は、複数のパワースイッチング素子(Q1〜Qn)などからなるパワースイッチング素子直列分岐回路を含み、当該パワースイッチング素子は制御端と、高端(SD)と低端(WD)とを含み、パワースイッチング素子は分岐回路に直列にされるが、当該複数のパワースイッチング素子(Q1〜Qn)直列方式は1つのパワースイッチング素子における高端(SD)と別の1つのパワースイッチング素子における低端(WD)とを順に従って直列する。また、複数のエネルギー一時記憶回路(K1〜Kn)を含み、各パワースイッチング素子の両端が1つのエネルギー一時記憶回路を対応並列するが、各パワースイッチング素子の開/閉が非同期短時間過電流の負荷エネルギーを記憶するためである。また、前記パワースイッチング素子直列分岐回路に電圧制限を行う集中電圧制限回路Hを含む。

(もっと読む)

BTL回路

【課題】素子数が少なくでき、且つグランドバウンスの影響が抑えられるようにしたBTL回路を提供する。

【解決手段】トランジスタMP1,MP2と、該各トランジスタMP1,MP2に直列接続されたトランジスタMN1,MN2とからなり、トランジスタMP1とMN1の共通接続点を出力端子OUTPとし、トランジスタMP2とMN2の共通接続点を出力端子OUTNとするBTL回路である。入力端子VINの入力信号とトランジスタMP1のゲート電位を反転遅延させた信号とトランジスタMN2のゲート電位の信号とを入力して、出力を、トランジスタMN1のゲートにそのままの位相で帰還させ、トランジスタMP2のゲートに反転して帰還させるノア回路NOR1を有する。また、入力端子VINの入力信号とトランジスタMN1のゲート電位を反転遅延させた信号とトランジスタMP2のゲート電位の信号とを入力して、出力を、トランジスタMP1のゲートにそのままの位相で帰還させ、トランジスタMN2に反転して帰還させるナンド回路NAND1を有する。

(もっと読む)

Hブリッジ回路

【課題】MOSFETの切り替え時に発生する回生電流が周辺回路に与える影響を低減することができるHブリッジ回路を提供する。

【解決手段】寄生NPNトランジスタTr2は、寄生NPNトランジスタTr1よりも、LDMOS20(MOSFETQ2)への距離が近いため、電流増幅率hFEも大きい。このように意図的に発生させた寄生NPNトランジスタTr2からドレインへの電流供給が増加することで、ISO端子6やVDD端子7を介して周辺回路から引き抜かれる電流量が減少する。

(もっと読む)

負荷回路の保護装置

【課題】負荷回路でデッドショートが発生した場合に、即時にこの負荷回路のみを遮断して負荷回路を保護する負荷回路の保護装置を提供する。

【解決手段】複数の負荷回路と電源VBを接続する共通配線に生じる逆起電力E1を検出するE1検出回路13と、各負荷回路を接続する負荷接続配線の一部に生じる逆起電力E2を検出するE2検出回路12を備える。そして、E1検出回路13にて共通配線に生じる逆起電力E1が所定の閾値を超えたことが検出され、且つ、E2検出回路12にて負荷接続配線にE1と同一の向きとなる逆起電力E2が発生した場合に、この負荷回路を遮断する。従って、短絡事故が発生した場合には即時にこの負荷回路を遮断することができる。また、その他の負荷回路を継続して作動させることができる。

(もっと読む)

パルストランスを用いた信号伝達回路

【課題】パルストランスを用いた信号伝達回路に接続される回路要素の誤動作を回避する。

【解決手段】パルストランスTの2次側において、スイッチ素子Q2は、IGBTのゲート・エミッタ間に設けられる。コンデンサCは、スイッチ素子Q2の制御端子に接続される。スイッチ素子Q3は、コンデンサCに接続される。パルストランスTの1次側に設けられているスイッチ素子Q1をターンオフすると、2次側において負電圧が発生し、コンデンサCがチャージされる。スイッチ素子Q1がオフ状態である期間は、パルストランスTの励磁エネルギーが放出された後であっても、コンデンサCの負電圧は保持され、スイッチ素子Q2はオン状態に保持されるので、IGBTのゲート・エミッタ間のインピーダンスは低い状態に維持される。

(もっと読む)

誘導性負荷の駆動装置

【課題】逆起電圧を吸収させるに際して所望の還元電流特性を得つつ、過度な発熱が生じるのを防止できるような誘導性負荷の駆動装置を提供する。

【解決手段】第1のスイッチング素子28と、第2のスイッチング素子30と、外部供給電源12に接続される電路44を有すると共に、第1のスイッチング素子がオフ、第2のスイッチング素子がオンされるとき、誘導性負荷の逆起電圧によって生じる逆起電流をアースに還流させる還流回路18と、第1、第2のスイッチング素子28,30がオフされるとき、逆起電圧を外部供給電源12に吸収させると共に、逆起電圧を吸収する逆起電圧吸収回路20と、逆起電圧吸収回路20に介挿されると共に、逆起電圧吸収回路20に吸収される逆起電圧の電圧量を切り換える切換手段52を備えるように構成する。

(もっと読む)

半導体素子の駆動回路

【課題】本発明は、高速ターンオフが可能なスイッチング素子の高速な電流遮断に伴い発生するスイッチングノイズを確実に低減するとともに、スイッチング素子の駆動回路系を安定に動作させることができる半導体素子の駆動回路を提供することを目的とする。

【解決手段】半導体素子QのゲートにダイオードDrのカソードを接続し、前記半導体素子のソースに前記ダイオードのアノードを接続するとともに、

前記ゲートと前記カソードとの間又は前記ソースと前記アノードとの間に抵抗Rrが挿入接続されたフィードバック回路10を有することを特徴とする。

(もっと読む)

スイッチ制御装置、開閉器及びスイッチ制御方法

【課題】スイッチを閉じた場合に、電源から負荷装置に突入電流が流れ込んで、スイッチに大きな負荷がかかることを防ぐことができるスイッチ制御装置、開閉器及びスイッチ制御方法を提供する。

【解決手段】電源と負荷装置との間に接続されるスイッチ21を制御するスイッチ制御装置22であって、スイッチ21の閉命令を取得する開閉命令取得部221と、開閉命令取得部21が閉命令を取得した場合にスイッチ21を閉時間だけ閉じる第1の処理と、スイッチ21を開時間だけ開く第2の処理とを交互に行なう制御部225とを備え、閉命令を取得後の通電開始時にスイッチ21の開閉を繰り返すことによってスイッチ21に流れる突入電流を抑制する。

(もっと読む)

ソリッドステートリレー

【課題】コストの上昇を抑制すると共に、異常動作を防止し、且つスナバ回路の抵抗近傍部品が故障してしまうことを防止することが可能なソリッドステートリレーを提供する。

【解決手段】ソリッドステートリレー20は、スナバ回路Sを構成するコンデンサC0と抵抗R0との接続点dと、トライアックTAのゲート端子Gとを接続する第3接続ライン28cを備えている。さらに、ソリッドステートリレー20は、第3接続ライン28c上に設けられた抵抗R2と、接続点eと接続点bとの間に設けられたコンデンサCとを備えている。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子だけではなく、半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】ゲート端子に電圧を供給することでオン・オフを制御する半導体スイッチの駆動回路において、駆動回路3の出力ゲート電圧を検出するゲート電圧検出手段5と、半導体スイッチ4の主端子電圧を検出する主電圧検出手段9と、ゲート電圧状態を光絶縁して低圧回路に伝達する第一の信号絶縁手段6と、半導体スイッチの主電圧状態を光絶縁して低圧回路に伝達する第二の信号絶縁手段10と、第一の信号絶縁手段の信号と半導体スイッチの駆動指令、第二の信号絶縁手段の信号と半導体スイッチの駆動指令とを各々比較し、正常又は異常を判別する判別手段7、11とを備える。

(もっと読む)

1 - 20 / 31

[ Back to top ]