Fターム[5J055EZ27]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 論理素子(INVは除く) (1,593) | 単安定回路 (28)

Fターム[5J055EZ27]に分類される特許

1 - 20 / 28

半導体装置

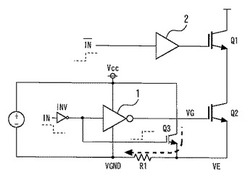

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

スイッチ回路、半導体装置及び携帯無線機

【課題】負バイアス発生回路を用いずにマージン電圧を改善することができる手段をスイッチ回路に提供する。

【解決手段】N型MOSFETを用いて構成されるスイッチM1を、信号をアンテナに同通するスイッチに、P型MOSFETを用いて構成されるスイッチM2を、信号を接地するシャント用にそれぞれ用いる。各スイッチを構成するMOSFETのゲート端子に共通の制御信号を入力する。この制御信号の反転信号をスイッチM2の接地端に接続することで、各MOSFETのゲート端子の電位を接地電圧に設定できる。

(もっと読む)

ゲート駆動回路

【課題】本発明は、レベルシフト高圧トランジスタのゲートに接続される電源の電圧が高い場合にも低い場合にも弊害なく稼動するゲート駆動回路を提供することを目的とする。

【解決手段】ゲート電圧の波形がパルス信号で制御されるレベルシフト高圧トランジスタと、該レベルシフト高圧トランジスタのゲートと電源を接続する抵抗と、該レベルシフト高圧トランジスタのドレインと接続され、該レベルシフト高圧トランジスタのドレイン電流に応じてゲート駆動信号を出力する高電圧回路と、該レベルシフト高圧トランジスタのソース及びゲートと接続され、該ドレイン電流が増大すると該抵抗を流れる電流を増大させるように構成されたカレントミラー回路と、該電源の電源電圧が低い場合は該抵抗の抵抗値を低減させ、該電源の電源電圧が高い場合は該抵抗の抵抗値を維持する抵抗調整手段とを有する。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

半導体回路

【課題】低消費電流でノイズ耐性に優れた高圧側パワートランジスタを駆動する回路を提供する。

【解決手段】低圧側入力信号(HIN)に従って短い期間活性状態となるワンショットパルス(ON_B)を生成するワンショット回路(11)を設ける。第1および第2の電流供給部(14,16)により、入力信号およびワンショットパルスの発生するワンショットパルス信号に従って内部ノード(15)に電流を供給する。第1の内部ノードを流れる電流をウイルソンカレントミラー回路(20)で受け、電流検出部(R3)により電圧信号に変換し、ゲートドライバ(DRV)により、スイッチングパワートランジスタの駆動信号を生成する。

(もっと読む)

半導体集積回路および電源装置

【課題】電源線や接地線に重畳されるスイッチングノイズを低減することのできる半導体集積回路および電源装置の提供を図る。

【解決手段】第1電源線VINと第2電源線GNDとの間に直列に設けられた複数組の第1スイッチ素子Tp1〜Tp3および第2スイッチ素子Tn1〜Tn3を有し、基準電圧Vrに基づいて前記第1および第2スイッチ素子をオン/オフ制御する半導体集積回路であって、前記各第1スイッチ素子を、それぞれ遅延時間を設けて順に制御する制御回路14を有するように構成する。

(もっと読む)

高周波回路のスイッチング方法及び高周波回路

【課題】休止時のゲート−ドレイン間の電圧が小さくなるようにし、また運転/休止の切替え時に低ドレイン電圧領域を通過させないようにする。

【解決手段】高周波回路に含まれる能動素子に対し駆動電圧を与えることにより、この能動素子の運転と休止を切り替える高周波回路及びそのスイッチング方法で、休止状態の能動素子のドレインに、定常運転レベルの電圧Vdを印加し、その後、能動素子のゲートに、定常運転レベルの電圧Vgを印加することにより運転に切り替え、一方、運転状態の能動素子のゲートに、定常運転レベルの電圧Vgに換えてピンチオフ電圧Vpを印加し、その後、能動素子のドレインに印加されている定常運転レベルの電圧Vdを切断することにより、休止に切り替える。

(もっと読む)

電流変動制御装置、半導体集積回路、電流変動制御方法および電流変動制御プログラム

【課題】面積を小さくでき、かつ、消費電流の変化を抑制して安定した動作を行う半導体集積回路の全体消費電流を制御する電流変動制御装置を提供する。

【解決手段】電流変動制御装置は、本来的用途に応じて設けられている複数の既存内部回路Bを選択的に活性化させて調整用の消費電流を生じさせる電流制御回路と、内部回路Aのリセット解除およびリセット投入を制御するリセット制御信号を出力するとともに電流制御回路に動作許可を与える動作許可信号を出力するリセット制御回路と、を備える。電流制御回路は、既存内部回路Bに活性化制御信号を出力し、内部回路Aのリセット解除前に既存内部回路Bを順次選択して活性化させることによりこれら既存内部回路Bによる調整用消費電流を徐々に上昇させ、内部回路Aのリセット解除時に既存内部回路Bの活性化を停止させる。

(もっと読む)

半導体スイッチモジュール

【課題】当該半導体スイッチモジュールが適用された機器の誤動作や自己の故障を防止できる半導体スイッチモジュールを提供する。

【解決手段】外部からの駆動信号に含まれる所定幅以下のパルスを除去するフィルタ回路12〜16、と、フィルタ回路で所定幅以下のパルスが除去された駆動信号をゲート信号としてオン/オフする半導体スイッチ19とを備える。

(もっと読む)

電力用素子の故障検出装置

【課題】パワーモジュールに用いられる電力用素子の故障を簡単な構成で検出可能な故障検出装置を提供する。

【解決手段】故障検出装置1Bは、電力用素子としてのIGBTQ1の主電極間の電圧を、ダイオードD7を介して検出する。そして、故障検出装置1Bは、ダイオードD7のアノード電圧が予め定める基準電圧V3より低電圧であるとき、IGBTQ1は短絡故障であると判定する。好ましくは、ダイオードD7のアノード電圧が予め定める基準電圧V4より高電圧であることを併せて判定すれば、フライホイールダイオードD1がオン状態である正常動作の場合を除外できる。

(もっと読む)

電流増幅半導体素子の駆動回路

【課題】 電流増幅半導体のベース電流をコレクタ電流に応じた必要最小限の値に制御するようにし、高速で低消費電力の電流増幅半導体素子の駆動回路を提供する。

【解決手段】 2個の直流電源の正側電源2の正極と負極の間に、チョッピング用スイッチング素子4とインダクタ6と被制御電流増幅半導体1のベース及びエミッタとの直列回路を接続するとともに、チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソード及び負側電源3の負極にアノードとなるようダイオード8を接続し、被制御電流増幅半導体のベースと負側電源の負極間に制御用スイッチング素子7を接続した回路構成をなし、被制御電流増幅半導体のコレクタ及びエミッタ間の電圧を検出し、被制御電流増幅半導体がオン状態時に、該電圧が準飽和電圧近辺の2値間になるようにチョッピング用スイッチング素子のオンオフ期間を制御する制御回路5を有する電流増幅半導体の駆動回路。

(もっと読む)

電力供給遮断回路及び液滴吐出装置

【課題】ICの過度の温度上昇やICの発火を確実に防止する。

【解決手段】ドライバIC50が正常に動作し、シフトレジスタ106からワンショットタイマ82に所定時間間隔で出力されるストローブ信号が、ワンショットタイマ82からリレー81にON信号が出力し終える前に、次のストローブ信号を出力し終えているときには、ワンショットタイマ82からリレー81にON信号が出力され続け、駆動用VDD2配線55を介して駆動パルス用電源と駆動回路62とが接続された状態が保持され続ける。ドライバIC50に異常が生じ、シフトレジスタ106からワンショットタイマ82に、ストローブ信号が出力されなくなると、ワンショットタイマ82からリレー81にON信号が出力されなくなり、駆動用VDD2配線55による駆動パルス用電源と駆動回路62との接続が遮断される。

(もっと読む)

半導体装置

【課題】 高耐圧電力用集積回路が、スイッチングデバイスの導通状態から非導通状態への遷移、または非導通状態から導通状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合においても、スイッチングデバイスの誤動作を防止できる半導体装置を提供する。

【解決手段】 高電位側パワーデバイス駆動回路HDは、スイッチングデバイス12の導通状態が変化するような信号を伝達した際、スイッチングに伴い発生する誤信号をフィルタ回路8にて的確に除去できるよう、前記信号の伝達直後から一定期間、2つのレベルシフト用高耐圧NMOSのオン/オフ状態を必ず同一状態にするためのマスク信号発生回路18を有する。

(もっと読む)

スイッチ回路およびこのスイッチ回路を用いたステップアッテネータ

【課題】GaAs−FETスイッチの低速尾部効果を低減するのに十分な輝度でLEDを発光させても、長期間に渡って安定した高速切替が可能なスイッチ回路およびこのスイッチ回路を用いたステップアッテネータを実現することにある。

【解決手段】低速尾部効果を有するGaAs−FETスイッチを用いたスイッチ回路に改良を加えたものである。本回路は、FETスイッチを照射するLEDと、GaAs−FETスイッチがオフ状態からオン状態に遷移するのに伴って、LEDを所定の時間発光させる駆動回路とを有することを特徴とするものである。

(もっと読む)

半導体集積回路装置

【課題】負荷を短時間で安定状態にすることが可能な半導体集積回路装置を提供する。

【解決手段】例えば、スタートアップ回路ST−UPと、電流バイアス回路IBIASと、温度補正回路T−CPSと、スイッチ回路SW1,SW2と、プリチャージ回路PC1,PC2と、PMOSトランジスタMP1,MP2を備えた定電流回路ISを設ける。ST−UPは、イネーブル信号ENを受けて1ショットパルス信号を生成する。IBIASは、MP1のゲートを駆動し、例えば正の温度特性を備えた電流I1を生成する。T−CPSは、MP2のゲートを駆動し、例えば負の温度特性を備えた電流I2を生成する。SW1,SW2は、ENが非活性の際にIBIASおよびT−CPSの電源を遮断する。PC1,PC2は、ST−UPからの1ショットパルス信号を受けて、MP1,MP2を一定期間オーバードライブする。

(もっと読む)

出力回路

【課題】出力信号のリンギングを抑制することのできる出力回路を提供する。

【解決手段】ドライブトランジスタ(1)は、内部信号に応答して第1の電源ノード(300)上の電圧を出力ノード(6)へ伝達する。比較回路(490)は、内部信号出力タイミングを規定するクロック信号(φck)に応答して活性化されて、第1の電源ノード(300)上の電圧と基準電圧(Vref)とを比較する。トランジスタ素子(492)が、比較手段の出力信号に応答して第2の電源ノード(Vcc)と第1の電源ノードとの間に電流の流れを生じさせる。このとき、第1の電源ノードの電位上昇時間は、クロック信号の遷移時間よりも長い。

(もっと読む)

半導体装置

【課題】本発明は、簡単な回路構成で電圧駆動型素子のターンオン時のスイッチング動作に伴って発生するノイズを低減し、且つ効率の高いスイッチング動作を駆動制御することが可能な半導体装置を提供することを目的とする。

【解決手段】半導体装置は、電圧駆動型素子のゲート端子にターンオンのための駆動信号を出力する駆動回路が、少なくとも2つのスイッチング素子の並列回路を有して構成され、制御回路が、ターンオン時のゲート電圧がミラー電圧に到達したとき並列回路のスイッチング素子を切り換えて、電圧駆動型素子の駆動能力を低くするよう構成されている。

(もっと読む)

半導体装置の入出力回路

【課題】 pull−down抵抗が端子に設けられている場合においても、

AC特性を改善することを目的とする。

【解決手段】 半導体内部電源電圧よりも高電圧の外部信号線に接続される出力端子部6と、フローティングNウェルを有し複数のPチャネル型トランジスタ52、53、54とアナログスイッチ51aにより構成され半導体内部信号を外部へ出力するハイ側出力回路部と、複数のNチャネル型トランジスタ55、57が直列に接続され半導体内部信号を外部へ出力するロー側出力回路部とを備えた半導体装置の入出力回路において、前記アナログスイッチを構成するPチャネル型トランジスタ51aの閾値電圧を他のトランジスタの閾値電圧より低く設定した。

(もっと読む)

1 - 20 / 28

[ Back to top ]