Fターム[5J055EZ39]の内容

Fターム[5J055EZ39]に分類される特許

121 - 140 / 177

通信システム及び通信装置並びにPWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができる通信システムを提供する。

【解決手段】マスタ11は、通信中において通信周波数を微小変動させると共に、バス3のドライブレベルを許容範囲内で変化させる。また、マスタ11は、バス3をドライブする場合の電流駆動能力を変化させてレベル遷移に要する時間も変化させるので、信号レベルが変化する場合の波形の傾きもダイナミックに変化させて信号の周波数帯域をより拡げるようにして、発生するノイズのピークレベルを一層抑制する。

(もっと読む)

負荷駆動装置

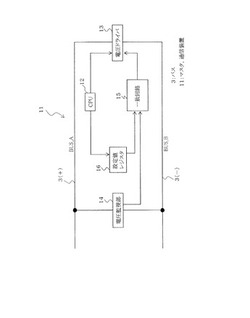

【課題】負荷装置へ通電する前に負荷装置の異常を検出可能な負荷駆動装置を提供する。

【解決手段】作動SW4が作動側の時、リレー12がオンして、ソレノイド(負荷装置)3への通電を可能とする。CPU14は、作動SW4が作動側で、その他の作動条件が成立した場合、ソレノイド駆動回路5へソレノイド3の駆動指示をする。この駆動指示よりソレノイド駆動回路5は、ソレノイド3へ通電する。リレー12の接点間には、プルダウン抵抗13が接続されている。電圧モニタ回路6は、抵抗R3,R4を介してソレノイド3の+端子15に接続されるとともに、ソレノイド3の+端子15の電圧をモニタし、CPU14の端子bへ入力する。CPU14は、ソレノイド3への通電前(非通電時)に、電圧モニタ回路6の抵抗とプルダウン抵抗13との分圧比に基づいて、ソレノイド3の異常または正常を判断する。

(もっと読む)

A/D変換用電圧入力回路およびA/D変換用電圧入力方法

【課題】車載用負荷の駆動状態に応じて、A/D変換回路に出力する負荷側の被測定電圧の電圧レベルを変更可能とするA/D変換用電圧入力回路を提供する。

【解決手段】負荷41に対する駆動回路20のON/OFF駆動に応じてA/D変換回路13に出力する例えば接続点Cの被測定電圧の電圧レベルを変更可能とするために、接続点Cの被測定電圧を分圧する分圧用抵抗R1,R2と切替制御用トランジスタTr2,Tr3とを備え、駆動回路20をOFFにした場合、切替制御用トランジスタTr3をONにして、被測定電圧を分圧用抵抗R1,R2により略分圧した電圧をA/D変換回路13に出力し、一方、駆動回路20をONにした場合、切替制御用トランジスタTr3をOFFにして、被測定電圧をそのままA/D変換回路13に出力し、もって、駆動回路20の駆動状態如何により、電圧レベルを変更し、A/D変換回路13におけるA/D分解能を切り替える。

(もっと読む)

出力回路

【課題】入力信号に応じた信号を出力端子から出力する出力回路に関し、複数の信号が衝突した場合であっても出力信号を安定化できる出力回路を提供することを目的とする。

【解決手段】本発明は、入力信号に応じた信号を出力端子から出力する出力回路において、入力信号を増幅する第1の増幅回路(112)と、入力信号を増幅する第2の増幅回路(113)と、第1の増幅回路(112)の出力信号に応じてスイッチングされ、オン時に出力端子(Tout0)に電流を供給する第1のトランジスタ(114)と、第2の増幅回路(113)の出力信号に応じてスイッチングされ、オン時に出力端子(Tout0)から電流を引き込む第2のトランジスタ(115)と、入力信号に応じて第1の増幅回路(112)の動作を制御する第1の制御回路(116)と、入力信号に応じて第2の増幅回路(113)の動作を制御する第2の制御回路(117)とを有することを特徴とする。

(もっと読む)

半導体集積回路

【課題】簡単な構成で、消費電流をさらに少なくすることができる半導体集積回路を提供する。

【解決手段】時計回路21、および種々の制御回路ブロック24、25、26、27、28を第1チップ20に配置する一方、第2チップ30には、時計回路21にのみ電源を供給する時計用電源回路31、一次制御回路ブロック(クロックジェネレータ24、CPU25、ROM26)に電源を供給するための第1メイン電源回路32、二次制御回路ブロック27、28に電源を供給するための第2メイン電源回路33を配置する。時計用電源回路31は常時オンとして時計回路21を常時動作させるが、時計回路21によって計測される時間に基づいて他の制御回路ブロックの使用未使用を決定して、一次制御回路ブロックの未使用時には第1メイン電源回路32をオフにし、二次制御回路ブロックの未使用時には第2メイン電源回路33をオフにする。

(もっと読む)

集積回路装置、マイクロコンピュータ及び電子機器

【課題】直接非同期リセットをいれても誤動作なく処理可能な集積回路の提供。

【解決手段】本集積回路装置10は、非同期リセット入力90が非同期入力に接続されるフィリップフロップ20を含んで構成されるCPU10と、非同期リセット入力90及びクロック入力80に基づき、非同期リセット入力解除後の最初のクロックでディセーブル状態からイネーブル状態に変化するライトディセーブル信号52を生成するライトディセーブル信号生成回路50を含み、CPU10は、ライトディセーブル信号52がディセーブル状態の間は前記フィリップフロップ20へ新たなデータが書き込まれるのを防止する書き込み防止回路60を含む。また非同期リセット入力解除に所定クロックだけ遅延させてディセーブル状態からイネーブル状態に変化するライトディセーブル信号を生成するようにしてもよい。

(もっと読む)

リセット信号生成回路

【課題】動作状態に応じてリセット信号を同期又は非同期に切替えて生成することができるリセット信号生成回路を提供すること。

【解決手段】動作検出回路21は、CPUの動作を検出し、動作検出信号OCを出力する。信号制御回路22は、動作検出信号OCに基づいて、システムリセット信号RSTXに応答し、リセット信号C_RSTを内部クロック信号CLKと同期又は非同期にて出力する。

(もっと読む)

ON側を危険側とするフェールセーフ性を有するスイッチ回路

【課題】半導体スイッチ素子と電流・電圧検知素子とを使用してON側を危険側とするフェールセーフ性を有するスイッチ回路を構成する。

【解決手段】半導体スイッチ素子と電流・電圧検知素子とを配置して、複数の半導体スイッチ素子の一つがON故障しても出力側に電流が流れないよう構成し、出力側に電流を流さないままで各スイッチ素子のON故障を検知することを可能とした。

(もっと読む)

信号選択回路及びプログラム

【課題】ある出力信号を切り替える際に、切り替えられていない出力信号にノイズを発生させない。

【解決手段】複数のアナログ信号の中から選択される同一の又は異なる第1及び第2アナログ信号をデジタル信号に変換することにより第1及び第2デジタル信号を出力する信号選択回路であって、複数のアナログ信号の中から第1及び第2アナログ信号を選択するアナログ信号選択回路と、アナログ信号選択回路から出力される第1アナログ信号を第3デジタル信号に変換して出力する第1ADコンバータと、アナログ信号選択回路から出力される第2アナログ信号を第4デジタル信号に変換して出力する第2ADコンバータと、第3及び第4デジタル信号の一方又は双方を第1及び第2デジタル信号として選択的に出力するデジタル信号選択回路と、アナログ選択信号及び前記デジタル選択信号を出力する制御回路と、を備える。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

スイッチ式ホットスワップコントローラ

本発明は、通信システムにおける電子基板をホットスワッピングするための電気回路(100)、方法及びコンピュータプログラムを説明する。電気回路における電流の増加は、スイッチング回路(150)においてパワートランジスタをスイッチングするマイクロコントローラ(130)により、電子基板に対するコンデンサ電圧を徐々に増加するように制御される。電流レベルはマイクロコントローラ(130)自体又は外部電流感知回路(140)のいずれかにおいて測定され、最大電流レベルと比較される。  (もっと読む)

(もっと読む)

オーディオ信号増幅装置

【課題】 複数の入力端子にそれぞれ接続された装置のうち、聴取を希望する装置を変更する場合でも、その都度入力端子の切換え作業をする必要がなく、また、予約録画機能を備える装置の予約録画の開始によって入力端子が勝手に切換わってしまうことを防止することができるオーディオ信号増幅装置を提供する。

【解決手段】 他の装置から出力されたオーディオ信号を入力する複数の入力端子と、複数の入力端子のうち増幅部にオーディオ信号を入力する入力端子を切換えにより選択する切換部と、送信された再生開始の指示信号を受信する受信部と、再生開始の指示信号を複数の入力端子にそれぞれ対応させて記憶する記憶部と、記憶部に記憶した再生開始の指示信号と一致する信号を受信したとき増幅部にオーディオ信号を入力する入力端子を再生開始の指示信号に対応する入力端子に切換えるよう切換部を制御する制御部とを備える。

(もっと読む)

半導体装置

【課題】レベルシフト回路に供給される電源が低い場合に、負荷に流れる出力電流を抑え、負荷の誤動作を防止できる半導体装置を提供することができる。

【解決手段】

本発明にかかる半導体装置1は、ゲートに入力されるゲート信号S1に応じて、L負荷2に流れる電流を制御する出力MOSトランジスタM0と、Vcc端子の電源電圧に基づいて、入力信号のレベルをシフトしゲート信号を生成するレベルシフト回路12と、電源電圧に基づいて、L負荷2と出力MOSトランジスタM0との間の出力電圧を検出し、ゲート信号のレベルを調整する制御信号調整回路と、を備えるものである。

(もっと読む)

制御回路

【課題】外来ノイズによってリセット回路が誤動作することを防止することができる制御回路を提供すること。

【解決手段】装置の制御を行う制御回路において、リセット信号を発生させるリセット信号発生手段と、リセット信号発生手段で発生したリセット信号により回路のリセット動作を行うリセット手段と、リセット信号の感度を鈍くする感度鈍化手段を備えたことを特徴とする。又、前記感度鈍化手段は、制御回路で指定した所定の期間のみ有効とする。

(もっと読む)

サンプリング制御装置、方法、プログラムおよび記録媒体

【課題】ダイオードを有するサンプリングヘッドにおけるRF帯域とIF帯域とを共に広くすることができないという現象に対処する。

【解決手段】第一ダイオードD1のアノードに負のバイアス電圧を与え、第二ダイオードD2のカソードに負のバイアス電圧と同じ大きさの正のバイアス電圧を与えるバイアス電圧付与部16と、負のバイアス電圧の大きさを制御するバイアス電圧制御部15と、第一ダイオードD1のカソードに接続され、入力信号を受ける入力信号端子61と、第三ダイオードD3のカソードに接続されるキャパシタンス要素Cと、第三ダイオードD3のカソードとキャパシタンス要素Cとの間に接続され、出力信号を出力する出力信号端子66と、第一ダイオードD1のアノードに正のパルス信号を与える正パルス信号源63pと、第二ダイオードD2のカソードに正のパルス信号と同期した負のパルス信号を与える負パルス信号源63nとを有する。

(もっと読む)

電源ショート保護回路

【課題】端子の電源ショート時にも電圧駆動素子およびシャント抵抗を保護する。

【解決手段】一端が端子T1に接続され、他端がシャント抵抗Rsを介して接地された電圧駆動素子10と、シャント抵抗Rsの電圧を検出する検出回路20と、検出回路20からの電圧検出信号で電圧駆動素子10をON/OFF制御する駆動回路30とを備える電源ショート保護回路において、電圧駆動素子10と並列にシャント抵抗Rsに比べて大きな抵抗値の抵抗素子R1を接続することにより、電圧駆動素子10のOFF時にもシャント抵抗Rsに電流を流して電圧を検出回路20で検出し、端子T1が電源ショートしているときには電圧駆動素子10をONさせないように駆動回路30を制御する。

(もっと読む)

負荷駆動装置

【課題】 負荷駆動装置の電気回路に生じた地絡異常と断線異常とを確実に区別して検出する手段を備えた負荷駆動装置を提供すること。

【解決手段】 バッテリー電源と、前記バッテリー電源に接続する電源回路と、前記電源回路から分岐する複数の分岐電源回路と、前記複数の分岐電源回路上にそれぞれ設けられ、バッテリー電源から電力を供給される複数の負荷と、を備える負荷駆動装置において、前記複数の負荷のうち少なくとも1つの負荷の下流側の前記分岐電源回路上に設けられ、当該負荷の電流を検出する第1の電流検出手段と、前記複数の負荷の上流側の前記電源回路上に設けられ、前記複数の負荷の総電流を検出する第2の電流検出手段と、前記第1の電流検出手段と前記第2の電流検出手段とにより検出された電流値に基づいて前記複数の負荷の異常を検出する異常検出手段と、を設けた。

(もっと読む)

ディジタル信号出力装置

【課題】 ディジタルオーディオ信号出力端子が外部接続端子を介し外部機器に接続さ

れているか否かを判別してディジタルオーディオ信号出力端子からのディジタルオーディ

オ信号の出力および出力停止を自動的に切り換えられるディジタル信号出力装置を提供す

る。

【解決手段】 ディジタルオーディオ信号出力端子Dを外部機器10に接続線9を介し

接続する外部接続端子2における外部機器10の接続状態時にのみ電気的絶縁状態となる

部位に接続されて、外部機器10の接続および非接続に対応してスイッチング動作される

スイッチング素子Q1と、スイッチング素子Q1を通じての信号の入力および非入力の別

によりディジタルオーディオ信号出力端子Dからの出力をディジテルオーディオ信号また

は比較的低い一定値の直流電圧信号を択一的に出力すように切換制御する制御部1aとを

備えている。

(もっと読む)

パワーICの保護装置

【課題】 短絡によって生じる過電流に対してモータ駆動用のパワーICを確実に保護する。

【解決手段】 短絡検出回路91はホッパーモータ57の正端子と負端子との短絡を検出する。また、短絡保護回路93は、短絡検出回路91が短絡を検出すると、パワーIC81の保護用入力端子STをローレベルにしてパワーIC81からホッパーモータ57への電力供給を停止することによりパワーIC81を保護する。短絡保護遅延回路95は、短絡が続くと所定時間後に短絡保護回路93による保護をラッチする。また、ラッチ解除回路97は、ラッチされているパワーIC81の保護を解除する。

(もっと読む)

リセット回路及びそのリセット回路の動作方法

【課題】電源電圧がCPUの動作電圧を下回っている場合に、外部からのスタンバイモード解除信号を受け付けないようにするマイクロコンピュータを提供する。

【解決手段】電源電圧の状態を示す信号を出力する電圧検出部2と、複数の動作モードで動作するデータ出力回路3とを具備するリセット回路1を構成する。複数の動作モードは、電源電圧が第1閾値電圧以上の電圧であることを示す通常モードと、電源電圧が第1閾値電圧から第2閾値電圧の範囲であることを示すデータ保持モードと、電源電圧が前記第2閾値電圧以下であることを示すデータ消去モードとを含む。データ出力回路2は、データ保持モードからデータ消去モードへの遷移に応答して、保持している前記データをリセットし、データ消去モードへ移行せずに前記データ保持モードから前記通常モードへ遷移するときに、保持されていた前記データを出力する。

(もっと読む)

121 - 140 / 177

[ Back to top ]