Fターム[5J055EZ39]の内容

Fターム[5J055EZ39]に分類される特許

161 - 177 / 177

情報処理装置,及び、半導体集積回路

【課題】同一のクロック信号を複数の半導体集積回路に分配する場合において、基板のアートワークの自由度を高めつつパワーオンリセット機能を安価に実現できる情報処理装置と、このような情報処理装置に組み込まれる半導体集積回路とを、提供する。

【解決手段】情報処理装置10に組み込まれるASIC14の内部のリセット回路モジュール14bは、定電圧電源ユニット11からの電気の電圧を監視するとともに、電圧がリセット電圧を超過した後、CPU13及び他IC15内のPLL回路モジュールのロックアップ時間以上の一定時間だけ待機してからCPU13及び他IC15並びに内部回路モジュール14aへメインリセット信号を出力する。

(もっと読む)

半導体装置

【課題】

供給される基準電圧に応答して、入力されるアナログ信号をAD変換してデジタルデータを出力する半導体装置において、その基準電圧が変動するときでも、その電圧変動の影響を受けることのないデジタルデータを生成する半導体装置を提供する。

【解決手段】

基準電圧を生成する基準電圧生成回路と、その基準電圧に応答して、センサから出力される出力電圧をAD変換するAD変換回路とを具備する半導体装置を構成する。そして、その基準電圧生成回路は、基準電圧に対応するセンサ用電圧を生成して、そのセンサ用電圧をセンサ用電圧出力端子を介してセンサに供給する。

(もっと読む)

電子装置及び表示装置及びクロック信号供給制御方法

【課題】

クロック信号によるノイズの影響を、安価且つ簡単な回路構成で低減させた電子装置及びクロック信号供給制御方法の提供。

【解決手段】

スケーラIC121からTVマイコン131へのOSDクロック信号線供給ラインであるOSDクロック信号線17と基準電位(グランド)との間にバイパス回路122を設け、装置起動時の発振不安定期間若しくはTVマイコン131がOSDクロック信号を必要としない期間において、バイパス回路122をオンとすることにより、OSDクロック信号をグランドに接地し、OSDクロック信号線17から発せられるノイズを低減させる。

(もっと読む)

コンパレータ切替え回路

【課題】 動作モードに応じて2つのコンパレータの動作状態を切替える場合でも、外部に対して不定レベルの信号が出力されることを確実に防止できるコンパレータ切替え回路を提供する。

【解決手段】 動作切替え回路11は、外部より送信される通信データを受信して二値レベル判定を行なうコンパレータ1,2の動作切替えを行なう場合、マイコン4が出力するモード切替え信号を遅延回路12を介して遅延させた信号を生成し、その遅延信号とモード切替え信号とをORゲート13及びANDゲート14で論理合成してハイレベル期間が異なるCOMP1,COMP2制御信号を生成すると、それらの制御信号により何れか1つのコンパレータ1,2が動作状態となっている期間を経て切替えを行う。また、マルチプレクサ3の選択切替えは遅延回路12の出力信号によって行う。

(もっと読む)

負荷駆動回路

【課題】 負荷電流が流れたままの状態を回避するとともに、ツェナーダイオードによるトランジスタの保護機能を正常に機能させる。

【解決手段】 負荷の駆動を停止する場合、NPN型トランジスタ21をオンさせたままNPN型トランジスタ11をオフさせ、NPN型トランジスタ11からNPN型トランジスタ21へサージ電流を流し終える所定期間以上が経過した後、NPN型トランジスタ21をオフさせる。

(もっと読む)

定電流供給装置

【課題】 定電流駆動用のトランジスタが短絡状態の故障になっても、過電流を防止できる定電流供給装置を提供する。

【解決手段】 定電圧出力用のNPN型トランジスタ21を備える定電圧回路2と、定電流供給用のPNP型トランジスタ31を備える定電流回路3とを組み合わせて定電流供給装置を構成する。定電流回路3の負荷として発光ダイオード11と抵抗12との直列回路を接続する。故障検出手段13は、発光ダイオード11の点灯/消灯状態とその状態での負荷電圧に基づいて定電流供給装置の故障を検出する。

(もっと読む)

入力回路およびそれを備える電子制御装置

【課題】 マイクロコンピュータなどのマイクロコンピュータの入力ポートを、スイッチなどの接地との間の複数の接点入力端で共用するために介在される入力回路において、前記接点入力端の接地電位からの浮きに対しても、正確に接点状態を判定できるようにする。

【解決手段】 各接点入力端IN1〜IN8に対して、ベースが接続されるトランジスタQ1〜Q8を設け、たとえば奇数番目と偶数番目とのように、複数のトランジスタをマイコン12のI/OポートP01,P02からの選択出力で纏めて選択/非選択し、かつ同時に選択されない複数のトランジスタQ1とQ2.Q3とQ4,Q5とQ6、Q7とQ8のコレクタ電流を共通の抵抗R1〜R4を用いて電圧変換し、I/OポートP1〜P4に与える。したがって、スイッチSW1〜SW8のオン抵抗などで、接地電位時に接点入力に浮きが生じても、正確に接点状態を判定することができる。

(もっと読む)

半導体装置

【課題】

過電流発生時、電源電圧が極端に低い場合であっても、出力トランジスタを確実にオフし、出力トランジスタの破壊を防止できる半導体装置を提供すること。

【解決手段】

本発明にかかる半導体装置は、ゲートG1に印加される信号に応じて出力電流を流す出力MOSトランジスタM0と、ゲートG1に接続されたMOSトランジスタM3と、出力MOSトランジスタM0に流れる電流を検出しMOSトランジスタM3のゲート端子に出力する第一の検出回路32と、出力MOSトランジスタM0に流れる電流を検出しMOSトランジスタM3のバックゲート端子に出力する第二の検出回路33と、を備え、第二の検出回路33は前記第一の検出回路32よりも低い電圧で動作するものである。

(もっと読む)

半導体回路

【課題】 LSIのパワーオルエリアの電源投入・遮断時に貫通電流や誤動作を発生させることなく、確実に電源遮断状態に移行させる。

【解決手段】 パワーオフエリアにマスクレジスタ19を設け、電源遮断の前にこのマスクレジスタ19に“L”のマスク信号をセットする。バックアップエリア側では、パワーオフエリアから与えられるマスク信号を保持すると共に、このマスク信号が無電圧状態となったときには“L”を保持するラッチ回路33Aを設け、このラッチ回路33Aで保持したマスク信号を用いて、パワーオフエリア側との間の入出力信号をマスクする。

(もっと読む)

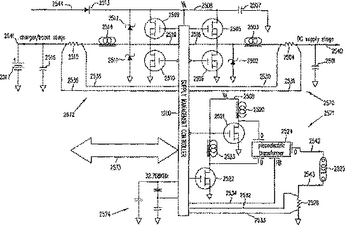

パワーコンバータ回路及び方法

複数のタイプが異なるスイッチングパワーコンバータの動作を同時に調整するコントロールシステムおよび方法。本システムは、パワーコンバータでサンプリングされたデータ及び非線形フィードバック制御ループの調整に用いる。  (もっと読む)

(もっと読む)

センサ信号処理装置

【課題】 コストの嵩むサンプリングホールド回路を設けることなく低コストで複数のアナログ信号の同時刻の値を1つのA/D変換器でデジタル値に変換する。

【解決手段】 センサから出力されるアナログ信号を複数系統に分岐して個別に処理する多重化された信号処理回路OP1,OP2と、該信号処理回路OP1,OP2から出力される複数の過渡的アナログ信号を、マルチプレクサ231を介して1つのA/D変換器232に入力し、当該A/D変換器232でデジタル信号に変換するようにしたセンサ信号処理装置において、前記複数の信号処理回路OP1,OP2と前記マルチプレクサ231との間に当該マルチプレクサ231の信号選択順番をNとし、前記A/D変換器232での1回のA/D変換処理時間をtとしたとき、(N−1)tの遅延時間に設定した遅延手段DLを介挿した。

(もっと読む)

情報処理装置及びその設定方法

【課題】

ユーザの使い勝手を格段と向上し得る情報処理装置及びその設定方法を提案する。

【解決手段】

外部入力による各種の操作内容に応じた処理を実行する情報処理装置及びその設定方法において、それぞれ所定の操作内容が割り当てられた複数の操作子のうち指定された各操作子を操作禁止対象として設定して記憶しておき、続いて各操作子からの入力を無効にするための設定スイッチがオン状態で、かつ複数の操作子のうち任意の操作子からの入力があったとき、記憶された設定内容に基づいて、当該操作子が操作禁止対象であるか否かを判断した後、当該判断結果に基づいて、操作された操作子が操作禁止対象である場合には当該操作子からの入力を無効にする一方、操作された操作子が操作禁止対象でない場合には当該操作子からの入力を有効にするようにした。

(もっと読む)

PWMモータ駆動回路

【課題】高速で小型、低損失で信頼性の高いPWMモータ駆動回路を実現する。

【解決手段】ソースを電源+VDDと接続したPチャンネルMOSFETトランジスタTru+ とソースをGNDと接続したNチャンネルMOSFETトランジスタTru- のドレインを接続し、モータコイルの出力とする。また、前記PチャンネルMOSトランジスタTru+ のソースとゲート間にバイアス抵抗R4を接続し、その抵抗R4と並列にソースとゲートを前記PチャンネルMOSトランジスタTru+ のオフ時に短絡するトランジスタQ2を設けるとともに、前記ゲートとコレクタを接続し、ベースを電源+VDDに接続した入力用のNPNトランジスタQ1のエミッタをマイコン2のポートP1に接続する。一方、前記NチャンネルMOSトランジスタTru- のゲートをマイコン2のポートP2と接続して両ポートP1、P2から駆動信号を入力する。この回路を用いることで簡便で高速動作ができて小型化が図れ、低損失で信頼性の高いPWMモータ駆動回路を実現する。

(もっと読む)

半導体集積回路

【課題】 高精度で内蔵発振を行うことができる半導体集積回路を提供する。

【解決手段】 半導体集積回路は、記憶回路(6)と、記憶回路に保持された制御情報に基いて内部クロック信号(VCLK)を生成する発振回路(23)と、外部クロック信号(RCLK)の周波数に内部クロック信号の周波数を一致させる制御情報を生成する論理回路(2)と、上記論理回路で生成された制御情報を記憶可能な電気ヒューズ回路又は溶断ヒューズ回路(6cd)を有し、上記内部クロック信号を内部回路の同期動作に用いる。プロセスばらつきにより発振回路の発振周特性(発振周波数)に誤差(不所望な変動)を生じても、水晶振動子の外付けや外部クロック信号の入力を必要とせずに、内部クロック信号周波数を目的周波数の外部クロック信号周波数に一致させることができる。

(もっと読む)

電力供給型パッチパネル

【解決手段】電力供給型通信用パッチパネルは、通信用パッチパネルに接続されたネットワークの装置に電力を供給するようになっている。電力は、電力供給型通信用パッチパネルにより通信用ケーブルを通してネットワークの装置に供給される。電力供給型通信用パッチパネルには、ネットワーク接続部を介してパッチパネルを遠隔管理できるようにするために、管理ポートが設けられている。多数の管理ポートを設けて、パッチパネルをデージーチェーン構成で互いに接続できるようにしてもよい。 (もっと読む)

妨害耐性を向上させるための方法及び集積回路

少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)と少なくとも一つの別のモジュール(2)との間で、誤り信号が一つ以上の誤り信号の形で伝送される、集積回路(16)の妨害耐性を改善する方法であって、その伝送に関して、このマイクロプロセッサ又はこれらのマイクロプロセッサのクロック周波数に依存しない最小パルス長を規定して、その最小パルス長以降において、誤り配線上で所定のパルス長を持つ信号を誤りと解釈する方法を記載している。また、この発明は、特に、前記の方法を実行するための集積回路であって、特に、分離して配置された電力部品を有する、少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)及び少なくとも一つの別のモジュール(2)と、少なくとも一つの誤り配線(3,4)を介して、誤りパルス(6,6’)を順番に出力するための一つ以上のパルス拡大機器と信号遅延機器の両方又は一方とを備えた集積回路に関する。  (もっと読む)

(もっと読む)

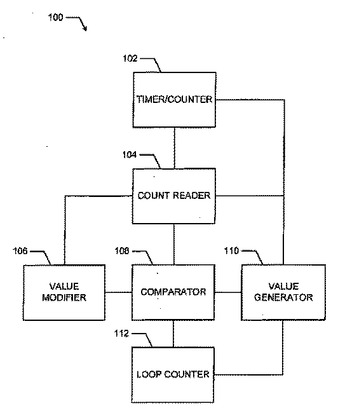

カウンタを用いて遅延を生成するための方法および装置

カウンタを用いて遅延時間を生成するための製造の複数の方法、装置、および複数の製品が開示される。特に、製造の前記複数の方法、装置、および複数の製品は、前記遅延時間に関連する複数のループの数の値およびカウンタに関連する少なくとも1つの特性値を決定する。残りのカウント値は、前記複数のループの数の値に基づいて、その後決定される。前記遅延時間は、前記カウンタと共に、前記複数のループの数の値および前記残りのカウント値に基づいて、生成される。

(もっと読む)

(もっと読む)

161 - 177 / 177

[ Back to top ]