Fターム[5J055EZ62]の内容

Fターム[5J055EZ62]に分類される特許

1 - 20 / 58

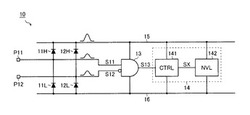

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

負荷駆動装置

【課題】短絡時にクランプ解除が為されてしまうことでスイッチングデバイスに過電流が流れることを防止する。

【解決手段】短絡状態が検出されたことを示す短絡信号Yが短絡検出フィルタ6を介することなくクランプ回路3に直接入力されるようにする。これにより、短絡時動作として、クランプ解除フィルタ時間の経過が短絡検出フィルタ時間の経過よりも先であった場合にも、クランプ回路3によるクランプ動作を継続することが可能となる。したがって、短絡時にクランプ解除が為されてしまうことでIGBT1に過電流が流れることを防止することができる負荷駆動装置とすることが可能となる。

(もっと読む)

誘導性負荷の駆動回路

【課題】スイッチング素子のオンオフによる誘導性負荷の電流応答性を良好なものとしながら駆動回路内の発熱をより抑制する。

【解決手段】誘導性負荷10を駆動する駆動回路20に、誘導性負荷10と並列接続され且つ互いに直列接続された第1の抵抗42および第2の抵抗44と、第2の抵抗44に並列接続されたコンデンサ46と、誘導性負荷10と並列接続されゲートが抵抗42と第2の抵抗44(コンデンサ46)との接続点に接続されドレインがグランドに接地されたNチャネル型のFET32と、FET32のソースと電源ライン24との間に介在しドレインからソースの方向を順方向とする第1のダイオード34とを設ける。

(もっと読む)

スイッチ回路及び半導体回路

【課題】 超音波診断装置等に適用され、送信信号または反射信号の電位変動に対しスイッチの誤動作や素子の破壊を起こすことなく、生体からの反射信号を広帯域、低雑音で受信回路に伝送するT/Rスイッチ回路を実現する。

【解決手段】 2つのMOSトランジスタのソースを共通に直列接続した共有ソース端子と、双方向スイッチ回路のゲート端子を共通に接続した共有ゲート端子と、2つのMOSトランジスタのドレインが入出力端子に接続されて構成される双方向スイッチ回路と、共有ゲート端子と共有ソース端子に接続され共有ソース端子の電位変動に対して共有ゲート端子の電位を同相で追従させ、スイッチのオンまたはオフ信号を共有ゲート端子に送るフローティングゲート電圧制御回路と、によりスイッチ回路を構成する。

(もっと読む)

負荷駆動装置

【課題】短絡保護のためのクランプ電圧の設定に基づいて、損失を抑制することが可能な負荷駆動装置を提供する。

【解決手段】IGBT1の温度、出力電流、ミラー電流もしくはゲート閾値電圧Vthを検出し、これらのいずれかに基づいてミラー電圧Vmirrorのバラツキに応じたクランプ電圧を演算する。これにより、クランプ電圧をその状況下でのミラー電圧Vmirrorに対応する値に低く抑えることが可能となり、クランプ電圧をミラー電圧Vmirrorのバラツキの最大値、つまりすべての環境変化等を含めた最大値を考慮して設計する場合と比較して、クランプ電圧を小さく抑えられる。したがって、クランプ時にIGBT1を損失が大きくなることを抑制しつつ、短絡耐量を向上することが可能となる。

(もっと読む)

スイッチおよびそのスイッチを用いたスイッチ回路

【課題】スイッチ用のトランジスタに発生する寄生ダイオードを介して内部に流入するESDによる負電流から内部回路を保護する。

【解決手段】第4nチャネルMOSFET(Mn4)は、ソース端子とバーグゲート端子間が接続されている。スイッチ素子は、第4nチャネルMOSFET(Mn4)のソース端子とグラウンド電位との間に接続され、第4nチャネルMOSFET(Mn4)のオフ時に第4nチャネルMOSFET(Mn4)のソース端子をグラウンド電位にする。保護回路40は、第4nチャネルMOSFET(Mn4)のソース端子と上記スイッチ素子の入力端子の接続点と、グラウンド電位との間に設けられ、静電気放電による第4nチャネルMOSFET(Mn4)のドレイン端子から流入する負電流をグラウンド電位に流す。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

電流駆動装置

【課題】駆動電圧を駆動回路へ安定的に供給しつつ、部品点数を少なくすることができる電流駆動装置を提供する。

【解決手段】パワートランジスタ3の主端子および制御端子が主端子接続端子13および制御端子接続端子14にそれぞれ接続されることにより、第1の電源4の電圧を所定の目標出力電圧に降圧する3端子レギュレータ10として機能する3端子レギュレータ構成回路12と、第1の電源4より低い電圧を出力する第2の電源6からの電力を用いて、3端子レギュレータ構成回路12がパワートランジスタ3の制御端子に印加する目標出力電圧に対応する制御電圧を設定する電圧設定回路18と、制御端子接続端子14に接続され、第1の電源4から電力が供給されると、3端子レギュレータ構成回路12の出力電圧VOUTが予め定められた電圧VC以下となるようにパワートランジスタ3の制御端子に印加される制御電圧を制御する電圧制限回路19とを備える。

(もっと読む)

電源電圧監視回路

【課題】簡易な回路で正確な出力信号を出力する電源電圧モニター回路を提供すること。

【解決手段】クランプ回路15で電圧がクランプされる前は第1の定電圧Vref1と電源電圧Vccの電位差を比較することなく、LレベルのRST信号を出力するが、クランプ回路15で電圧がクランプされた後は第1の差動回路13で第1の定電圧Vref1と電源電圧Vccの電位差を比較し、Hレベル又はLレベルのRST信号を出力することが可能となる。

(もっと読む)

電流検出回路

【課題】パワートランジスタの電流検出回路の保護用MOSFETにおいて基板バイアス効果が生じても、保護用MOSFETのソース−ゲート間の耐圧を満足したうえで、比較的高い電圧まで演算増幅器で負帰還して、精度よく負荷電流を検出する。

【解決手段】静電容量12とダイオード13を用いて、パワートランジスタ2のドレイン電圧の上昇時に、保護用MOSFET7のゲート電圧を上昇させる。電圧クランプ回路14は、保護用MOSFETのゲート電圧を所定のクランプ電圧Vcにクランプする。電圧制御回路17は、センストランジスタ6のドレイン電圧を、保護用MOSFET7のソース電圧に実質的に一致させる。検出回路40は、センストランジスタ6のドレイン電流を検出する。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子であって、ドレインとソースとゲートとを有し、前記ゲートをドライブする信号と前記ゲートとの間にコンデンサと抵抗の直列回路を介して接続され、前記ドレインと前記ゲートとの間に、ダイオードと電圧制限回路からなるゲート電圧クランプ回路とを備えることを特徴とする。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

半導体装置

【課題】素子が破壊されるほど高い電圧が印加された場合であっても、素子の破壊を抑制する。

【解決手段】第1の電圧が入力されることにより動作を行う半導体装置であって、第1の電圧の絶対値が基準値より大きいとき、第1の電圧の値を変化させる保護回路を具備し、保護回路は、第1の電圧に応じて第2の電圧を生成し、生成した第2の電圧を出力する制御信号生成回路と、電圧制御回路と、を備え、電圧制御回路は、ソース、ドレイン、及びゲートを有し、ゲートに制御信号として第2の電圧が入力され、第2の電圧に応じてオン状態又はオフ状態になることにより、第1の電圧の値をソース及びドレインの間に流れる電流量に応じて変化させるか否かを制御するトランジスタを含み、トランジスタは、チャネル形成層としての機能を有する酸化物半導体層をさらに有し、酸化物半導体層のバンドギャップは、2eV以上である。

(もっと読む)

駆動装置

【課題】低電圧駆動時の動作の信頼性を確保しながら動作速度を向上でき回路を保護できるようにする。

【解決手段】トランジスタQ7が動作するときには、当該トランジスタQ7による増幅回路がソース接地回路として動作する。MOSトランジスタQ7のゲート−ソース間にオン制御電圧が印加されたときには、当該トランジスタQ7のドレイン電位がソース電位に急速に近づき、急速にオン状態に遷移する。また、クランプ回路10がトランジスタQHのゲート−ソース間に設けられているため、当該ゲート−ソース間電圧が必要以上に上昇することがなくなる。この回路部分では、トランジスタQHの閾値電圧VT+トランジスタQ7のドレイン−ソース間電圧VDSのみで駆動できるため、低電圧駆動時でも動作の信頼性を確保できる。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GNDとの間に接続された負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源11の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN3と、電源10の極性が正常の場合に接地端子GNDと保護トランジスタMN3のバックゲートとを導通状態に制御するバックゲート制御回路17と、を備える。

(もっと読む)

1 - 20 / 58

[ Back to top ]