Fターム[5J055FX05]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還を行うもの (2,113) | 電気信号に変えられる現象、物理量 (2,102) | 電圧値 (1,457)

Fターム[5J055FX05]に分類される特許

1,441 - 1,457 / 1,457

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

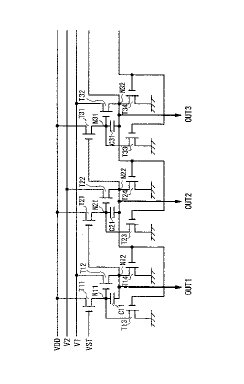

信号伝送回路、固体撮像装置、カメラおよび表示装置

【課題】回路電源を高速化または低電圧化しても安定な動作が可能で、高速化または低消費電力化に適した信号伝送回路を提供する。

【解決手段】複数の単位回路で構成され、駆動パルスに従って単位回路からパルス電圧が順次出力される。単位回路は、駆動パルスをドレインに入力して、パルス電圧としてソースから出力する第1の出力トランジスタ(T12)と、第1の出力トランジスタのゲートとソースとの間に接続された第1のブートストラップ容量(C11)と、第1のブートストラップ容量を充電するために、ソースが第1の出力トランジスタのゲートに接続され、ドレインが電源線または接地線あるいは充電パルス線に接続された充電トランジスタ(T11)と、一端が充電トランジスタのゲートに接続された第2のブートストラップ容量(C22)とを備える。

(もっと読む)

移相回路、高周波スイッチ並びに移相器

小型でかつ広帯域な特性を持つ移相回路を提供するもので、スルーとキャパシタンスの容量とを切り替える第1のスイッチング素子と、スルーとグランドに対するキャパシタンス

の容量とを切り替える第2のスイッチング素子と、インダクタンスをもつ第1および第2のインダクタとを備え、第1と第2のスイッチング素子の一端同士を第1のインダクタで接続し、第1と第2のスイッチング素子の他端同士を第2のインダクタで接続し、第1のスイッチング素子の一端を高周波信号入力端子に接続し、第1のスイッチング素子の他端を高周波信号出力端子に接続して、定の条件をを満たす移相器を構成する。

(もっと読む)

アクチュエータを制御するための電子装置

本発明は複数の誘導負荷を制御する装置に関する。この装置は、

複数の制御段から成る少なくとも1つの第1のグループと、

前記グループの制御段に共通した再導通化回路とを有しており、

前記制御段の各々は、

− 誘導負荷のためのボンディングパッドと、

− 導通化信号のための受信入力側と、

− 前記受信入力側に接続された制御電極と前記ボンディングパッドに接続された出力電極とを有するスイッチと、

− 前記ボンディングパッドに印加された電圧を測定し、該電圧がイネーブルレベルに達した場合にイネーブル信号を発生させるイネーブル回路を有しており、

前記再導通化回路は、前記グループの制御段のボンディングパッドにおける電圧を前記グループの各制御段のイネーブルレベルよりも高い共通のレベルに制限し、前記制御段のうちの1つのイネーブル回路がイネーブル信号を発生した場合に、導通化信号を該制御段のスイッチの制御電極に印加する。

本発明は、特に、ボンディングパッドに接続された負荷に対して同じ給電持続時間を保証するために使用することができる。  (もっと読む)

(もっと読む)

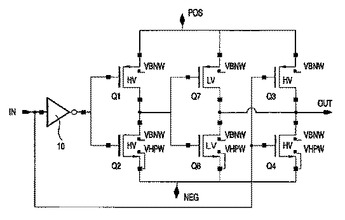

高速低電圧動作の高電圧駆動回路

不揮発性メモリなどの装置のための高電圧駆動回路。ここでは、低電圧ドライバが2つの異なる態様で高電圧ドライバと組み合わせられる。1つには、入力非依存型の実施例があり、低電圧ドライバ(Q7,Q8)が、高電圧ドライバと直接並列に接続され、これにより、高電圧動作のために高電圧信号パスを提供し、低電圧動作のために低電圧信号パスを提供する。代替の部分的入力依存型実施例では、低電圧ドライバが高電圧ドライバ(Q9,Q10)の出力に接続され、これが部分的レベルシフタ(Q1,Q6)を有することができる。この低電圧ドライバ(Q9,Q10)の出力は、全体のステージの出力端子を形成し、部分的レベルシフタ(Q1,Q6)が正又は負のレベルシフトの高電圧ドライバであるかどうかに基づいて、プルアップ/プルダウントランジスタ(Q11)を有する。

(もっと読む)

(もっと読む)

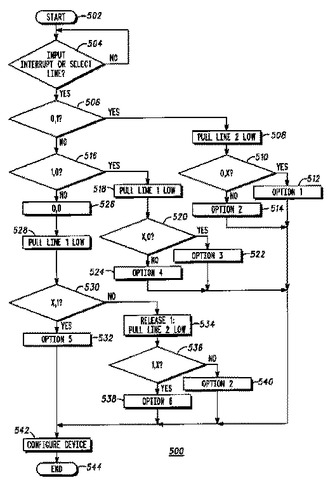

携帯機器のための割り込み駆動の拡張型オプション選択インタフェース

携帯電子機器(102)には周辺コンポーネント(104)が取り付けられ、この周辺コンポーネント(104)はオプション選択回路を使用して周辺コンポーネントのオプションクラスを示す。オプション選択回路は、携帯電子機器に割り込みを生成し、次いで種々のオプション論理ラインの論理レベルの変更により、オプションクラスを決定する。オプション選択ラインのうちの一つの論理状態の反転が検知されると、携帯電子機器はオプション選択回路のプレゼンスを知り、従って周辺コンポーネントのオプションクラスを決定する。  (もっと読む)

(もっと読む)

インバータ回路とこれを用いた圧電発振器

【課題】CMOSインバータの貫通電流は、このインバータを用いた装置の電力消費量を増大させ、特に携帯機器においては電池の寿命を短くする。

【解決手段】従来のCMOSインバータと同じ回路のP-MOSTQ1のソースS回路に、別のP-MOSTQ3を直列に追加接続し、そのゲートと回路の入力端間を遅延回路Z1で接続し、また、前記CMOSインバータのN-MOSTQ2のソース回路に、別のN-MOSTQ4を直列に追加接続してそのゲートと回路の入力端間を遅延回路Z2で接続した回路構成にする。

(もっと読む)

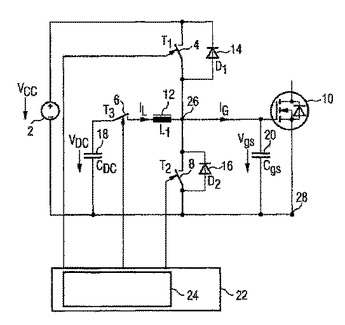

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

フェイルセイフな方法で誘導負荷を遮断するための装置および方法

【課題】誘導負荷54の遮断時の誘導電圧の大きさを監視することにより、誘導負荷54をフェイルセイフな方法で遮断する。

【解決手段】入力側の遮断信号20,22または24を受信すれば少なくとも1つのスイッチング素子26により負荷54を遮断する。遮断時に負荷54において誘導電圧Uiが発生するが、この誘導電圧Uiは閾値スイッチ38,40,41,44により制限されている。閾値スイッチ38,40,42,44は、監視回路68,70により監視されており、閾値スイッチ38,40,42,44の1つが故障すれば監視回路68,70において誤差信号が発生する。

(もっと読む)

スイッチ

第1のトランジスタ(1)及び第2のトランジスタ(2)を有するアナログ双方向スイッチ(20)は、スイッチ(20)の入力部又は出力部における信号電圧がスイッチ(20)を動作するのに使用される供給電圧を超過する場合に悪く機能する。スイッチ(20)に回路(21)を設けることにより、第2のトランジスタ(2)に向かうことになる第2の制御信号(“f”)は、もはや第1のトランジスタ(1)に向かうことになる第1の制御信号(“e”)を単に反転することにより生成されないが、第1の制御信号(“e”)に応答してスイッチ(20)の入出力部における入出力信号(“z”)を考慮することにより生成される。回路(21)は、固定値又は入出力信号(“z”)の値のいずれかを持つ第2の制御信号(“f”)を生成する生成器(22)を有し、入出力信号(“z”)を生成器(22)に供給する検出器(23)を有する。他の回路(24)は、第2のトランジスタ(2)に向かうことになるバックゲート信号(“bg”)を生成する他の生成器を有する。  (もっと読む)

(もっと読む)

信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅器及びプロセッサ

【解決手段】信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅及び処理回路が与えられる。入力データ信号は複数の信号利得に従って処理される。生成された信号は複数の信号値を有し、所定の下側及び上側閾値と比較される。所望の出力信号は、最大値が所定の下側閾値を横切らない場合には最大サンプル信号値であり、複数のサンプル信号値の内の隣接する大きいものが所定の上側閾値を横切る場合には最小サンプル信号値であり、一対のサンプル信号値の大きい方が所定の上側閾値を横切りかつ小さい方の値が所定の下側閾値を横切らない場合には複数のサンプル信号値の内の相互に隣接する一対の小さい方であり、大きい方の値が所定の下側閾値を横切りかつ所定の上側閾値を横切らない場合には一対のサンプル信号値の小さい方と大きい方との組み合わせである。 (もっと読む)

半導体スイッチの高周波制御

共振ゲート・ドライバ回路は、例えばMOSFETの効率的なスイッチングを実現する。しかし、共振ゲート・ドライバ回路の動作は、しばしば、高いスイッチング周波数が必要とされる応用分野を可能としない。本発明によれば、共振ゲート・ドライバ回路のインダクタのプリチャージが実行される。これは、MOSFETの非常に効率的かつ高速な動作を可能にする。  (もっと読む)

(もっと読む)

信号増幅用回路、及びアクティブマトリクス装置における同回路の使用

増幅回路はキャパシタ構造(42)と切替装置とを備える。キャパシタ構造は、電圧依存性静電容量を有する第一のキャパシタ(C2)と第二のキャパシタ(C1)(これもまた電圧依存性としてよい)とを有する。同回路は2つのモードで、すなわち少なくとも第一のキャパシタの一端子に入力電圧が提供される第一のモードと、切替装置によって第一及び第二のキャパシタ同士の間で電荷の再配分が起こることにより、第一のキャパシタにかかる電圧が変化し第一のキャパシタの静電容量が減少し、出力電圧が第一のキャパシタにかかる電圧に依存する第二のモードとで、動作可能である。本発明は電圧制御静電容量をキャパシタ間の電荷共有と併せて使用するものであり、これにより、結果的に電圧増幅特性が提供される。よってこの機構は、アナログ電圧の増幅に、または固定レベル(すなわちデジタル電圧)の昇圧に利用できる。よって本発明の回路は、レベルシフトまたは増幅のために、例えばアクティブマトリクスアレイ装置のピクセルでの用途に使用できる。  (もっと読む)

(もっと読む)

電力変換回路及び電力制御回路の動作及び回路

通常、並列なMOSFETは、電源用途において単一のゲート信号で駆動されるため、MOSFET間のカレントシェアリングが個々のMOSFETの特性に関して自動的に規定される。これは、MOSFET間の電流分布の大規模な非均一性をもたらす可能性がある。本発明によれば、MOSFETのオン抵抗の個々の制御が与えられ、このことが、並列化されたMOSFET間での改善されたカレントシェアリングを可能にする。  (もっと読む)

(もっと読む)

吸収性マイクロ波単極単投スイッチ

【解決手段】本発明のスイッチ回路は、分離チャンネルの一部を供給する第1差動増幅器対(Q1,Q2)と、送信チャンネルの一部を供給する第2差動増幅器対(Q3,Q4)と、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを供給する第3差動増幅器対(Q5,Q6)とを具備する。このスイッチ回路は、500μm×250μmの小寸法でありながら、15GHz〜26GHzレンジにわたる入力及び出力間に35dBの分離を提供する。  (もっと読む)

(もっと読む)

スイッチング回路における不感時間制御

DC−DC変換器は、入力端子(37)と接地端子(38)との間に直列に接続された2つの電界効果トランジスタ(35,36)を有する。両方のトランジスタ(35,36)がオフとなるときの不感時間の調整は、トランジスタ(35,36)の一方又は双方のドレイン(39,44)及びソース(43,40)に直接かけられてケルビンフィードバック接続部(71,72,67,68)を設けることによって行い、信号ラインの抵抗及びインダクタンスを回避するようにしている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 フィールドスルー電荷補償機能を備えるアナログスイッチにおいて、半導体製造工程の誤差によらず、スィッチング用のMOSトランジスタのフィールドスルー電荷を安定に補償し、アナログスイッチ動作時の入出力間の誤差を低減できる構造を実現する。

【解決手段】 入力端子INと出力端子OUTの間に同一サイズの2つのトランジスタ1a、1bを、電気的に並列に、また物理的には相対するように配置し、トランジスタ1a、1bの入力端子IN側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ2を配置し、トランジスタ1a、1bの出力端子OUT側に、トランジスタ1a、1bと同一サイズで、そのソースとドレインを共通接続されたトランジスタ3を配置し、製造工程の誤差によって、位置ずれが発生しても、トランジスタ1a、1bのソース側の寄生容量の総和および、ドレイン側の寄生容量の総和が不変であるようにし、トランジスタ1a、1bのスィッチング動作に伴うフィールドスルー電荷の補償が、設計通りにできるようにした。

(もっと読む)

1,441 - 1,457 / 1,457

[ Back to top ]