Fターム[5J055GX08]の内容

Fターム[5J055GX08]に分類される特許

1 - 20 / 190

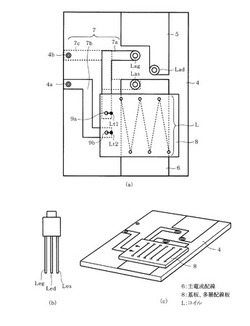

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】発光装置に含まれる発光素子の発光輝度を周囲の情報に応じて調節する表示シス

テムを提供する。

【解決手段】本発明において、センサー2011が周囲の情報を電気信号として検出し、

これをCPU2013は、あらかじめ設定しておいた比較データに基づきEL素子の発光

輝度を補正するための補正信号に変換する。この補正信号が電圧可変器2010に入力さ

れることにより、電圧可変器2010が所定の補正電位をEL素子に印加する。以上の表

示システムによりEL素子2003の発光輝度を制御することができる。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

スイッチング回路装置及び制御回路

【課題】スイッチングトランジスタを適切にオフ動作する。

【解決手段】スイッチング回路装置は,高電位端子に接続されたドレインと低電位電源に接続されたソースとゲートとを有し,高電位端子と低電位電源との間に接続されたスイッチングトランジスタと,入力制御信号に応答して,スイッチングトランジスタのゲートにスイッチングトランジスタの閾値電圧より高い高電位と前記低電位電源の電位とを有する駆動パルスを出力する駆動回路とを有し,駆動回路は,スイッチングトランジスタのゲートとソースとの間に設けられた第1の駆動トランジスタを含む第1のインバータを有し,駆動パルスにより前記スイッチングトランジスタがオンからオフに変化するときに,第1の駆動トランジスタが導通してスイッチングトランジスタのゲートとソース間を短絡する。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

窒化物半導体装置

【課題】駆動回路への要求を緩和した使いやすい高速動作の窒化物半導体装置を提供する。

【解決手段】実施形態によれば、窒化物半導体を含む、nチャンネル型の第1〜第4トランジスタと、抵抗と、を備えた窒化物半導体装置が提供される。第1トランジスタは、第1ゲートと、第1ソースと、第1ドレインと、を有する。第2トランジスタは、第2ゲートと、第1ゲートと接続された第2ソースと、第2ドレインと、を有する。第3トランジスタは、第3ゲートと、第1ソースと接続された第3ソースと、第1ゲート及び第2ソースと接続された第3ドレインと、を有する。第4トランジスタは、第3ゲートと接続された第4ゲートと、第1ソース及び第3ソースと接続された第4ソースと、第2ゲートと接続された第4ドレインと、を有する。抵抗の一端は第2ドレインと接続され、他端は第2ゲート及び第4ドレインと接続される。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

高周波モジュールおよび無線通信システム

【課題】低コスト化または小型化を実現可能なマルチバンド対応の高周波モジュールおよび無線通信システムを提供する。

【解決手段】例えば、高周波電力増幅装置HPAIC1は、GSM用のパワーアンプ回路部PABK_LB(PABK_HB)と、GSMかW−CDMAかを選択するモード設定信号Mctlを受けて、アンテナスイッチ制御信号SctlをVSW1レベルかVSW2レベルで出力する制御回路を備える。VSW2は、発振回路OSCからのクロック信号を用いてVSW1を昇圧することで生成される。HPAIC1は、MctlによってGSMが選択された際には、OSCを停止させると共にVSW1レベルのSctlをアンテナスイッチ装置ANTSWに出力し、MctlによってW−CDMAが選択された際には、OSCを用いてVSW2レベルのSctlをANTSWに出力する。

(もっと読む)

半導体装置

【課題】本発明の実施形態は、高パワーの高周波信号に対する耐圧を維持しながら小型化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、絶縁膜の上の半導体層に設けられたFETを含むスイッチ回路を有する半導体装置であって、前記FETのソース領域とドレイン領域との間に、前記ソース領域から前記ドレイン領域に向かう方向に並んで設けられた第1のゲート電極および第2のゲート電極と、前記第1のゲート電極と前記第2のゲート電極との間の中間領域に電気的に接続された制御端子と、を備える。前記FETは、前記第1のゲート電極および前記第2のゲート電極に供給されるゲート電圧によりON/OFF制御され、前記FETがON状態にある時、前記制御端子をアース電位とし、前記FETがOFF状態にある時、前記制御端子を正電位または負電位とする。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

1 - 20 / 190

[ Back to top ]