Fターム[5J056BB44]の内容

Fターム[5J056BB44]に分類される特許

1 - 20 / 22

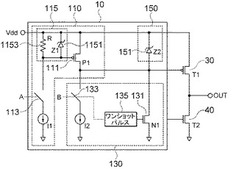

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

信号入力回路

【課題】信号入力端子のプルアップ機能を有したまま、信号入力端子に入力する信号電圧が高電位電源端子の電圧を超えるときがあっても、上記したような問題が生じないようにした信号入力回路を提供する。

【解決手段】エンハンスメント型NMOSトランジスタMN1のバックゲートを低電位電源端子2に接続し、ドレインとゲートを高電位電源端子1に接続し、ソースを信号入力端子3に接続する。エンハンスメント型NMOSトランジスタMN1のオン抵抗を、信号入力端子3に接続される前段回路のドライバの“L”レベル電圧出力時の出力インピーダンスよりも高い値に設定する。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

半導体チップ

【課題】動作電圧が互いに異なる半導体チップを接続して用いる場合、双方に、自身の動

作電圧と異なる電圧で動作する入出力バッファ回路を設ける必要があり、チップ面積が大

きくなってしまう。

【解決手段】本発明にかかる半導体装置は、第1電源電圧で動作する第1半導体チップと、前記第1電源電圧よりも低い第2電源電圧で動作し、当該第2電源電圧を前記第1半導体チップに供給する第2半導体チップとを有することを特徴とする。又は、かかる半導体装置の製造に用いるのに好適な半導体チップとして、本発明にかかる半導体チップは、互いに直列に接続され、互いに相補的にオンとオフが切り替わる第1および第2トランジスタを有し、第1外部端子へ信号を出力する出力回路と、前記第1および第2トランジスタと直列に接続され、第2外部端子にゲート電極が接続された第3トランジスタとを有することを特徴とする。

(もっと読む)

カップリング回路、このカップリング回路を含むドライバ回路、およびこのカップリング回路の制御方法

【解決手段】p−チャネル電界効果トランジスタタイプの第1および第2のトランジスタ(P1,P2)を備えるカップリング回路において、第1のトランジスタ(P1)のドレイン端子は信号入力端子(1)に接続し、第1および第2のトランジスタ(P1,P2)のソース端子はともに信号出力端子(2)に接続し、第1および第2のトランジスタ(P1,P2)のバルク端子はともに第2のトランジスタ(P2)のドレイン端子に接続し、第1のトランジスタ(P1)のゲート端子は第2のトランジスタ(P2)のゲート端子に接続する。このカップリング回路には、さらに 負電圧を生成する電荷ポンプ回路(110)を含むゲート制御回路(10)も設ける。このゲート制御回路(10)は、負電圧に基づいて、第1および第2のトランジスタ(P1,P2)のゲート端子におけるゲート電圧を制御する。 (もっと読む)

データ通信回路、送信機器、受信機器、送受信システム

【課題】データ通信回路において電圧緩和トランジスタの耐圧破壊を抑制する。

【解決手段】ドライバ(101)は、供給ノード(N101)を介してデータ信号を供給する。電圧緩和トランジスタ(102)は、ドライバの供給ノード(N101)に接続されたソースと、信号線に接続される信号ノード(N1)に接続されたドレインと、信号ノード(N1)の電圧(V1)が与えられるゲートとを有する。

(もっと読む)

2つのマスタと1つ以上のスレーブとの間の信号伝送のための電気回路

2つのマスタ(11、12)と1つ以上のスレーブ(13、14)との間の信号伝送のための電気回路(10)が記載される。2つのマスタ(11、12)と1つ以上のスレーブ(13、14)とは、バスシステム(15)を介して互いに接続される。2つのマスタ(11、12)によって、1つ以上のスレーブ(13、14)により受信されうるマスタデータ信号(MO)が少なくとも1つずつ生成可能である。各マスタデータ信号(MO)が印加される2つのマスタ(11、12)の出力口には、三状態ゲート(16)が1つずつ存在する。三状態ゲート(16)は、閉回路又は開回路として作動可能である。三状態ゲート(16)は、2つのマスタの一方(11)に割り当てられた三状態ゲート(1611)が閉回路として作動し、2つのマスタの他方(12)に割り当てられた三状態ゲート(1612)が開回路として作動するように、駆動される。 (もっと読む)

入出力回路

【課題】消費電力の増大を防止することが可能な入出力回路を提供する。

【解決手段】本発明の入出力回路は、信号の入力部に接続された第1トランジスタと、前記第1トランジスタのゲートに接続されたノードの電位を制御するための第2トランジスタと、所定電圧に基づいて前記第2トランジスタを制御するためのバイアス電圧を生成し、当該バイアス電圧を前記第2トランジスタのゲートに印加するバイアス回路と、前記入力部と出力端子との間に設けられたインバータと、一方の入力に内部電圧が印加され、他方の入力に前記インバータの出力が接続された排他的論理積回路と、前記第1トランジスタのゲートと前記排他的論理積回路との間に設けられ、前記入力部の電位に基づいて前記第1トランジスタのゲートと前記排他的論理積回路との接続を導通/遮断するトランスファゲートとを有することを特徴とする。

(もっと読む)

出力回路及び表示装置の駆動回路

【課題】出力回路の出力部の電圧降下を抑制すると共に、出力回路の入力部へ帰還される出力信号の位相の遅れを抑制することができる。

【解決手段】入力信号が入力されたオペアンプ30の出力端子(OUT)から出力されたデータ信号の交流成分は、コンデンサ34を介して負帰還されてオペアンプ30の反転入力端子へ入力される。また、オペアンプ30の出力端子(OUT)から出力されたデータ信号の直流成分は、第2の保護抵抗36によって電圧降下し、入力信号と同電位の出力信号となって出力パッド28を介して対応するデータ線20へ入力されると共に、第1の保護抵抗32を介してオペアンプ30の反転入力端子へ入力される。

(もっと読む)

半導体装置

【課題】プロセス工程及び開発期間を減らし、サイズを小さくすることができる静電気放電保護回路を有する半導体装置を提供することを課題とする。

【解決手段】入出力パッド(101)と、電源電圧が供給される電源電圧ノード(VDE)と、基準電位が供給される基準電位ノード(GND)と、アノードが前記入出力パッドに接続され、カソードが第1のノードに接続される第1のダイオード(131)と、前記入出力パッド及び前記電源電圧ノードに接続され、前記入出力パッドに前記電源電圧より低い電圧が入力されると、前記第1のノードが前記電源電圧になるように制御する電位制御回路(103)と、前記入出力パッドに静電気が入力されると静電気オン信号を出力するトリガ回路(109)と、前記静電気オン信号が出力されると、前記第1のノード及び前記基準電位ノード間に静電気放電電流を流す静電気放電サージパス回路(108)とを有する。

(もっと読む)

出力回路及び多出力回路

【課題】出力端子からツェナーダイオードを通してレベルシフト回路へ負荷電流が流れる経路を遮断して、出力端子を完全にハイインピーダンスにする出力回路を提供する。

【解決手段】出力回路は、ハイサイドトランジスタ13と、ローサイドトランジスタ14と、ゲート保護回路10と、レベルシフト回路8と、プリドライバ回路7とを備える。レベルシフト回路8は、ハイサイドトランジスタ13をオフさせてから所定時間経過後に、出力端子4からレベルシフト回路8への電流径路を遮断状態にする。

(もっと読む)

トランジスタスナップバック保護を組み込むレベルシフタ回路

第1の電圧領域に対応する入力信号をレベルシフトして、より高い第2の電圧領域に対応する一対の相補出力信号を発生するレベルシフタ回路を開示する。出力ノード上のローディングに関係なく、出力ローディングに応じて正確なトランジスタサイジングを必要とすることなく、高電圧出力ノード用の放電回路におけるスナップバック感知素子が保護される。スナップバック感知素子は、スナップバック感知素子と直列の電圧シフタ回路によって保護されて、その最高出力電圧での高容量出力ノードにおいてさえ、スナップバック感知素子への電圧を制限する。電圧シフタ回路は、次いでバイパスされて、低電源レールに十分に達する出力ローレベルをもたらす。  (もっと読む)

(もっと読む)

通信システムおよび通信端末

【課題】複数のノードそれぞれが単線の通信路に接続されてなる通信システムにおいて、ショートが発生した場合に各ノードのスリーステート素子が破損することを防止する。

【解決手段】各ノード2のH側経路56およびL側経路58を流れる電流を電流制限回路46,48により制限するため、その経路がショートして大きな電流が流れうる状況になっても、その定められた制限値より大きな電流が流れることはない。この制限値は、スリーステート素子42を形成するトランジスタTr1,Tr2に流すことのできるコレクタ電流の最大定格値以下に設定されているため、H側経路56,L側経路58または通信路3にショートが発生しても、各ノード2のスリーステート素子42を構成するトランジスタTr1,Tr2が破損するような電流が流れることを防止でき、その結果、各ノード2のスリーステート素子42が破損してしまうことを防止できる。

(もっと読む)

I/O回路

【課題】 接地側のNMOSドライバを小さな面積で、かつ、接地側のNMOSドライバの活性化の遷移時間を短くし、接地側のNMOSドライバのゲート電圧をより確実に接地電位にするI/O回路を提供すること

【解決手段】 I/O回路1は、ドレインがパッドに接続される第1NMOSドライバ10と、第1NMOSドライバ10と異なるアクティブ領域に配置され、ドレインが第1NMOSドライバ10のソースに接続され、ソースが接地電位に接続される第2NMOSドライバ11と、内部電源電位のレベルを電源電位のレベルに変換するレベルコンバータと、ドレインがレベルコンバータの一方の出力端子に接続され、ソースが接地電位に接続され、ゲートがレベルコンバータの他方の出力端子に接続される第1NMOSトランジスタ26と、を備えており、第1NMOSトランジスタ26のドレインが第2NMOS11ドライバのゲートに接続されている。

(もっと読む)

レベルシフタ回路及びそれを具備する半導体集積回路

【課題】回路素子の破壊等を防止することが可能なレベルシフタ回路を提供する。

【解決手段】レベルシフタ回路10は、レベル変換回路20と、保護回路30とを含んでいる。保護回路30は、電源電位供給回路31と、プルダウン回路32とを含んでいる。制御信号がアサートされている場合、電源電位供給回路31は、レベル変換回路20への電源の供給を行い、レベル変換回路20は、入力信号のレベルを変換した出力信号を生成する。制御信号がネゲートされている場合、電源電位供給回路31は、レベル変換回路20への電源の供給を行わず、プルダウン回路32は、出力信号をプルダウンする。

(もっと読む)

酸化物薄膜電界効果トランジスタを使用したデジタル出力ドライバおよび入力バッファー

デジタル出力ドライバは、薄い酸化物FETを用いて実装されてよいプレドライバおよびドライバを含んでいる。プレドライバは、デジタル入力信号にもとづいて、第一および第二のデジタル信号を発生する。第一のデジタル信号波、第一(例えばパッド)の供給電圧および中間電圧によって決定される第一の電圧範囲を有している。第二のデジタル信号は、第二(例えばコア)の供給電圧および回路アースによって決定される第二の電圧範囲を有している。ドライバは、前記第一および第二のデジタル信号を受信して、前記第一の供給電圧および回路アースによって決定される第三の電圧範囲を有するデジタル出力信号を与える。プレドライバは、ラッチおよびラッチドライバを含んでよい。ラッチは、デジタル入力信号についての現在の論理値を保存する。ラッチドライバは、該論理血をラッチに書込む。ラッチドライバは、論理値を書込むために短い持続時間だけ可能にされ、その後にオフされる。 (もっと読む)

高電圧耐性ポートドライバ

高電圧耐性ドライバ(200;300)は、過電圧に耐え、高い電圧レベルへの電気接続を持続し、出力電圧を固有の供給レベルで生成することができる、複数の出力駆動デバイスを含む。初期プルアップ駆動回路(204)は、複数の出力駆動デバイスに結合され、その複数の出力駆動デバイス(235a〜c、275a〜c)に対し、初期高駆動電圧を生成する。持続プルアップ回路(260、360)は、複数の出力駆動デバイスに結合され、持続された出力電圧を固有の供給レベルで生成する。  (もっと読む)

(もっと読む)

出力バッファ回路

【課題】 内部回路に供給される高電位側電源が未投入の場合でも、出力バッファ回路の誤動作や貫通電流の発生を抑制する。

【解決手段】 半導体集積回路1には、内部回路部11、出力バッファ回路部12、及び出力レベル制御部3が設けられている。内部回路部11には第1の高電位側電源Vdd1が供給され、出力バッファ回路部12には第2の高電位側電源が供給される。第1の高電位側電源Vdd1が未投入、第2の高電位側電源Vdd2が投入の場合、出力レベル制御部3は出力バッファ回路部12から出力される出力信号OUTを所定のレベルに制御する。

(もっと読む)

半導体集積回路

【課題】クロック遅延の抑制という観点より、外部クロック信号に同期する外部出力動作の高速化を実現する。

【解決手段】半導体集積回路は、外部出力バッファ(53)と、前記外部出力バッファから出力すべきデータを外部クロック信号(100)に同期してラッチするラッチ回路(90)と、前記ラッチ回路にラッチすべきデータの処理回路(20)とを有する。前記ラッチ回路と前記処理回路は前記外部クロック信号を受けるクロックバッファ(101)の出力を共通に入力する。前記ラッチ回路が外部からのクロック信号を受けて出力ラッチ動作を行なうことにより、外部クロック信号に同期する出力動作において内部クロック遅延の影響を小さくすることが可能になる。

(もっと読む)

半導体集積回路

【課題】 電源電位が供給されていないときに回路素子の耐圧よりも高い電圧が外部からパッドに印加されても、簡単な構成で、耐圧オーバーによる回路素子の破壊やリーク電流を阻止する。

【解決手段】 この半導体集積回路は、ノードN2に信号を出力する出力ドライバ10、及び/又は、ノードN2に入力された信号をバッファする入力バッファ20と、第2のノードとパッドとの間にドレイン・ソース経路が接続されたトランジスタQN12と、パッドの電位が電源配線の電位よりも高いときにパッドの電位を降下させてトランジスタQN12のゲートに供給するダイオードD1と、パッドから電源配線へのリーク電流を阻止すると共に、パッドの電位が電源配線の電位よりも低いときに電源配線の電位を降下させてトランジスタQN12のゲートに供給するダイオードD2とを具備する。

(もっと読む)

1 - 20 / 22

[ Back to top ]