Fターム[5J056BB58]の内容

Fターム[5J056BB58]に分類される特許

81 - 100 / 102

基板の両面に実装可能な集積回路装置及び電子機器

【課題】基板の両面いずれにも実装可能なインターフェース回路を備えた集積回路装置及び電子機器を提供すること。

【解決手段】集積回路装置20は、第1〜第4の端子101〜104の中心軸CLに対して第1及び第4の端子101,104が線対称に配置され、中心軸に対して第2及び第3の端子が線対称102,103に配置され、基板の表面及び裏面の双方のいずれかに選択して実装できる。第1の送信回路250では、第1及び第2の差動信号対(DP1,DM1)(DM1,DP1)の一方が出力され、第2の受信回路252では、第1及び第2の作動信号対の他方が出力される。第1及び第2のセレクタ230,232からの各出力は、セレクト信号SELに基づいて、第1の送信回路及び第2の送信回路に切り換えて出力する。

(もっと読む)

信号出力回路及び半導体集積回路

【課題】入力信号を基準電圧の異なる信号を出力する信号出力回路に関し、異なる基準電圧で駆動される複数の回路を容易に結合できる信号出力回路を提供することを目的とする。

【解決手段】本発明は、第1の基準電圧(V01)を基準として駆動される第1の回路(112)からの信号を第2の基準電圧(V02)を基準として駆動される第2の回路(113)に出力する信号出力回路であって、第1の回路(112)からの出力信号に応じて第1の基準電圧(V01)に電流を引き込み、引き込まれた電流に応じて第2の回路(113)に信号を供給する第1の制御回路(121、122、Q11、R11、Q12)と、第2の回路(113)から第2の基準電圧(V02)に電流を引き込む第2の制御回路(Q13、R12)とを有することを特徴とする。

(もっと読む)

単一電流を用いる二出力差動線路ドライバ

ボックススイッチはスタックされて電源からの共通電流を共用する。電源は、電流源、または、電圧源、または電流源と電圧源の組み合わせとすることができる。好適な実施形態では、ボックススイッチ内のトランジスタスイッチを、より良好な平衡状態になるよう動作させ、かつ、出力信号を対称にする極性の異なるトランジスタと並列配置することができる。コンデンサを用いて残留ノイズ電圧信号を除去することができる。  (もっと読む)

(もっと読む)

信号出力回路

【課題】LVDS出力回路と二値化出力回路との統合によって面積削減を行い、出力部分の負荷を軽減し、出力信号の特性の向上を図る。

【解決手段】2個の入力103,104と、2個の出力105,106とを持つ信号出力回路100の内部構成が、LVDS信号出力回路101の内部に二値化信号出力回路102を含んだ構成、又は二値化信号出力回路102をベースにLVDS信号出力回路101としての機能を付加したものである。それら2つの機能を、出力形式切り替え信号107によって選択して出力させる。2系統の出力信号の切り替えは、回路内部の制御信号の流れを切り替えるだけで可能となり、従来の出力部分にあった切り替え用のスイッチは不要となる。

(もっと読む)

四端子二重絶縁ゲート電界トランジスタを用いたCMOS増幅器、それを用いた多入力CMOS増幅器、高利得多入力CMOS増幅器、高利得高安定多入力CMOS増幅器および多入力CMOS差動増幅器

【課題】 増幅器の入力インピーダンスに制限を加えず、入力オフセット電圧Vofsによる増幅段数の制限をなくし、信号入力経路に悪影響を及ぼすことがないようにした四端子二重絶縁ゲート電界トランジスタを用いたCMOS増幅器、それを用いた多入力CMOS増幅器、高利得多入力CMOS増幅器、高利得高安定多入力CMOS増幅器および多入力CMOS差動増幅器を提供することにある。

【解決手段】 P形およびN形の四端子二重絶縁ゲート電界効果トランジスタを用い、それぞれのドレインを共通接続して出力端子とし、それぞれの第一のゲートを接続して第一の入力端子とし、それぞれの第二のゲートを接続して第二の入力端子とするCMOS増幅器を構成する。このCMOS増幅器を複数個用い、その各出力端子を接続して一つの出力端子とし、各CMOS増幅器の入力端子は同複数個の2倍の独立した入力端子として用いて多入力CMOS増幅器を構成する。

(もっと読む)

オンダイターミネーションの制御方法及びそれに係る制御回路

【課題】オンダイターミネーションが動作する周波数に関係なく、遅延固定ループクロックと内部クロックとの間のクロックドメインエラーを解決し、所望のタイミングにオンダイターミネーション動作を行うことができるオンダイターミネーション制御方法及びそれに係る制御回路を提供する。

【解決手段】外部クロック及び遅延固定ループクロックを受信して、それぞれのクロックがトグルされる数を設定された値からカウントするカウンタ部と、オンダイターミネーション命令信号に応答し、前記外部クロックカウント値と前記遅延固定ループカウント値とを比較し、その値に応じてオンダイターミネーションの動作を制御する比較制御部とを備える。

(もっと読む)

適応型入力セル回路

入力セルを動作する方法であって、前記方法は、センサー入力信号、デジタル・バイアスの第1の制御入力及び第2の制御入力を受信する段階、及び前記第1の制御入力のバイアスが第1のデジタル状態である場合に第1の抵抗器回路を用いセンサー入力信号へアナログ・プルアップ・バイアスを加える段階、を有する。第1の抵抗器回路の少なくとも一部に接地への経路を設け、第1の制御入力が第2のデジタル状態のバイアスである場合に、第1の抵抗器回路にセンサー入力へプルダウン・バイアスを加えさせる。方法は、電圧基準及び入力波形信号を受信する段階、第2の制御入力のバイアスが第1のデジタル状態である場合に、第2の抵抗器回路を用い入力波形信号を比較器に加え、及び第2の制御入力のバイアスが第2のデジタル状態である場合に、バイアス及び減衰された入力波形信号を比較器に加える段階、を有する。方法は、バイアスされたセンサー入力信号を第2の抵抗器回路により加えられた波形と比較し、入力セル出力を決定し、従って入力セルはセンサー入力信号を時間に基づくパラメーターに変換できる。  (もっと読む)

(もっと読む)

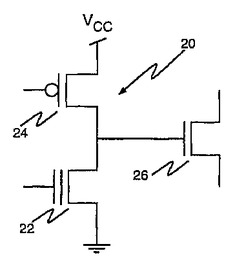

プログラマブルロジックアレイ用不揮発性プログラマブルメモリセル

プログラマブルロジックアレイに用いるために適した不揮発性プログラマブルメモリセルは、第2導電型の揮発性MOSトランジスタ24と直列に、第1導電型の不揮発性MOSトランジスタ22を具備する。不揮発性MOSトランジスタ22は、フラッシュトランジスタのようなフローティングゲートトランジスタであるか、又はフローティング電荷トラッピングSONOS、MONOSトランジスタ、若しくはナノ結晶トランジスタのような別のタイプの不揮発性トランジスタであってもよい。揮発性MOSトランジスタ、インバータ、又はバッファ26は、そのゲート又は入力を、不揮発性MOSトランジスタ22と揮発性MOSトランジスタ24との間のコモン接続点に接続することによって駆動される。  (もっと読む)

(もっと読む)

半導体装置

【課題】論理回路の入出力データをクロックに同期してラッチする同期式回路の動作環境範囲を拡大する。

【解決手段】論理回路5と出力ラッチ回路2の間に、論理回路5の出力データを遅延する可変遅延回路10を設け、この可変遅延回路10の遅延量を観測された動作環境に基づき制御する制御回路6を備える。動作環境として、温度、プロセス変動に伴う回路素子の遅延、電源電圧等を観測する。可変遅延回路10に代えて、ラッチ回路2のクロックCKを遅延する可変遅延回路を設けてもよい。可変遅延回路10の採る複数の遅延量の各遅延量ごとに一つの動作範囲が許容され、半導体装置はその全動作範囲で動作するので動作範囲が広くなる。

(もっと読む)

出力レベル電圧調整

ピン出力レベルを基準レベル(60)に適合させる回路において、デジタル比較器(20)はデバイスの出力ピンからの出力電圧(40)を基準電圧レベル(60)と比較する。比較器(20)は比較器出力(50、52)の極性および前のクロック周期の比較器出力の登録された極性に依拠して信号を状態マシン(22)へ送り、状態マシンは、クロック制御された信号をセンス回路(21)および電圧レギュレータ(30)へ送る。センス回路(21)は、誤差信号の極性が逆になるまで、クロック制御された間隔で基準電圧(60)に向けて出力レベルに漸進的に段を付けるようスイッチ抵抗のネットワーク(28)内の抵抗を修正することができる。出力電圧(40)が基準電圧(60)閾値を横切ると、比較器(20)は状態を反転させ、出力ピン電圧を基準電圧レベル(60)へ調整し続ける。  (もっと読む)

(もっと読む)

レベル生成装置

【課題】 100V超の高耐圧素子を用い、かつ容量性負荷を駆動させる場合でも、ハイレベルとミドルレベルの間の電位差を高耐圧素子の耐圧の範囲内で、自由に設定することを目的とする。

【解決手段】 各ドレインが出力端子4に接続された、ハイレベルトランジスタ6とミドルレベルトランジスタ7とロウレベルトランジスタ8の3個のトランジスタを有し、それぞれオン時にハイレベル、ミドルレベル、ロウレベルを出力する。さらにミドルレベルトランジスタ7と出力端子4の間に、カソードが出力端子4に接続された逆流防止ダイオード29を備える。

(もっと読む)

半導体装置及びその駆動方法

【課題】複数のインタフェースとの互換性をシステムレベルで構成する半導体装置及びその駆動方法を提供する。

【解決手段】インタフェース制御回路及びインタフェース従属回路を具備する。インタフェース制御回路は、使用者の要求に応じてインタフェース選択モードが設定されると、複数のインタフェースイネーブル信号のうち該当するインタフェースイネーブル信号をアクティブにする。インタフェース従属回路は、複数のインタフェースイネーブル信号を入力し、複数のインタフェースのうちどのインタフェースに互換性を持たせるのかを感知し、これに従って適合した動作を行う。従って、複数のインタフェースに対する互換性をボンディングオプションによらずシステムレベルで構成することができる。

(もっと読む)

抵抗回路、増幅器および分圧出力器

【課題】電気抵抗素子に対して並列接続されたスイッチング素子を備えた抵抗回路において、スイッチング素子の寄生容量に起因したインピーダンスの周波数依存性を緩和または解消した抵抗回路を実現する。

【解決手段】電気信号入力のための入力端1と、所定の抵抗値を有する電気抵抗素子2と、電気抵抗素子2に対して並列に接続した迂回経路3と、迂回経路3の電気的導通を制御するスイッチング素子4と、電気抵抗素子2に対して直列に接続されたインダクタンス素子5と、外部に出力するための出力端6とを備える。インダクタンス素子5は、スイッチング素子4に起因して特に高周波数帯にて抵抗回路のインピーダンス値が電気抵抗素子2の抵抗値からずれることを抑制するに適したインダクタンス値を有し、かかるインダクタンス素子5を備えることによって高周波数帯でも安定したインピーダンス値を有する抵抗回路を実現する。

(もっと読む)

レベルシフト回路、それを用いた電気光学装置、および、電子機器

【課題】 論理入力信号やノイズのレベルに適切に対応することが可能なレベルシフト回路を提供する。

【解決手段】 レベルシフト回路において、一端にて論理入力信号が入力される容量素子と、容量素子の他端に接続された入力に対して第1の論理反転レベルを有する第1の論理反転回路および第2の論理反転レベルを有する第2の論理反転回路を含み、第1と第2の論理反転回路の出力極性が一致することで第2の論理振幅を有する論理出力信号を反転する論理出力回路と、容量素子の他端に入力の一端と出力が接続され、前記第1の論理反転レベルよりも低く第2の論理反転レベルよりも高い第3の論理反転レベルを有する第3の論理反転回路と、第1および第2の論理反転回路と第2の論理振幅に対応する電源とを接続し、前記第1の論理反転レベルおよび前記第2の論理反転レベルを設定する論理反転レベル設定手段と、を備える。

(もっと読む)

レベル変換回路

【課題】 高速なレベル変換動作が可能で低消費電力、かつ汎用性の高いレベル変換回路を提供する。

【解決手段】 このレベル変換回路では、PチャネルMOSトランジスタ3,4は、カレントミラー回路を構成する。入力信号が「L」レベルから「H」レベルに立上げられた場合に、NチャネルMOSトランジスタ6が非導通になるため、PチャネルMOSトランジスタ3,4にリーク電流が流れるのが防止され、消費電力が小さくなる。また、入力信号が「L」レベルから「H」レベルに立上げられた場合に、PチャネルMOSトランジスタ5が導通することによって、ノードN2の電位が「H」レベルに固定されるため、ノードN2の電位が不安定な状態になるのが防止される。したがって、従来のレベル変換回路に比べて、高速なレベル変換動作が可能で低消費電力、かつ汎用性の高いレベル変換回路が実現できる。

(もっと読む)

半導体装置の送信器及びその信号送信方法

【課題】 半導体装置の送信器及びその信号送信方法を提供する。

【解決手段】 プリドライバステージ、メインドライバステージ及び制御回路を備える半導体装置の送信器である。プリドライバステージは、第1ドライバ制御信号及び第1終端制御信号に応答して、第1内部出力信号の共通モードレベル及び振幅を変更して第2内部出力信号を出力する。メインドライバステージは、第2ドライバ制御信号及び第2終端制御信号に応答して、第2内部出力信号の共通モードレベル及び振幅を変更して出力信号を出力する。制御回路は、出力信号に対応する入力信号の共通モードレベル及び振幅を検出して、第1ドライバ制御信号及び第2ドライバ制御信号と、第1終端制御信号及び第2終端制御信号とを発生させる。出力信号の共通モードレベル及び振幅は、入力信号の共通モードレベル及び振幅と同じである。半導体装置の送信器は、多様な共通モードレベル及び振幅を有する入力信号に対応する出力信号を出力できる。

(もっと読む)

ネットワークノード、ネットワークシステムおよびネットワークノードにおける終端抵抗設定方法

【課題】 ネットワーク、特にフリートポロジーネットワークにおけるノード間における通信の品質向上を実現する。

【解決手段】 終端抵抗設定方法は、ADコンバータが通信用ICから送信中フラグを受信すると(S100にてYES)、ADコンバータが通信用トランスの1次側の電圧値をAD変換して測定回路に出力するステップ(S200)と、測定回路が通信用ICから送信開始フラグを受信すると(S300にてYES)、測定回路がプリアンブルの電圧値の絶対値が基準電圧値±αの範囲内にあるか否かを判断するステップ(S400)と、プリアンブルの電圧値の絶対値が基準電圧値±αの範囲内にないと(S400にてNO)、測定回路がプリアンブルの電圧値が基準電圧値に近くなるように調整用終端抵抗の抵抗値を変更するステップ(S500)とを含む。

(もっと読む)

ディジタル処理コンポーネントの給電レベルを調節するシステム及びこれを動作させる方法

可変動作周波数をもつディジタル処理コンポーネント(100)の給電レベル、VDD、を調節するための制御回路(125)が開示される。制御回路(125)は、N個の遅延セル(201)と給電調節回路(210、215、220)とを包含する。N個の遅延セル(201)は直列に結合され、その各々はVDDの値により決定される遅延Dを持ち、その結果最初の遅延セル(201a)の入力に印加されたクロック縁はN個の遅延セル(201n)を通り順次リップルする。給電調節回路(210、215、220)はVDDを調節可能でまた(i)少なくともK遅延セル(201)及びK+1遅延セル(201)の出力をモニタし、(ii)クロック縁がK遅延セル(201)の出力に到達しそしてK+1遅延セル(201)の出力には到達していないことを決定し、(iii)それに応じVDDを調節可能な制御信号を発生する。  (もっと読む)

(もっと読む)

インターフェース回路

【課題】 LVDSインターフェース回路及びCMOSインターフェース回路を併用する。

【解決手段】 LVDS信号と、第1のCMOS信号のいずれか一方を選択する第1の選択回路21と、LVDS信号及びこの第2のCMOSのいずれか一方を選択する第2の選択回路22と、この第1の選択回路21の出力信号を夫々のゲートに供給する第1のPチャンネルMOSトランジスタ25P及び第1のNチャンネルMOSトランジスタ25Nと、この第2の選択回路22の出力信号を短絡スイッチ26a付きインバータ回路26を介して夫々、共通の定電流源28、30を有する25Pと25NからなるCMOSのゲート、及び27P27NからなるCMOSの2つCMOSのゲートを介して出力する。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】効率的な遅延回路を実現することができる汎用ロジックセル、それを用いた半導体装置、及びその半導体装置の製造方法を提供すること

【解決手段】半導体装置70Aは、複数の汎用ロジックセル60´と、それら複数の汎用ロジックセル60´に接続された電源線11と、それら複数の汎用ロジックセル60´に接続された接地線12と、第1配線81Aと、第2配線82Aとを備える。この時、第1配線81Aは、ある汎用ロジックセル60´の第3のノード3と、第4のノード4と、第5のノード5とを接続する。また、第2配線82Aは、電源線11と、その汎用ロジックセル60´の第1のノード1とを接続する。

(もっと読む)

81 - 100 / 102

[ Back to top ]