Fターム[5J056BB58]の内容

Fターム[5J056BB58]に分類される特許

21 - 40 / 102

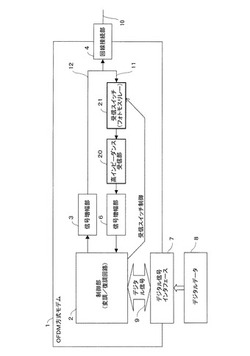

OFDM方式モデム

【課題】OFDM方式モデムにおいて、受信信号の最大値以上の電圧を発生する高電圧生成回路を設けることなく受信スイッチの動作の信頼性を確保できるようにする。

【解決手段】制御部2が変調および復調を行い回線接続部4を介して通信の回線10に接続されるOFDM方式モデムにおいて、受信通信路11に設けられ子機の受信インピーダンスを親機に対して子機を複数台接続したときの通信性能の低下を抑える高インピーダンスとする高インピーダンス受信部20、および受信通信路の開閉を行うフォトモスリレー21,211,212を備え、前記高インピーダンス受信部が前記フォトモスリレーの出力回路のMOS FETにながれる電流を許容電流以下とし、前記制御部が前記フォトモスリレーを開閉制御する。

(もっと読む)

多値記憶手段、多値バッファ手段および双方向性スイッチング手段

【課題】C・MOS・FET等の相補型3端子スイッチング手段を用いたオン・オフ駆動手段も使用できる双方向性スイッチング手段を提供する。

【解決手段】どちらも両主電極の役割がその印加電圧の方向により互いに入れ換わることができ、どちらも互いに相補関係に有る2つのオン・オフ制御スイッチング手段が有って、その両オン・オフ制御スイッチング手段のうち一方の主電極と他方の主電極を接続し、一方の開放された主電極と一方の制御電極の間に一方のオン・オフ駆動手段を設け、一方の開放された主電極と他方の制御電極の間に他方のオン・オフ駆動手段を設け、その両オン・オフ制御スイッチング手段の直列回路を双方向性のスイッチとして使用する。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

レベルシフタおよびそれを用いた試験装置

【課題】従来と異なる形式のレベルシフタを提供する。

【解決手段】レベルシフタ200は、第1下側電圧VssLと第1上側電圧VddLのいずれかのレベルをとる入力信号Inを、第2下側電圧VssHと第2上側電圧VddHのいずれかのレベルをとる出力信号Outにレベルシフトする。SRフリップフロップ100の出力信号Outは、そのセット端子への信号のポジティブエッジに応じて第2上側電圧VddHに遷移し、そのリセット端子への信号のポジティブエッジに応じて第2下側電圧VssHに遷移する。ANDゲート202は、SRフリップフロップ100の出力信号Qに対して反転論理レベルを有するフィードバック信号FBQと入力信号Inとの論理積を、SRフリップフロップ100のセット端子へと出力する。NORゲート204はフィードバック信号FBQと入力信号Inとの否定論理和を、SRフリップフロップ100のリセット端子へと出力する。

(もっと読む)

データ出力回路

【課題】プリエンファシスまたはディエンファシスのためのドライバの追加がなくても、プリエンファシスまたはディエンファシス動作を行えるデータ出力回路を提供すること。

【解決手段】インピーダンスコードによって各々オン・オフされ、出力ノードにデータを出力する複数の駆動手段311、312を備え、前記インピーダンスコードが、前記駆動手段をターンオンさせる値を有する第1のグループと前記駆動手段をオフさせる値を有する第2のグループとに分けられ、プリエンファシス期間の間には、前記第2のグループによる制御を受ける駆動手段の全部または一部がターンオンされる。

(もっと読む)

半導体装置

【課題】スイング領域を変換せずに、CML領域でスイングする信号の電源電圧レベルをシフトすることができる回路を提供する。

【解決手段】第1の電源電圧VDD1を電源として用い、第1のレベルを基準としてスイングするCMLクロックCML_TRANS_Pを受信して、そのスイング基準レベルを第2のレベルに切り換えて降圧CMLクロックCML_TRANS_Lとして出力するスイングレベル切換部220と、第2の電源電圧VDD2を電源として用い、スイングレベル切換部220から伝達される降圧CMLクロックCML_TRANS_LをバッファリングするCMLクロック伝達バッファリング部240と、第1の電源電圧VDD1を電源として用い、ソースクロックCML_INをバッファリングして、CMLクロックCML_TRANS_Pを生成した後、スイングレベル切換部220に提供するCMLクロック生成バッファリング部200とを備える。

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

電源インタフェース、受信回路、集積回路、及び信号伝送方法

【課題】異電源間であっても入力信号のライズとフォールの相対的な関係を維持したまま出力信号を生成できる電源インタフェースを提供する。

【解決手段】この電源インタフェースは、送信回路11と受信回路12を備える。受信回路12は、第1信号の第1信号レベルから第2信号レベルへの遷移を検出し、第1検出信号を出力する第1検出部18と、第1検出部18が第1信号の第1信号レベルから第2信号レベルへの遷移を検出するのに要する検出時間と同じ検出時間で、第2信号の第1信号レベルから第2信号レベルへの遷移を検出し、第2検出信号を出力する第2検出部19と、第1検出部18から出力された第1検出信号と第2検出部19から出力された第2検出信号に基づいて出力信号OUTを生成する出力信号生成回路20と、を有する。

(もっと読む)

半導体装置

【課題】マスクデータの変更をせずに複数のデフォルト値を設定する。

【解決手段】半導体装置80には、n個のデフォルト値設定回路が並列に配置される。n個のデフォルト値設定回路には、デフォルト値設定部2、デフォルト値設定部3、及びマルチプレクサMUX1がそれぞれ設けられる。デフォルト値設定部2は低電位側電源VSS電圧(ローレベル)を設定し、デフォルト値設定部3は高電位側電源VDD電圧(ハイレベル)を設定する。マルチプレクサMUX1は、デフォルト値設定部2及び3の値が入力され、モード選択信号Smsにより1ビットのデフォルト値を生成する。n個のデフォルト値設定回路はNビットのデフォルト値を生成する。

(もっと読む)

ターミネーション回路及びそれを備えるインピーダンス整合装置

【課題】回路面積を増加させることなく、多様なターミネーションインピーダンス値を提供するターミネーション回路及びこれを備えるインピーダンス整合装置を提供すること。

【解決手段】本発明に係るインピーダンス整合装置は、インピーダンス値を較正するためのインピーダンス調整コードを生成するキャリブレーション回路310と、インピーダンス値設定情報に応じて前記インピーダンス調整コードを変更し、変更された前記インピーダンス調整コードを出力するコード変更部320と、変更された前記インピーダンス調整コードに応じて決定されるインピーダンス値でインタフェースノードをターミネーションするターミネーションインピーダンス部330、340と、を備える。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

出力インタフェース回路

【課題】 外部機器の入力タイプに合わせてシンク型とソース型とに容易に切換えることができ、且つ製作コストを低減できる出力インタフェース回路を提供すること。

【解決手段】 出力インタフェース回路は、外部機器50に接続された端子A,Bと、端子Aに接続されたソース用レベル変換回路24と、端子Bに接続されたシンク用レベル変換回路25と、ディップSW8,9と、ソース用レベル変換回路24とシンク用レベル変換回路25を駆動する為のFET駆動回路21と、ディップSW8,9の設定信号に基づいてFET駆動回路21を制御する制御部3とを備え、ソース用レベル変換回路24は、PNP出力対応モードのとき制御部3の出力信号のレベルを高く変換して端子Aへ出力し、シンク用レベル変換回路25は、NPN出力対応モードのとき制御部3の出力信号のレベルを高く変換して端子Bへ出力する。

(もっと読む)

入力インタフェース回路

【課題】 外部機器の出力タイプに合わせてシンク型とソース型とに容易に切換えることができ、且つ製作コストを低減できる入力インタフェース回路を提供すること。

【解決手段】 入力インタフェース回路は、外部機器50に接続された端子A,Bと、ディップSW8,9と、端子Aに接続されたFET30を含むVCCバイパス回路22と端子Bに接続されたFET40を含むGNDバイパス回路23と、VCCバイパス回路22のFET30とGNDバイパス回路23のFET40を駆動する為のFET駆動回路21と、ディップSW8,9の設定信号に基づいてFET駆動回路21を制御する制御部3と、NPN入力対応モードのとき端子Aからの入力信号レベルを低く変換して制御部3へ出力するシンク用レベル変換回路24と、PNP入力対応モードのとき端子Bからの入力信号レベルを低く変換して制御部3へ出力するソース用レベル変換回路25とを設けた。

(もっと読む)

バッファ回路

【課題】低電圧と高電圧とを相反する論理信号として出力し、前記高電圧として、異なる2以上の電圧を出力可能であって、安定して動作するバッファ回路。

【解決手段】論理制御回路と、第1の高電圧VDDLを与える電源と出力端子との間に設けられ、ゲートに前記論理制御回路から出力された第1の高電圧VDDLレベルの制御信号が入力され、バックゲートに第1の高電圧VDDLが与えられた第1のMOSトランジスタM9と、第2の高電圧VDDHを与える電源と出力端子との間に設けられ、ゲートに論理制御回路から出力された第2の高電圧VDDHレベルの制御信号が入力され、バックゲートに第2の高電圧VDDLが与えられた第2のMOSトランジスタM11と、第1のMOSトランジスタM9と出力端子との間に設けられ、第2の高電圧VDDLレベルの制御信号によりオンオフが制御される第1のスイッチ回路SW1と、を備えるバッファ回路。

(もっと読む)

二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路

【課題】回路を構成する二重ゲート電界効果トランジスタの動作モードを、回路組み上げ後に適宜変更できるようにした二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路を提供する。

【解決手段】二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路は、二重ゲート電界効果トランジスタX1(21)の第1ゲートG1に第1の入力信号in1を加え、第2ゲートG2に選択回路11aを接続し、その選択回路11aに第1の入力信号in1と第2の入力信号in2を加え、選択回路11aにより第1の入力信号in1または第2の入力信号in2を選択して第2ゲートG2に加える。第2ゲートG2に切り替えて入力される入力信号に応じて、3端子動作又は4端子動作を行わせる。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、検出すべき電圧を入力する第4の端子と、参照電圧の電位差に応じた電流をそれぞれ流す第1、第2のトランジスタ(以下、Tr)と、第1のTrと直列接続される第3のTrと、第2のTrと直列接続される第4のTrと、第3のTrの流す電流に応じたミラー電流を流す第5のTrと、第4のTrの流す電流に応じたミラー電流を流す第6のTrと、第6のTrと第4の端子との間に接続される第7のTrと、第5のTrと第3の端子との間に接続され、第7のTrの流す電流に応じたミラー電流を流す第8のTrと、を有し、第5、第8のTrの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

ボンディングオプション回路、半導体集積回路装置

【課題】貫通電流の問題もなく、ボンディングオプションパッドのチップ上の配置の自由度を高めたボンディングオプション回路、半導体集積回路装置を提供する

【解決手段】ボンディングオプション回路15は、第1の電源電位を供給するためのリードフレーム上の第1のリードに接続され得る第1のボンディングオプションパッドと、第2の電源電位を供給するための前記リードフレーム上の第2のリードに接続され得る第2のボンディングオプションパッド51と、前記第1のボンディングオプションパッドに接続される第1の双方向IOバッファー60と、前記第2のボンディングオプションパッドに接続される第2の双方向IOバッファー61と、前記第1および第2の双方向IOバッファー60、61と接続される制御部20とを含む。

(もっと読む)

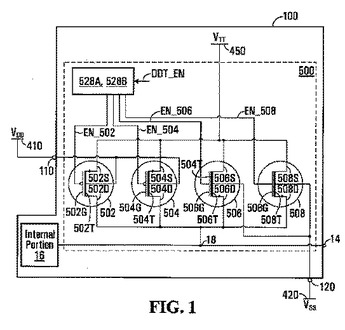

オンダイ終端のための終端回路

内部部分に接続されている端子を有する半導体デバイスにおいて、そのデバイスの端子用のオンダイ終端を提供するための終端回路。この終端回路は、端子と電源の間に接続された、少なくとも1つのNMOSトランジスタおよび少なくとも1つのPMOSトランジスタを含む複数のトランジスタと、NMOSトランジスタのそれぞれのゲートを対応するNMOSゲート電圧でドライブし、PMOSトランジスタのそれぞれのゲートを対応するPMOSゲート電圧でドライブするための制御回路であって、オンダイ終端が有効である場合にトランジスタを動作のオーム領域におくようにNMOSゲート電圧およびPMOSゲート電圧を制御するように構成されている、制御回路とを含む。電源は、上記NMOSゲート電圧のそれぞれより小さく、上記PMOSゲート電圧のそれぞれより大きい電圧を供給する。  (もっと読む)

(もっと読む)

通信装置及びそれを内蔵する電池パック

【課題】双方向通信において信号が双方から入力されても一方から他方に信号を誤作動無く伝送できるようにし、信号の送受の切り替えタイミングを任意に変更できるようにする。

【解決手段】第1の入力信号がJ入力に入力され且つ第1の入力信号の反転信号がK入力に入力されて第1の出力信号を出力する第1のJK型フリップフロップ(FF)と、第2の入力信号がJ入力に入力され且つ第2の入力信号の反転信号がK入力に入力されて第2の出力信号を出力する第2のJK型FFとを備え、NANDゲート12に入力されるクロックが第2のJK型FFのQ出力の反転信号に置換され、NANDゲート13に入力されるクロックが第2の入力信号の反転信号に置換され、NANDゲート22に入力されるクロックが第1のJK型FFのQ出力の反転信号に置換され、NANDゲート23に入力されるクロックが第1の入力信号の反転信号に置換されている、通信装置。

(もっと読む)

差動出力バッファ

【課題】 広範囲な電源電圧仕様に対して、安定した出力振幅およびその出力振幅の中心電圧を出力することができる差動出力バッファを提供する。

【解決手段】 ドレインが電源電圧VDDに接続されるとともにゲートに出力差動信号OUTP,OUTNの出力コモンモード(VOC)を規定する第1の基準信号VREF1が入力されるデプレッション型NMOSトランジスタ11と、ソース双方がデプレッション型NMOSトランジスタ11のソースに接続されるとともに各ゲートに各差動信号INN,INPが入力されるPMOSトランジスタ12,14と、各ゲートおよび各ドレインが各PMOSトランジスタ12,14の各ゲートおよび各ドレインにそれぞれ接続されるとともに各ゲートに各差動信号INN,INPが入力されるNMOSトランジスタ13,15と、NMOSトランジスタ13,15双方のドレインとグランドGNDとの間に接続されたNMOSトランジスタ16とを備えた。

(もっと読む)

21 - 40 / 102

[ Back to top ]