Fターム[5J056CC02]の内容

Fターム[5J056CC02]に分類される特許

1 - 20 / 296

信号送信回路

複数の集積回路にインタフェース信号を供給する方法および回路

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

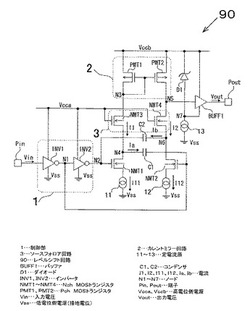

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

LVDS出力回路

【課題】 1個の基準電圧源を用いて、中間電圧(コモン電圧)及び出力振幅について温度特性がフラットになり、搭載されるICチップの面積増大を防ぐことが出来るLVDS出力回路を提供する。

【解決手段】 中間電圧(コモン電圧)作成用の基準電圧はバンドギャップリファレンス回路1の演算増幅器5の出力部から引き出し、振幅を決める定電流回路の基準電圧はバンドギャップ電圧を作る際に使用する抵抗R41、R42の節点14(中間タップ)から引き出す。そして、引き出し部分は電流検出用抵抗R6の温度特性に合わせる。検出用抵抗の温度特性と中間タップの位置での温度特性を合わせることにより、定電流回路3全体としての温度変化を無くすようにする。このようにして、1つのバンドギャップリファレンス回路1を用いて温度変化無しにLVDS出力回路を駆動できる。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

出力回路

【課題】差動出力電圧の振幅のばらつきを抑制した出力回路を提供する。

【解決手段】出力回路は,定電圧ノードと基準電源との間に,複数のスイッチ素子のオン,オフにより合成抵抗値が可変制御可能な複数の抵抗を有し,定電圧ノードに第1の電流を生成する定電流生成回路と,第1の電流をカレントミラーにより生成した第2の電流を,内部回路から供給される内部差動信号に応じて,出力端子対に出力する出力駆動回路と,出力端子対の出力差動電圧の差が所望の電圧差と一致するように,定電流生成回路の複数のスイッチ素子を制御するスイッチ素子制御信号を生成する出力振幅調整部とを有する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

差動入力回路および差動入力回路の電圧特性調整方法

【課題】ソースが共通接続されそれぞれのゲートが二つの入力端子に接続さた二つのトランジスタを有する差動対を備える差動入力回路において、より適正に入力オフセットをより小さくする。

【解決手段】トランジスタTin1,トランジスタTin2のドレインに高電圧印加回路60を接続し、トランジスタTin1のソースおよびトランジスタTin2のソースと接地電圧印加点GNDとの間にトランジスタTsenを設け、論理ローレベルの電圧の制御信号SENをスイッチング回路70に入力すると共に制御信号Tcとしてクロック信号を入力して入力端子IN1に電圧V1を印加すると共に入力端子IN2に電圧V2を印加し、検出した出力端子OUT,OUTBの電圧に応じてトランジスタTin1,Tin2のドレインに高電圧印加回路60により電源電圧Vddhを印加する

(もっと読む)

レベル変換回路

【課題】Lレベル出力も高電位側電源から決定されるようにできるレベル変換回路を提供する。

【解決手段】高電位電源VDDから論理レベル設定抵抗RLを経由して出力ノードBに至る第1経路と、高電位電源VDDから論理レベル設定抵抗RLを経由しないで出力ノードBに至る第2経路と、を設ける。切換えスイッチ部120,110は、Lレベル出力の場合には第1経路を導通させ、Hレベル出力の場合には第2経路を導通させる。さらに、Lレベル出力の場合には、カレントミラー回路130を有する定電流源がONになり、出力ノードBから一定電流を引き抜く。前記出力ノードBは、終端抵抗RLを介して終端電圧VTに接続されている。Lレベル出力の電位VOUTは、終端電圧VTの値ではなく、論理レベル設定抵抗RLの値によって調整される。

(もっと読む)

レベル生成回路

【課題】 耐圧の低いMOSFETを保護するためにゲート接地として動作する、MOSFETのゲート電圧を生成するための外部電源を不要にする。

【解決手段】 第1電源電圧から一定の大きさの第1電流を生成する定電流生成部と、第1薄膜NMOSFETと第2薄膜NMOSFETから構成され、第1電流に比例した大きさの第2電流を出力する第1カレントミラー回路部と、第2薄膜NMOSFETを保護するためにゲート接地として用いる第3薄膜NMOSFET及び第1厚膜PMOSFETと、第1電源への電流の逆流を防ぐための第1ダイオードと、第3薄膜NMOSFETのゲート−ソース間電圧がマイナスになることを防ぐための第2ダイオードとからなる保護回路部と、第2電流に比例した大きさの第3電流を出力する第2カレントミラー回路部と、第3電流により第1定電圧を生成する第1ツェナーダイオード部とを備える。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

レベル変換バススイッチ

【課題】レベル変換時の信号の立ち上がりを速くすることのできるレベル変換バススイッチを提供する。

【解決手段】実施形態のレベル変換バススイッチは、低電圧レベル信号が伝送される低電圧レベル信号線と高電圧レベル信号が伝送される高電圧レベル信号線との間に、低電圧レベルの制御信号により導通が制御されるMOSトランジスタ型のスイッチ1が接続され、高電圧レベル信号線と高電圧電源線VccBとの間に、プルアップ抵抗2が接続される。このレベル変換バススイッチでは、加速回路3が、高電圧レベル信号の立ち上がりをプルアップ抵抗2による立ち上がりよりも速くし、加速期間制御回路4が、加速回路3の作動期間を制御する。

(もっと読む)

1 - 20 / 296

[ Back to top ]