Fターム[5J056CC07]の内容

Fターム[5J056CC07]に分類される特許

1 - 20 / 27

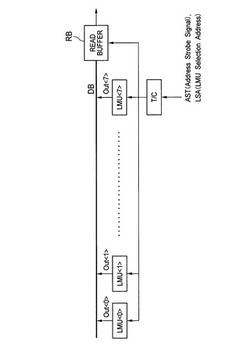

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

検出回路

【課題】プロセスミスマッチ等によるサンプルごとの検出電圧レベルのばらつきを低減させることができ、高速動作を行うことが可能な検出回路を提供する。

【解決手段】1対のシリアルデータ信号の一方が反転入力端に入力され、他方が非反転入力端に入力される第1検出用レシーバ回路と、1対のシリアルデータ信号の一方が非反転入力端に入力され、他方が反転入力端に入力される第2検出用レシーバ回路と、第1検出用レシーバ回路及び第2検出用レシーバ回路の各出力信号に基づいて、入力検出及び切断検出の少なくとも一方を行う検出回路とを備え、第1検出用レシーバ回路及び第2検出用レシーバ回路は、それぞれ第1差動入力回路及び第1負荷回路を含む差動増幅回路と、差動増幅回路の閾値に設ける第1オフセット制御回路とを有し、第1負荷回路はドレインが独立でゲートを共通とし、ゲートに所定の電圧が印加される1対のMOSトランジスタを含んで構成される。

(もっと読む)

半導体集積回路

【課題】常時電源オン回路領域の電源が先に遮断されても電源オフ回路領域に悪影響を及ぼすことを防止する半導体集積回路を提供する。

【解決手段】第1電源から電力供給される回路領域である電源オンドメインと、第2電源から電力供給される回路領域である電源オフドメインとを同一チップ上に備え、電源オンドメインは、第1電源がオンかつ第2電源がオフであるときに電源オフドメインと電源オンドメインとの間で入出力される信号を遮断する第1信号遮断部と、第2信号遮断部の遮断を有効または無効にする旨を示す第1制御信号を出力する遮断制御部とを備え、電源オフドメインは、遮断制御部からの遮断を有効にする旨を示す第1制御信号に基づき、電源オンドメインと電源オフドメインとの間で入力される信号を遮断する第2信号遮断部を備え、前記遮断制御部は、第1電源からの電源供給の停止を検出したとき、遮断を有効にする旨を示す第1制御信号を出力する。

(もっと読む)

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

電流回路および信号発生回路

【課題】吸い込みの電流値と吐き出しの電流値とを揃える。

【解決手段】第1〜第3単位回路の各々は、第1のPチャネルトランジスタ(P11,P21,P31)、第2のPチャネルトランジスタ(P12,P22,P32)、第1のNチャネルトランジスタ(N11,N21,N31)、および第2のNチャネルトランジスタ(N12,N22,N32)を備える。各トランジスタの特性は等しく、各単位回路における第1のNチャネルトランジスタのゲートは第1固定電位Vs1に接続され、第2のPチャネルトランジスタのゲートは第2固定電位Vs2に接続される。第1ノードND1と第2ノードND2とは第3配線190に接続される。P11およびN12は、常にオン状態となるように設定され、P21およびN22は、常にオフ状態となるように設定され、P32とN31との接続点は外部の負荷に接続される出力端子S1と接続され、P31とN32とは一方がオン状態のとき他方がオフ状態となるように制御される。

(もっと読む)

スイッチング出力回路およびスイッチング電源

【課題】貫通電流を防止する。

【解決手段】ハイサイドトランジスタ16およびローサイドトランジスタ18それぞれのゲート電極30、40は、異なる位置に設けられた駆動用コンタクト32(42)と検出用コンタクト34(44)を介して信号を入出力可能に構成される。ハイサイドドライバ22は、制御信号S1が第1レベルであり、かつローサイドトランジスタ18側の検出用コンタクト44の信号SLがローレベルのとき、ハイサイドトランジスタ16側の駆動用コンタクト32にローレベルを印加する。ローサイドドライバ24は、制御信号S1が第2レベルであり、かつハイサイドトランジスタ16側の検出用コンタクト34の信号SHがハイレベルのとき、ローサイドトランジスタ18側の駆動用コンタクト32にハイレベルを印加する。

(もっと読む)

信号レベル変換回路および位相同期回路

【課題】信号レベル変換回路の上限動作周波数を向上させる。

【解決手段】クロック信号をゲート(G)電極に受ける第1MOSトランジスタ(MOS−Tr)と,ドレイン(D)電極を第1MOS−TrのD電極に接続される第2MOS−Trと,逆相のクロック信号をG電極に受ける第3MOS−Trと,G電極およびD電極を第2MOS−TrのG電極と第3MOS−TrのD電極に接続された第4MOS−Trと,第1および第2MOS−TrのD電極から取り出した信号を受けるインバータ回路により構成されたレベル変換回路において,第2MOS−Trのソース電極と電源の間,または,第4MOS−Trのソース電極と電源の間の少なくとも一方に,並列に接続した複数の第5MOS−Trを設け,インバータ回路の出力の平均電圧が低電位側の電源と高電位側の電源の中間の電圧になるように第5MOS−Trの導通及び遮断を制御する制御回路を設ける。

(もっと読む)

伝送回路、CMOS半導体デバイス、及び設計方法

【課題】クロック信号の遅延量を低減する。

【解決手段】予め定められた最小パルス時間以上のパルス時間を有する差動信号を伝送する伝送回路であって、2本の伝送線の電位差として、差動信号を送出する駆動部102aと、2本の伝送線の電位差により差動信号を受け取ることにより、差動信号に基づいて動作する被駆動部102bと、2本の伝送線を電気的に接続する接続抵抗104とを備える。また、接続MOSトランジスタは、被駆動部の受信端の近傍に設けられてよい。

(もっと読む)

信号調節受信器回路網

【課題】通信経路から受信されるデジタル信号を調節するための技術を提供すること。

【解決手段】通信経路から受信される信号を調節するためのシステムおよび方法が開示される。受信器は、信号の周波数成分の少なくとも一部を減衰する通信経路から信号を受信できる。受信器は、受信される信号の周波数コンテンツの少なくとも一部を調節する等化ブロック、正規化された信号振幅および/または正規化されたエッジスロープを提供する信号正規化ブロック、および制御ブロックを含み得る。一実施形態においては、制御ブロックは、高周波数に対する等化ブロックにおける周波数調節を制御するが、低周波数に対しては制御しない。低周波数調節に対して、制御ブロックは、信号正規化ブロック内の正規化された信号振幅を制御する。このようにして、低周波数コンテンツに対する制御された調節は、信号正規化ブロックにおいて実行される。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

抵抗調整回路及び半導体集積回路

【課題】本発明は、LSI内部の抵抗値を外部の抵抗素子に基づいて規定範囲内に自動調整することを特徴とする。

【解決手段】半導体集積回路に接続された抵抗素子Rextの抵抗値に応じた値の基準電圧Vrefを発生する基準電圧発生回路10と、制御コード信号Code_OUT[N:0]に応じて抵抗値が調整されるレプリカ抵抗回路12を有し、このレプリカ抵抗回路の抵抗値に応じた値の比較用電圧Vaを発生する比較用電圧発生回路12と、レプリカ抵抗回路と同様に構成され、制御コード信号に応じて抵抗値が調整される本体抵抗回路14と、基準電圧及び比較用電圧をそれぞれの電圧値に応じた周波数を有する信号に変換し、さらに両信号を積分して積分データを生成し、かつ両積分データの差に基づいて前記制御信号を発生する抵抗制御回路11とを半導体集積回路に内蔵したことを特徴とする。

(もっと読む)

差動信号生成回路

【課題】差動信号のクロスポイントを容易に調整することができる差動信号生成回路を得る。

【解決手段】本発明に係る差動信号生成回路は、入力信号と閾値電圧とを比較して差動信号を出力する第1アンプと、差動信号に応じて閾値電圧を調整する第2アンプとを備え、第2アンプは、ゲートに差動信号がそれぞれ入力され、差動対を構成する第1,第2トランジスタと、第1、第2トランジスタのドレインと基準電位点との間にそれぞれ接続されたカレントミラー構成の第3、第4トランジスタと、第1,第2トランジスタのソースが共通接続された電流源と、外部から入力された電流又は電圧に応じて、第1トランジスタのドレイン電流を調整する調整部とを有し、第2トランジスタのドレイン電圧に応じて閾値電圧を調整する。

(もっと読む)

定電荷出力回路

【課題】1個のクロック信号入力に対して所定の正確な量の電荷を出力させるようにして、出力電荷量がクロックジッタの影響を受けないようにする。

【解決手段】トランジスタM1,M2でカレントミラー回路を構成し、スイッチSW1をOFFしスイッチSW2をONした状態から、スイッチSW2をOFFした後にスイッチSW1をONにし、キャパシタC1に充電される電荷に応じた電荷をトランジスタM2から出力させる。スイッチSW1がONしスイッチSW2がOFFしている期間が、キャパシタC1の両端の電圧がVDDとGND間の電位差からトランジスタM1の閾値電圧を差し引いた電圧に充電されるまでの時間よりも長くなるよう制御する。

(もっと読む)

半導体集積回路の設計方法

【課題】算出すべき論理回路のゲートレベルの特性に応じた実効容量や実効抵抗を用いて、実際の特性との差異を小さくする。

【解決手段】半導体集積回路の設計段階のゲートレベル特性算出では、遅延実効容量Cdelay、遷移実効容量Cslew、及び実効抵抗Cjkがライブラリー1に予め格納されている。半導体集積回路の設計段階のレイアウト後、論理ゲート回路の遅延計算がInput Slewデータと遅延実効容量Cdelayにもとづいて実行され、論理ゲート回路の遷移計算がInput Slewデータと遷移実効容量Cslewにもとづいて実行され、論理ゲート回路の消費電流計算がInput Slewデータと消費電流実効容量Cpowerにもとづいて実行される。

(もっと読む)

差動伝送回路および信号再生方法

【課題】相手側の装置と正常に接続されていない状態での不定信号の入力による誤動作を防止することのできる差動伝送回路および信号再生方法を得る。

【解決手段】差動レシーバ13の出力14は内部ロジック回路15に供給されると共に、バンドリジェクションフィルタ21に入力されて、ここで相手側の装置と正常に接続されていない状態で発生するノイズのみの波長成分を透過させる。したがって、不定信号の入力により、セット・リセット・フリップフロップ21がセットされてマスク期間設定回路25で定めた時間だけマスク信号16が発生し、出力14が内部ロジック回路15内でマスクされる。これにより、後段の回路の誤動作が防止される。

(もっと読む)

半導体集積回路装置

【課題】製品歩留りの改善と信頼性を確保しつつ高速化を実現した半導体集積回路装置を提供する。

【解決手段】 MOSFETで構成される主回路と、上記MOSFETが形成される半導体領域に対して正のバイアス電圧を供給する基板バイアス回路とを有する半導体集積回路装置において、上記MOSFETが形成される半導体領域とソースとの間に流れる基板電流に応答して上記半導体領域に供給される電流を制限する電流制限回路を設ける。

(もっと読む)

1 - 20 / 27

[ Back to top ]