Fターム[5J056CC13]の内容

Fターム[5J056CC13]に分類される特許

1 - 17 / 17

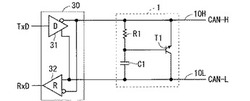

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】トランシーバ回路30等の通信回路に接続される通信線10を構成するHライン通信線10H,Lライン通信線10L間にリンギング抑制回路1が設けられる。リンギング抑制回路1において、バイポーラトランジスタT1のエミッタはHライン通信線10Hに接続され、コレクタはLライン通信線10Lに接続され、ベースはコンデンサC1の一方電極及び抵抗R1の一端に接続され、コンデンサC1の他方電極はLライン通信線10Lに接続され、抵抗R1の他端はHライン通信線10Hに接続される。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

低電流の論理およびドライバ回路

低電流回路は、論理ステージ(E3,E4,E5)と、インバータステージ(E8)と、ドライバステージ(E9,E10)とを備える。論理ステージおよびインバータステージには電流リミッタが設けられ、電流リミッタは、Dモードフィードバックトランジスタ(D1;D2)および電圧降下を生成する要素(E1,E2;E6,E7)を備える。フィードバックループ(FL)は、Dモードフィードバックトランジスタのソースおよびゲートを、この要素を介して接続する。ドライバステージは、トーテムポール状に接続されたEモードトランジスタ(E9,E10)を備え、それは、負荷回路を接続および非接続とするように、DモードトランジスタおよびEモードトランジスタを駆動する。この回路は、オン状態において大電流能力を提供するとともに、オフ状態において無視できるほどの電流を有する。  (もっと読む)

(もっと読む)

カップリング回路、このカップリング回路を含むドライバ回路、およびこのカップリング回路の制御方法

【解決手段】p−チャネル電界効果トランジスタタイプの第1および第2のトランジスタ(P1,P2)を備えるカップリング回路において、第1のトランジスタ(P1)のドレイン端子は信号入力端子(1)に接続し、第1および第2のトランジスタ(P1,P2)のソース端子はともに信号出力端子(2)に接続し、第1および第2のトランジスタ(P1,P2)のバルク端子はともに第2のトランジスタ(P2)のドレイン端子に接続し、第1のトランジスタ(P1)のゲート端子は第2のトランジスタ(P2)のゲート端子に接続する。このカップリング回路には、さらに 負電圧を生成する電荷ポンプ回路(110)を含むゲート制御回路(10)も設ける。このゲート制御回路(10)は、負電圧に基づいて、第1および第2のトランジスタ(P1,P2)のゲート端子におけるゲート電圧を制御する。 (もっと読む)

集積回路装置、及び電子機器

【課題】 グランド端子がオープン状態となった場合であっても、グランド端子以外の端子の電位に応じて、内部回路の動作/非動作が決定されてしまうような不都合が生じないようにする。

【解決手段】 集積回路装置は、内部回路200と、グランド端子TGと、内部回路が動作している期間の少なくとも一部の期間においてグランドレベルとなる第1信号SG1が供給される第1端子T1と、第1端子T1の電圧と、グランド端子TGの電圧とを比較することによって、グランド端子TGのオープン状態を検出する検出回路20と、検出回路20によってグランド端子TGのオープン状態が検出されると、内部回路200をリセットまたはディスエーブル状態に設定する設定回路30と、を含む。

(もっと読む)

ドライバ回路およびDC−DCコンバータ

【課題】デッドタイムを設けることなく貫通電流を抑制することができるとともに、貫通電流を抑制しつつ高周波化を図ることができるドライバ回路およびDC/DCコンバータを提供する。

【解決手段】電源端子と接地端子との間に直列形態に接続され、デッドタイムのない相補的な一対の制御信号によってオン、オフ駆動される第1のスイッチング素子(SW1)と第2のスイッチング素子(SW2)を備えるドライバ回路において、少なくとも前記第1のスイッチング素子の制御端子に、オン状態での制御電圧を制限するリミッタ回路(LMT1)を接続するようにした。

(もっと読む)

周波数出力装置、流量計、及び流量計測装置

【課題】周波数出力端子の保護と、信号波形の帯域を十分に確保することができる周波数出力装置を提供する。

【解決手段】周波数信号を出力する周波数出力装置2の出力端子にバリスタ素子Zs1を設ける。これにより、例えばバリスタ電圧を超える電圧が出力端子に印加された場合に、そのバリスタ電圧を超える電圧分を接地側に流して、周波数出力装置2に高電圧のサージ電圧が入力されるのを防ぎ、周波数出力装置2を保護する。また、放電時における放電量を少なくして電圧の変化を滑らかにし、電圧の立ち下がり時におけるピーク電流を下げて、ラジオノイズ等の電磁誘導ノイズの影響を低減し、必要な周波数信号の帯域を確保する。

(もっと読む)

インターフェイス回路およびそれを備える表示装置

【課題】波形整形回路の周波数特性の測定を可能にする。

【解決手段】波形整形回路11は、入力差動信号INN,INPを波形整形する。出力切換回路12は、通常モードのときには、波形整形回路11からの整形差動信号SP,SNを2値化して出力する。一方、出力切換回路12は、テストモードのときには、波形整形回路11からの整形差動信号SN,SPを正弦波信号として出力する。

(もっと読む)

半導体装置

【課題】製造プロセスの微細化と、しきい電圧の低下により、通常オフ状態となっているMOSトランジスタにリーク電流が発生する。また、製造プロセスによっては、NチャンネルMOSトランジスタとPチャンネルトランジスタとのリーク電流が等しいとは限らない場合があり、発振回路のような回路構成によっては、動作に問題を引き起こす可能性が高い。

【解決手段】本発明にかかる半導体装置は、制御電圧により駆動力が変化する第1のトランジスタを有する保護回路と、前記保護回路と同一の回路構成を有するモニター回路と、前記モニター回路が出力する電圧と、基準電圧との比較結果に基づいて前記制御電圧を生成する制御電圧生成回路とを有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、製造工数、製造コストの増加を伴うことなく、高電圧印加端子を設ける。

【解決手段】高耐圧のNMOS(T4)からなるトランスファゲート54と、プルアップ抵抗55を設ける。トランスファゲート54の入力端は高電圧印加端子50に接続され、トランスファゲート54の出力端は入力抵抗51を介して、CMOSインバータ52に接続されている。プルアップ抵抗55の一方の端はトランスファゲート54の出力端に接続され、プルアップ抵抗55の他方の端には電源電圧VDD(5V)が印加されている。トランスファゲート54は、入力された高電圧VX(VX>VDD)をVDD−Vt1’まで降下させる。プルアップ抵抗55は、トランスファゲート54の出力端の電圧をVDDにバイアスしており、トランスファゲート54によって降下された出力端の電圧を略VDDまで上昇させる。

(もっと読む)

スイッチング動作速度を増加させるブースト回路を含む高電圧スイッチ回路およびこれを含むフラッシュメモリ装置

【課題】フラッシュメモリ装置において、スイッチング動作速度を向上させるとともに、出力される高電圧のノイズ成分を減少させる。

【解決手段】イネーブル信号に応答して出力ノードを設定された電圧にプリチャージするイネーブル制御回路と、出力ノードがプリチャージされるとき出力ノードで発生するスイッチ制御電圧に応答して入力ノードにフィードバック電圧を供給するフィードバック回路と、クロック信号に応答してフィードバック電圧をブーストしブースト電圧を出力ノードに出力することによりスイッチ制御電圧を増加させるブースト回路と、スイッチ制御電圧に応答してオンまたはオフされオンされるときに高電圧を受信して出力する高電圧スイッチとを備えて、高電圧スイッチ回路を構成する。ブースト回路は、クロスカップルドタイプの増幅回路を含む。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

半導体集積回路およびそのテスト方法

【課題】出力バッファを含む半導体集積回路のテストにおける、不要な不良品判定を減らし、歩留の改善を図る。

【解決手段】LSI20内に、LSIテスタ30による、出力バッファのテストを補助するための構成(スイッチ切換手段10,特性記憶メモリ11,補正電圧算出手段12,リミッタ13)を設ける。まず、各出力段トランジスタ(M1,M2)の電圧/電流特性を実測し、特性記憶メモリ11に記憶されている特性と比較し、同一性を調べる。同一性が肯定されない場合には、補正電圧算出手段12が、両特性の差異に基づき、LSI20の規格に抵触しない範囲内で、最適な入力電圧レベルを算出し、これに基づき、再検査を行い、運悪く不良品と判定されていたものを救済する。

(もっと読む)

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

静電気保護機能を有するバッファ回路

本発明は、静電気保護機能を有するバッファ回路を提供する。本発明のバッファ回路は、それぞれ選択的に入出力パッドの電圧をプルアップ及びプルダウンするプルアップ回路とプルダウン回路を含み、プルアップ回路及びプルダウン回路は分離した電源供給ラインに連結されて、静電気放電を入出力パッドから受けたとき、入出力パッドからプルアップ回路を経てプルダウン回路への電流パスが存在しない。これにより、静電放電特性を向上させることができる。  (もっと読む)

(もっと読む)

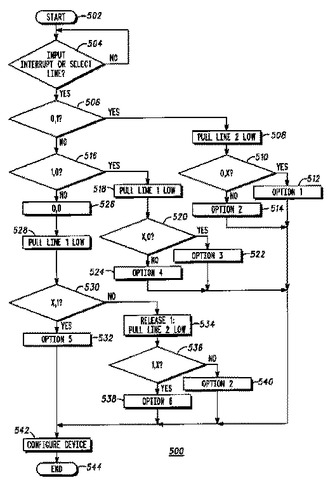

携帯機器のための割り込み駆動の拡張型オプション選択インタフェース

携帯電子機器(102)には周辺コンポーネント(104)が取り付けられ、この周辺コンポーネント(104)はオプション選択回路を使用して周辺コンポーネントのオプションクラスを示す。オプション選択回路は、携帯電子機器に割り込みを生成し、次いで種々のオプション論理ラインの論理レベルの変更により、オプションクラスを決定する。オプション選択ラインのうちの一つの論理状態の反転が検知されると、携帯電子機器はオプション選択回路のプレゼンスを知り、従って周辺コンポーネントのオプションクラスを決定する。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]