Fターム[5J056DD29]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723) | 相補動作するもの、CMOS (940)

Fターム[5J056DD29]に分類される特許

921 - 940 / 940

半導体装置

【課題】複数の異なる電源や端子の追加を必要とせず、低消費電流で占有面積の小さなレベルシフト回路を有する半導体装置を提供する。

【解決手段】入力信号およびその反転信号を受けるNチャネルMOSトランジスタM1およびM2、たすきがけ接続されたPチャネルMOSトランジスタM3およびM4、入力信号Lの反転信号Hを与えるPチャネルMOSトランジスタM5によりレベルシフト回路を構成する。入力信号Lの反転信号Hを与えるPチャネルMOSトランジスタM5を導入したことにより、複数の異なる電源や端子の追加を必要とせず、低消費電流で占有面積が小さく、高速動作可能なベルシフト回路を有する半導体装置を提供する。

(もっと読む)

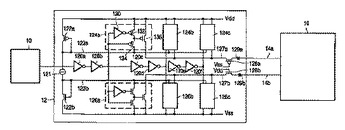

高性能リピータモードおよび通常リピータモードを有するリピータ回路

高性能リピータモードおよび通常リピータモードを有し、該高性能リピータモードが高速リセット機能を有するリピータ回路が提供され説明される。一実施形態では、スイッチが第1のスイッチ位置に設定され、リピータ回路を高性能リピータモードで動作させる。別の実施形態では、スイッチは第2のスイッチ位置に設定され、リピータ回路を通常リピータモードで動作させる。  (もっと読む)

(もっと読む)

ワイヤ遷移を検出し支援する回路および方法

ワイヤ上の信号遷移を支援する回路及びその方法。前記回路は、第1のサブ回路を含み、前記第1サブ回路は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間、ターンオンさせ、そしてターンオフする。前記第1のトランジスタ(16)は、出力(34)を高状態に駆動して、該立ち上がり遷移を支援する。前記回路は、第2のサブ回路を含み、前記第2のサブ回路は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間、ターンオンさせ、そしてターンオフする。前記第2のトランジスタ(25)は、出力(34)を低状態に駆動して、該立ち下がり遷移を支援する。 (もっと読む)

高性能リピータモードおよび通常リピータモード並びにリセット機能を有するリピータ回路

高性能リピータモードおよび通常リピータモードを有し、該高性能リピータモードが高速リセット機能を有するリピータ回路が提供され説明される。一実施形態では、スイッチが第1のスイッチ位置に設定され、リピータ回路を高性能リピータモードで動作させる。別の実施形態では、スイッチは第2のスイッチ位置に設定され、リピータ回路を通常リピータモードで動作させる。  (もっと読む)

(もっと読む)

出力段システム

開示されたのは、いくつかのトランジスタ(P1、P2)が集積回路中に直列に配置され、個々の電力制御された電圧源(Q1、Q2)によって始動される出力段システムである。これにより出力(A)でトランジスタ(P1、P2)の定格電圧よりも高い電圧を供給することを可能にしながら、トランジスタを異なる絶対ポテンシャルで動作することを可能にする。開示された出力段システムは完全に集積回路技術に従って製造が可能であり、それぞれ高い電圧範囲でディジタル及びアナログ信号出力を供給するのに適している。  (もっと読む)

(もっと読む)

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

論理基本セル、論理基本セルアレイ、および、論理回路

論理基本セルは、あらかじめ決定できる第1のまたは第2の論理サブ関数に関して第1入力信号と第2入力信号とを論理的に組み合わせるための、第1論理関数ブロックおよび第2論理関数ブロックを備えている。また、上記論理基本セルは、上記第1論理関数ブロックに結合されてゲート端子とソース/ドレイン端子とを有する第1論理トランジスタを備えている。該ゲート端子には第3入力信号が供給されうる。該ソース/ドレイン端子には、出力信号が供給されうる。さらに、第2論理関数ブロックに結合されて、ゲート端子とソース/ドレイン端子とを有する第2論理トランジスタが備えられている。該ゲート端子には、第3入力信号に対して相補的な信号が供給されうる。該ソース/ドレイン端子は、第1論理トランジスタのソース/ドレイン端子に結合されている。  (もっと読む)

(もっと読む)

SOI構造シングルイベント耐性のインバータ、NAND素子、NOR素子、半導体メモリ素子、及びデータラッチ回路

高いシングルイベント耐性を有するインバータ、NAND素子、NOR素子、メモリ素子、データラッチ回路を提供する。シングルイベント耐性インバータ(3I)は、インバータを構成するpチャネルMOSトランジスタ及びnチャネルMOSトランジスタのそれぞれに対して同じ導電型のトランジスタをさらに直列に接続した二重化構造(3P1,3P2,3N1,3N2)にし、2つのpチャネルMOSトランジスタの間のノード(A)と、2つのnチャネルMOSトランジスタの間のノード(B)とを接続線で接続する。シングルイベント耐性のメモリ素子及びデータラッチ回路(4)は、当該シングルイベント耐性インバータ(3I)を含む。 (もっと読む)

インバータ回路とこれを用いた圧電発振器

【課題】CMOSインバータの貫通電流は、このインバータを用いた装置の電力消費量を増大させ、特に携帯機器においては電池の寿命を短くする。

【解決手段】従来のCMOSインバータと同じ回路のP-MOSTQ1のソースS回路に、別のP-MOSTQ3を直列に追加接続し、そのゲートと回路の入力端間を遅延回路Z1で接続し、また、前記CMOSインバータのN-MOSTQ2のソース回路に、別のN-MOSTQ4を直列に追加接続してそのゲートと回路の入力端間を遅延回路Z2で接続した回路構成にする。

(もっと読む)

半導体装置及び電圧制御発振回路

電圧制御発振回路(15)内に互いに異なる段数の独立した複数のリング発振回路を設け、セレクタ(22)により何れか1つのリング発振回路の出力を帰還クロック信号(FB)として選択的に出力することで、独立しているリング発振回路の出力が常に帰還クロック信号として出力されるようにして、動作速度が高速であってもデューティ比が崩れていない帰還クロック信号を出力でき、入力信号(DLLI)が出力されるまでの遅延時間を任意に調整できるようにする。  (もっと読む)

(もっと読む)

信号伝送システム及び信号伝送線路

【課題】 グランドを参照する差動線路とグランドを参照しない差動線路を接続して、数十GHz帯のデジタル高速信号を差動線路を介して伝送する。

【解決手段】信号伝送線路を介して回路ブロック間でデジタル信号の伝送を行う信号伝送システムにおいて、各回路ブロックはそれぞれ機能回路と分離された構成の受送信回路を備え、受信端と送信端の間がインピーダンス整合した伝送線路115であることを基本構成とし、差動出力ドライバから導出されたグランド参照差動線路105を上記回路ブロック内でグランド110を中心にして差動信号の線路を対称に配置した構成とし、上記信号伝送線路115内ではグランド110を参照しない差動ペア線路111,112のみが前記グランド110を中心とする対称構造の線路から直接延長された構造とする。

(もっと読む)

複合型補正バッファの設計

【課題】複合型インピーダンス補正バッファ回路を提供する。

【解決手段】本発明の一実施例によって、回路を開示する。該回路は、その一部が目標インピーダンスを供給するために使用される複数のドライバスライスと、複数のドライバスライスの一部を選ぶためのデジタル整合論理と、プルアップとプルダウンとを整合させるようバイアス電圧を作るアナログ整合回路とを有する。

(もっと読む)

(もっと読む)

電力低下及び過電圧トレランスを有するバスホールド回路

CMOS構成要素のバスホールド回路であって、DC電流を引き込まず且つ過電圧の許容性がある、バスホールド回路が説明される。入力電圧が前記バスホールドの供給電圧よりも大きい時には、該入力から漏れ電流が引き込まれない。フィードバックインバータが、前記バスホールド回路内においてVin論理をラッチするために用いられる。Vinがローである時には、前記バスホールド回路は、第1のスイッチをターンオンさせ、該第1のスイッチが、PMOSスイッチのゲートをローに駆動して、該PMOSスイッチをオンに切り替える。前記PMOSスイッチは、フィードバック・インバータの電力接続をVccに接続する。前記ゲートは、ローのままとなり、Vinが増加する時に、前記PMOSスイッチをオンに切り替えたままに保持する。前記第1のスイッチがターンオフさせられるが、前記PMOSのゲートは、VinがVccを越えるまでローのままとなる。その時点において、比較器は、前記PMOSのゲートを、PMOSスイッチをオフに切るVinに駆動する。アービタ回路が、前記PMOSスイッチと、前記比較器内及びアービタ回路内における他のPMOS構成要素とのNウェルをバイアスさせるために、Vcc及びVinのうちのより高いものを選択する。このバイアス動作は、Nウェルが決して順方向バイアスされないことを保証し、それによって、Vinからの漏れを防止する。

(もっと読む)

(もっと読む)

長いオンチップバスの動作

テクノロジの縮尺度のために、オンチップ相互接続は幅が狭くなってきており、このような相互接続の高さは、幅に線形に比例しない。これにより、隣接配線とのカップリング容量が増加し、クロストークが高くなる。それはまた、配線の受信側におけるRC応答の不十分さに起因する性能の不十分さに繋がり、非常にノイズの多い環境では、故障の原因になることさえある。受信機スイッチング閾値がバスラインにおいて検出されたノイズに応じて調整される適応閾値構成が提案される。これらのノイズレベルは、フロントエンド処理(トランジスタ性能)とバックエンド処理(金属抵抗、容量、幅及びスペーシング)の両方に依存する。従って、回路は、プロセス変動を自動的に補償する。  (もっと読む)

(もっと読む)

低干渉ラインドライバ

バス通信システムは、通信導電体及びドライバの対を含む。このドライバは、複数の対の被制御型電流源回路を含み、各対は、互いに逆極性の第1及び第2の電流源回路と、各対における電流源により引き寄せられる電流を整合させるための制御回路とを有する。第1の極性の電流源回路は、通信導電体の一方に結合された出力を有し、第2の極性の電流源回路は、通信導電体の他方に結合された出力を有する。遅延線には、各対が、遅延線によって決まるように、連続する対の間の相互遅延をもって連続的にオンに切り換えられるよう、第1及び第2の極性の電流源の制御入力に結合されたタップが設けられる。  (もっと読む)

(もっと読む)

差動信号伝送線路の終端回路

【課題】差動信号伝送線路の終端回路において、ディファレンシャルモード信号及びコモンモード信号に対して、整合センタータップ終端回路を実現しする。また、センタータップ終端回路を単一部品で構成する事により、実装面積を縮小するとともに、部品・実装コストの削減も達成する。

【解決手段】差動信号伝送線路における2つの線路の差動インピーダンスの約1/2である抵抗値を有する第1、第2の抵抗素子を、受信側ICの入力端に直列にして接続し、第1、第2の抵抗素子の中点とプリント配線板のGNDとの間に、第3の抵抗素子と第1のコンデンサ素子を直列に接続する。また、これらの抵抗素子とコンデンサ素子からなるセンタータップ終端回路部品をチップ抵抗部品に、電極、抵抗皮膜、誘電体皮膜を層状に重ね合わせる事により形成して、単一部品で実現する。

(もっと読む)

出力回路装置

【課題】 電源電圧のダイナミックな変動により遅延が変化すると、例えば、クロックバッファのクロック信号にジッター(jitter)が含まれ、高速で正確なタイミングでの動作が困難になる。

【解決手段】 第1の電源線Vddと第2の電源線Vssとの間に少なくとも1つの分離用トランジスタ2a(2a',2b,2b')を有する制御回路を介して接続された出力回路1a(1b)を備える出力回路装置であって、前記分離用トランジスタの制御電極には、一定のレベルに保持された制御電圧Vba(Vba',Vbb,Vbb')が印加され、前記制御電圧は、前記第1または第2の電源線の電圧における高周波成分を減衰させるレベルの電圧であるように構成する。

(もっと読む)

半導体集積回路

【課題】 本発明の目的は、高速・低消費電力の半導体集積回路を提供することにある。

【解決手段】 動作状態にある回路と待機状態にある回路を混在するようにして、回路毎にバックゲート電圧を設定可能にする。

【効果】 待機時には小電流とし低消費電力性を得て、動作時には大電流として高速性を得ることができる。

(もっと読む)

半導体集積回路装置

【課題】 入力回路の簡素化と製品管理の取り扱いを簡便にしつつ、実質的な低消費電力化及び素子の微細化に適合して安定した入出力伝達特性を実現できる入力回路を備えた半導体集積回路装置を提供する。

【解決手段】 外部端子から供給される入力信号を受ける差動増幅回路に第1と第2の動作電圧を第1と第2のスイッチMOSFETを介して供給するようにし、バイアス電圧発生回路により上記入力信号が上記第1と第2の動作電圧の中心電圧付近にあるときに上記第1と第2スイッチMOSFETをオン状態にし、その入力信号が継続的に一定期間上記第1電圧又は第2電圧にあるときには、それに対応した出力信号を形成すべく上記第1又は第2スイッチMOSFETのいずれか一方をオン状態に他方をオフ状態にする制御電圧を形成し、上記第1動作電圧と第2動作電圧に対応した第1振幅の入力信号と、上記第1動作電圧と第2動作電圧の間の所定の中間電圧に対応した第2振幅の入力信号の双方の供給を可能とする。

(もっと読む)

入力回路及び半導体集積回路装置

【課題】外部信号に応答した内部信号を生成する入力回路であって、増幅時に発生する外部信号のエッジから内部信号の立ち上がりエッジ及び立ち下がりエッジの相対的な遅延を改善する。

【解決手段】差動回路は、外部信号DQS ,DQと基準電圧Vref がそれぞれ入力される一対のNMOSトランジスタTN1,TN2を備え、外部信号DQS ,DQと基準電圧Vref に基づいて一対のNMOSトランジスタTN1,TN2にそれぞれ流れる電流に応じて、外部信号DQS ,DQに応答した内部信号dqsz,dqz を出力する。電流調整回路としてのNMOSトランジスタTN4は、外部信号DQS ,DQに対する内部信号dqsz,dqz のレベルに応答して差動回路の電流量を調整すべくオンオフ動作する。

(もっと読む)

921 - 940 / 940

[ Back to top ]