Fターム[5J056EE04]の内容

Fターム[5J056EE04]に分類される特許

1 - 20 / 201

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子面積の増加を抑制しつつ、動作速度が向上する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、ボディ領域11a、11bと、ボディ領域11a、11b上にゲート絶縁層12a、12bを介して配置されるゲート電極13a、13bと、ボディ領域11a、11bを挟んで配置される一対のソース/ドレイン領域14a、14b、14cと、を有する電界効果型トランジスタ10a、10bを複数備え、複数のトランジスタ10a、10bは、ボディ領域11a、11b同士が電気的に接続されており、複数のトランジスタ10a、10bの内の一のトランジスタ10aのゲート電極13aのみが、複数のトランジスタ10a、10bの内の何れかのトランジスタのボディ領域と電気的に接続される。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

レベルシフト回路及び半導体装置

【課題】電源電圧が低電圧化したときの動作不良の発生を抑制することのできるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、第1の高電位電圧VLを信号レベルとする入力信号Siに応じて相補的にスイッチング制御されるNチャネルMOSトランジスタTN1,TN2を有するレベル変換部10を備える。レベルシフト回路1は、第1の高電位電圧VLの低下を検出したことを示す検出信号DSを生成する検出部20と、検出信号DSに応じて、トランジスタTN1,TN2の閾値電圧が低くなるようにトランジスタTN1,TN2のボディバイアスVbbを制御する制御部30とを備える。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

入出力バッファ回路

【課題】チップ面積を削減させると共に、動作周波数をより高くする。

【解決手段】外部接続端子VIOと、ソースを電源に接続し、ドレインを外部接続端子VIOに接続し、ゲートに駆動信号が供給可能とされるPMOSトランジスタMP7と、PMOSトランジスタMP7のバックゲートと電源間に接続され、開閉が制御されるバックゲート制御回路22と、PMOSトランジスタMP7のドレイン・ゲート間に接続され、開閉が制御されるゲート制御回路23と、PMOSトランジスタMP7のゲートと駆動信号が供給される駆動端との間に接続され、開閉が制御される駆動側制御回路24と、を備え、外部接続端子VIOから駆動信号に係る信号を出力しないハイインピーダンス状態において、バックゲート制御回路22および駆動側制御回路24が開放状態とされ、ゲート制御回路23が短絡状態とされる。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

スイッチ回路

【課題】リーク電流がスイッチ回路に接続される回路に影響を与えることを抑制することが可能なスイッチ回路の提供。

【解決手段】第1の電位と第2の電位の間の接続状態をオンオフする第1のトランジスタと、該第1のトランジスタのドレインにソースが接続され、前記第1のトランジスタと略同一の特性を有する第2のトランジスタとを備え、前記第1のトランジスタをオフした時に、前記第1のトランジスタのゲート−ソース間電圧VGS1と、前記前記第2のトランジスタのゲート−ソース間電圧VGS2が略等しくなることを特徴とするスイッチ回路。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

半導体集積回路

【課題】 電源ノイズを緩和しながら、内部回路が動作を開始するまでの時間を短縮する。

【解決手段】 内部回路は、基板電圧が供給されるトランジスタを含み、内部電源電圧を受けて動作する。電源スイッチは、内部回路を動作させるための電源オン信号の活性化中に外部電源線を内部電源線に接続する。基板電圧制御回路は、電源オン信号の活性化により上昇する内部電源電圧が目標電圧を超えたときに、基板電圧を第1電圧から第2電圧に変更する。第1電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流は、第2電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流より少ない。このため、電源スイッチがオンした後、内部電源電圧が低い期間にトランジスタのソース・ドレイン間電流を少なくでき、内部回路を流れる貫通電流を少なくできる。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

クロック負昇圧回路

【課題】回路構成が簡易、小型でウェル・バイアス電圧の立ち上がり時間が短く、安定した負昇圧クロックを供給することが可能なクロック負昇圧回路を提供する。

【解決手段】クロック負昇圧回路部301、クロック負昇圧回路部302、クロック負昇圧回路部301、クロック負昇圧回路部302のウェル層上に設けられたNMOSトランジスタ107に電圧を供給するキャパシタ403、NMOSトランジスタ104を備え、クロック負昇圧回路部301が備えるNMOSトランジスタ104とキャパシタ403とを接続する電圧ライン303、クロック負昇圧回路部302が備える2つのNMOSトランジスタ104の出力を接続する電圧ライン303によってクロック負昇圧回路を提供する。

(もっと読む)

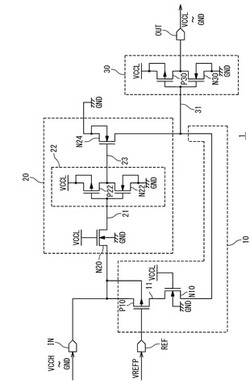

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

半導体集積回路装置

【課題】簡易な構造により、MOSFETのサブスレショールドリーク電流を低減することができる半導体集積回路装置を提供すること。

【解決手段】本発明にかかる半導体集積回路装置は、被制御回路5と基板バイアス制御回路101を有する。被制御回路5は、基板上に形成される1以上のMOSFETを有する。基板バイアス制御回路101は、出力端から被制御回路5の基板に供給する基板バイアスを制御する。基板バイアス制御回路101は、N型MOSFET1及び2を有する。N型MOSFET2は、被制御回路5のMOSFETと同じ電流−電圧特性を有し、サブスレショールドリーク電流を接点Bの電圧VBに変換する。N型MOSFET1は、一端が基板バイアス制御回路101の出力端と接続され、接点Bの電圧VBに応じて基板バイアスを接地電位以下に制御する。

(もっと読む)

SeOI上の疑似インバータ回路

【課題】メモリアレイのワードライン・ドライバ回路として使用できる、大きくなく、低消費電力の回路を提供する。

【解決手段】半導体・オン・インシュレータ(SeOI)基板上に形成された回路であって、電源電位を印加する為の第1、第2の端子間に第2のチャネル型のトランジスタと直列の第1のチャネル型のトランジスタを含み、トランジスタの各々が薄層におけるドレイン領域およびソース領域と、ソース領域とドレイン領域間に延びるチャネルと、チャネルの上方に配置されたフロント・コントロール・ゲートとを備え、各トランジスタが、トランジスタのチャネルの下方のベース基板に形成され、かつトランジスタの閾値電圧を調整する為にバイアスされうるバック・コントロール・ゲートを有し、トランジスタのうちの少なくとも1つが閾値電圧を十分に調整するバックゲート信号の作用の下、空乏モードで動作するように構成される。

(もっと読む)

1 - 20 / 201

[ Back to top ]