Fターム[5J056EE13]の内容

Fターム[5J056EE13]に分類される特許

1 - 20 / 123

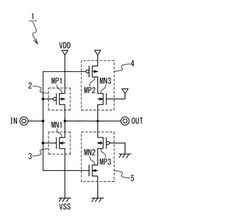

集積回路、集積回路装置及び伝送システム

【課題】回路遅延の増大を抑制しながら、回路しきい値電圧のバラツキを抑制できる集積回路を提供する。

【解決手段】

集積回路1は、高位側電源VDDと出力端子OUTの間に接続されたPMOSトランジスタMP1と、低位側電源VSSと出力端子OUTの間に接続されたNMOSトランジスタMN1と、高位側電源VDDと出力端子OUTの間に直列に接続されたPMOSトランジスタMP2及びNMOSトランジスタMN3と、低位側電源VDDと出力端子OUTの間に直列に接続されたNMOSトランジスタMN2及びPMOSトランジスタMP3とを備えている。PMOSトランジスタMP1、MP2、及びNMOSトランジスタMN1、MN2のゲートが入力端子INに接続されている。また、NMOSトランジスタMN3のゲートは高位側電源に接続され、PMOSトランジスタMP3のゲートは低位側電源に接続されている。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】通信時に発生するノイズを抑制しつつ、高速な通信を可能とする情報処理装置を提供する。

【解決手段】情報処理装置1には、2本1組の信号線7a,7bで構成される信号線対7と信号線対7に対して入力された2進数の複数ビットのデータに応じた電圧レベルに設定するためのドライバ2と、信号線対7の他端側に接続され、信号線対7の電圧レベルに応じて2進数の複数ビットのデータに変換するためのレシーバ3とが設けられる。ドライバ2は、信号線対7に電圧を印加するための定電圧源4と、2進数の複数ビットのデータに応じて信号線対の入出力インピーダンスを調整するスイッチSW6a,6bと、2進数の複数ビットのデータに応じて信号線対のそれぞれの信号線に流す電流の向きを切り替えるスイッチSW9a,SW9b,SW10a,SW10bとを含む。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

半導体装置

【課題】キャリブレーション回路に用いる基準電位生成回路を改良する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ110と、基準電位VREFを生成する基準電位生成回路200と、キャリブレーション端子ZQに現れる電位と基準電位VREFとを比較する比較回路151と、比較回路151による比較の結果に基づいてレプリカバッファ110の出力インピーダンスを変化させるコントロール回路140とを備える。基準電位生成回路200は、イネーブル信号ENに応答して活性化される電位発生部210と、イネーブル信号ENに関わらず活性化される電位発生部220とを含み、電位発生部210の出力ノードと電位発生部220の出力ノードが比較回路151に共通接続されている。これにより、イネーブル信号ENが活性化する前に正しく基準電位VREFを出力することができる。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

レベル変換回路及び半導体装置

【課題】低面積化を図ること。

【解決手段】各信号BDT1〜BDTmをレベルシフトする回路として、クロックトレベルシフト回路(CLS回路)36(361〜36m)を用いた。CLS回路361は、ダイナミックコンパレータ回路(DC回路)411と、ラッチ回路421とを備える。DC回路411は、Lレベルのクロック信号ACKに応答してリセット状態となり、Lレベルの信号CDTm,XCDTmを出力する。また、CLS回路361は、Hレベルのクロック信号ACKに応答して比較状態となり、H1レベルの信号BDTm,XBDTmをH2レベルの信号CDTm,XCDTmにレベル変換する。ラッチ回路421は、相補な信号CDTm、XCDTmに応じた信号ADTm,XADTmを出力し、Lレベルの信号CDTm,XCDTmに応答して出力レベルを保持する。

(もっと読む)

半導体装置及び電子機器

【課題】一導電型のTFTのみを用いて回路を構成することにより工程削減が可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提供する。

【解決手段】出力ノードに接続されているTFT203のゲート−ソース間に容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT203のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることなく、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

電圧レベルシフト回路および半導体装置

【課題】電圧レベルシフト回路において、入力信号の信号レベルによる応答特性の差違を抑制する。

【解決手段】電圧レベルシフト回路は、入力信号とは異なる電圧振幅を有する出力信号VOUTを生成する。インバータINV2は、入力信号にしたがってVSS〜VDDIの範囲の電圧V1を生成する。インバータINV3は、入力信号にしたがってVSS〜VPERIの範囲の電圧V2を生成する。インバータINV4は、V1およびV2にしたがって出力信号VOUTを生成する。

(もっと読む)

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

消費電力錯乱型論理回路及び情報記憶媒体

【課題】入力信号の組合せにより充電経路の平均数が異なるため、及び後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減する。

【解決手段】論理回路1は、入力信号X、Yと乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10と、制御信号en1に応じて出力線Z1の出力状態を制御し、論理演算回路10の出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線VDDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、制御信号en2に応じて切り替える出力段回路30とを備える。

(もっと読む)

集積回路

【課題】単独の動作モード信号で動作モードを切り替えるコンパレータ回路において、コンペアモードでコンパレータ回路の出力値が確定した後も、入力部から出力部に向けて不要な電流が流れてしまう。

【解決手段】本発明の集積回路では、コンパレータ回路に、入力部および出力部の間の、リーク電流が通る電流パスに含まれるトランジスタを制御する論理回路を追加する。この論理回路は、動作モード信号と、コンパレータ回路の出力信号とを入力し、コンパレータ回路の出力信号が確定した後は電流パスを遮断状態にする。

(もっと読む)

出力回路、入力回路及び入出力回路

【課題】自身の電源電位より高い電位のみならず、自身の接地電位GNDより低い電位が印加されても、トランジスタ素子の破壊や、電流の流れ込み、流れ出しを防止することを目的としている。

【解決手段】出力端子から当該出力回路への電流の流れ込みを防止する第一のリーク電流防止回路と、当該出力回路から前記出力端子への電流の流れ出しを防止する第二のリーク電流防止回路と、前記出力端子に当該出力回路の電源電圧よりも高い電圧が印加されたとき、前記第一のリーク電圧防止回路を動作させ、前記出力端子に接地電圧よりも低い電圧が印加されたとき、前記第二のリーク電流防止回路を動作させる選択回路と、を有する。

(もっと読む)

レベルシフト回路及びそれを内蔵した半導体集積回路

【課題】2つの入力信号が共にローレベルとなっても、レベルシフト回路の出力信号を特定のレベルに固定して、次段の回路の誤動作を防止する。

【解決手段】このレベルシフト回路は、第1の電源電位が供給されて動作する回路から入力される互いに逆相の第1の信号及び第2の信号に基づいて、第1の電源電位よりも高い第2の電源電位に対応する振幅を有する第3の信号を出力する電圧変換部と、第1のPチャネルトランジスタ及び第1のNチャネルトランジスタによって構成され、第3の信号を反転して出力端子から出力信号を出力するインバータと、第1のNチャネルトランジスタのソースと接地電位との間に接続され、第1及び第2の信号によってそれぞれ制御される第2及び第3のNチャネルトランジスタと、第2の電源電位とインバータの出力端子との間に接続され、微小電流を流すインピーダンス素子とを具備する。

(もっと読む)

シリアル出力回路、半導体装置およびシリアル伝送方法

【課題】 高速シリアル伝送で使用するデエンファシスを備えた出力回路において、出力振幅で発生するコモンモード電位の変動を抑制する回路を提供する。

【解決手段】 デエンファシスを備える差動伝送のシリアル伝送装置の出力回路のP極とN極とに、送信するデータのパターンの検出装置と送信するデータの反転パターンの検出装置の出力とをそれぞれ差動入力とする、差動回路の出力を接続する。接続される差動回路によって、特定の送信するデータのパターンおよびその反転パターンの出現時に出力回路の電流が補われ、コモンモードノイズを防ぐことができる。

(もっと読む)

半導体集積回路

【課題】データ選択機能付きのダイナミック型フリップフロップ回路において、動作の高速性を良好に確保しながら、複数のデータの何れもが選択されていない場合であっても、正常動作するようにする。

【解決手段】例えば選択信号S0によりHのデータD0が選択されていた場合、第1ノードN1がLとなり、第2ダイナミック回路1Bの第2ノードN2はHとなっており、出力信号QはHレベルである。この状態において、選択信号S0〜S2によって複数のデータD0〜D2の何れもが選択されなくなった際には、第1ノードN1がHとなり、前記第2ノードN2は、その電荷が放電されて、出力信号QはLレベルに誤動作する状況となる。しかし、この場合には、出力ノードN3がHとなり、第4ノードN4がLとなって、前記第2ダイナミック回路1Bのn型トランジスタTr6がオフして、第2ノードN2の放電を阻止する。

(もっと読む)

表示装置

【課題】回路によりトランジスタの高耐圧化を図り、信頼性の向上、あるいは設計・プロセス裕度の拡大を図った表示装置を提供する。

【解決手段】単チャネルシフトレジスタを有し、前記単チャネルシフトレジスタは、多段に縦続接続されるn(n≧2)個の基本回路を有し、前記基本回路は、V1の基準電圧が印加される電源線に第1の電極が接続される第1のトランジスタと、第1の電極が、前記第1のトランジスタの第2の電極に接続され、制御電極に、Vcのバイアス電圧が印加される第2のトランジスタとを有し、前記第1のトランジスタがオフ状態のときに、前記第2のトランジスタの第2の電極に印加される最大電圧をV2とするとき、V1<Vc<V2を満たし、前記基本回路は、制御電極が、前記第2のトランジスタの第2電極に接続されるセット用トランジスタと、前記セット用トランジスタの第2電極と制御電極との間に接続される容量素子とを有する。

(もっと読む)

出力バッファ回路

【課題】ハイ・インピーダンスにする際に発生する電源ノイズを低減させる出力バッファ回路を提供する。

【解決手段】出力バッファ回路10は、データ信号DA及び制御信号DCに基づいて、PMOSトランジスタT1をオンからオフさせNMOSトランジスタT2をオフからオンさせて出力端子Poを第1状態に、PMOSトランジスタT1をオフからオンさせNMOSトランジスタT2をオンからオフさせて出力端子Poを第2状態に、又、両トランジスタT1,T2をオフさせて出力端子Poをハイ・インピーダンスとなる。そして、オフ時間制御回路部13によって、第1状態又は第2状態からハイ・インピーダンスにする制御信号が入力された時、オンからオフさせるためにPMOSトランジスタT1又はNMOSトランジスタT2のゲートに供給される信号の立ち上がり波形又は立ち下がり波形を緩やかにする

(もっと読む)

1 - 20 / 123

[ Back to top ]