Fターム[5J056FF07]の内容

Fターム[5J056FF07]に分類される特許

141 - 160 / 879

半導体装置

【課題】終端抵抗のオンオフの切り替え時に外部端子にインピーダンスの急激な変化が生じることを低減する。

【解決手段】外部端子(図2のDQに相当)と、外部端子に接続され、出力信号を外部端子に出力可能とする出力回路(図2の21に相当)と、外部端子に終端抵抗をオンオフ可能に接続する終端回路(図2の22に相当)と、終端抵抗がオフ状態又はオン状態のいずれか一方の状態から他方の状態に変化するまでの時間を、データ出力時に出力信号が一方の論理レベルから他方の論理レベルへ変化するまでの時間以上となるように制御する第1のスルーレート制御回路(図2の23aに相当)と、を備える。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

電気回路

【課題】本発明は、端子数を低減した電気回路を提供することを目的とする。

【解決手段】第一回路と、該第一回路に接続された第一端子と、該第一回路と同時使用されない第二回路と、該第二回路に接続された第二端子と、該第一回路および該第二回路に接続された第三端子と、該第一回路および該第二回路に印加される電源電圧と所定の基準電圧とを比較し、該電源電圧と該基準電圧の大小に応じて該第一回路または該第二回路のいずれか一方を停止させる切り替え手段とを備える。そして、該切り替え手段により該第一回路を停止させた場合には該第二回路が該第二端子と該第三端子により信号の入出力を行い、該切り替え手段により該第二回路を停止させた場合には該第一回路が該第一端子と該第三端子により信号の入出力を行うことを特徴とする。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

半導体装置

【課題】内部電源電圧の急激な変化に追従し、安定した内部電源電圧を供給することができる電源部を備えた半導体装置を提供する。

【解決手段】半導体装置は、集積回路からなるコア回路と、内部電源からの電圧および外部電源からの電圧を受け、コア回路から転送されるデジタルデータを出力するドライバと、コア回路からのデータを一時的に保持し、前記ドライバに該デジタルデータを転送するフェッチ部とを含む周辺回路と、ドライバに電源線を介して内部電圧を供給する第1の電源部と、外部電源と電源線との間に直列に接続された電流駆動素子およびスイッチング素子をそれぞれ含む複数の電流駆動列を備え、複数の電流駆動列を駆動することによって第1の電源部とは別に電源線に電流を供給する第2の電源部と、デジタルデータの連続するビット間で論理が遷移するときに複数の電流駆動列の少なくとも1つを駆動させるように第2の電源部を制御する電源制御部とを備える。

(もっと読む)

半導体集積回路

【課題】書き込み回数に制限がなく、回路規模の増加に対して消費電力を抑制することができる半導体集積回路を提供する。

【解決手段】ルックアップテーブル101とフリップフロップ102Aのラッチ回路以外の回路構成部との電源供給経路を分離し、ルックアップテーブル101とラッチ回路以外の回路構成部とを別個に電源制御する電源コントローラ109及び電源制御回路111を備える。

(もっと読む)

バッファ回路

【課題】出力の反射を抑制しつつスルーレートを高い自由度を持って調整可能なバッファ回路を提供する。

【解決手段】

複数の出力トランジスタPOA1〜POE1は、電源端子(電源電圧VCCQ)と出力端子DoutP1との間に電流経路を並列接続され導通することにより出力端子DoutP1の電圧を変化させる。ゲート制御用トランジスタTA1〜TE1は、接地端子Dgndと出力トランジスタPOA1〜POE1のゲートとの間、又は2つの出力トランジスタのゲートの間に電流経路を形成するように接続され、出力トランジスタにゲート電圧を与える。ゲート制御用トランジスタTA1〜TE1のゲートは、ゲート制御用トランジスタTA1〜TE1のソースの電圧が変化したときにゲート−ソース間の電位差が閾値電圧以上となって導通するよう、所定の電圧を与えられている。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力で安定に動作する回路装置及び電子機器等を提供する。

【解決手段】回路装置は、組み合わせ論理回路100と、記憶回路110とを含む。組み合わせ論理回路100は、断熱的回路動作を行い、記憶回路110の帰還ループを構成する回路120は、非断熱的回路動作を行う。記憶回路110は、組み合わせ論理回路100の断熱的回路動作のホールド期間において、組み合わせ論理回路100からの信号を取り込んで記憶し、非ホールド期間において、記憶された信号に基づいて組み合わせ論理回路100への出力を変化させる。

(もっと読む)

半導体装置

【課題】 半導体装置の電源投入時におけるノイズの影響及び電圧降下を抑制すること。

【解決手段】 本半導体装置は、複数の内部回路に第1電圧を供給するための第1電源線及び第2電源線を備える。第1電源線と内部回路の間には第1スイッチが、第2電源線と内部回路の間には第2スイッチがそれぞれ設けられている。制御回路20は、複数の内部回路1〜3のうち一の内部回路3の電源投入時において、第1スイッチSW3Aに続いて第2スイッチSW3Bをオンにすることで電源を投入する。また、電源投入に伴い発生するノイズ及び電圧降下の大きさに基づいて、他の動作中の内部回路1〜2における第1スイッチSW1A及びSW2Aを制御する。この構成によれば、内部回路の電源投入時におけるノイズの影響及び電圧降下を抑制することができる。

(もっと読む)

電圧調整回路

【課題】電圧調整回路を提供するための改善された技法を提供する。

【解決手段】供給電圧ノードを出力電圧ノードに接続するプルアップp型閾値デバイスであって、制御信号に依存してオフに切り替えられるように構成されるプルアップp型閾値デバイスを備える電圧調整回路が提供される。プルダウンスタックは、出力電圧ノードを基準電圧ノードに接続し、プルダウンスタックは、直列で接続されるプルダウンp型閾値デバイスおよびプルダウンn型閾値デバイスを備える。インバータは、出力電圧ノードから入力を受け取るように構成され、カットオフ信号を生成するように構成され、プルダウンn型閾値デバイスは、制御信号に依存してオンに切り替えられるように構成され、プルダウンp型閾値デバイスは、カットオフ信号に依存してオフに切り替えられるように構成される。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】断熱的回路動作と非断熱的回路動作を切り替え可能である回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、論理回路200と、電源回路100と、を含む。第1のモードでは、電源回路100は、非直流の電源電圧VPK、VMKを論理回路200に供給し、論理回路200は、その非直流の電源電圧VPK、VMKが供給されることで断熱的回路動作を行う。第2のモードでは、電源回路100は、直流の電源電圧VDD、VSSを論理回路200に供給し、論理回路200は、その直流の電源電圧VDD、VSSが供給されることで非断熱的回路動作を行う。

(もっと読む)

半導体集積回路

【課題】固定電位と入力信号を比較するカレントミラー型差動増幅器において、入力信号の立ち下り時に出力信号の遷移の遅れを改善して入力信号の立ち上がり時と立ち下がり時で出力信号の遷移時間差を少なくする。

【解決手段】カレントミラー型差動増幅器1-1 のミラートランジスタの共通ゲート端子のノードGPと定電流源回路TNCSの一端との間に、差動増幅器の出力信号OUTnをゲート入力とするトランジスタTNK1と、差動増幅回路の出力信号とは逆の論理の信号OUTpをゲート入力とするトランジスタTNK2とを直列に接続する。

(もっと読む)

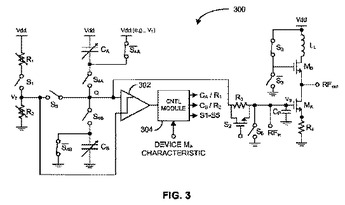

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

インピーダンス調節装置

【課題】小さい面積でも正確なインピーダンス値でターミネーション動作をするインピーダンス調節装置を提供する。

【解決手段】基準電圧VREFとキャリブレーションノードZQの電圧とを比較する比較部410と、比較部410の比較結果UP/DOWNに応じてインピーダンスコードPCODE<0:N>をカウントするカウント部420と、インピーダンスコードPCODEによって決定されるインピーダンス値を有し、キャリブレーションノードZQに連結されるレファレンスインピーダンス部430と、インピーダンスコードPCODEの生成完了時に、比較部410の比較結果を保存する保存部440と、インピーダンスコードPCODE<0:N>に応答してオン・オフされる複数の並列抵抗611〜615と、保存部440に保存された信号TRIMに応答してオン・オフされる抵抗616とで、所定のパッドをターミネーションするターミネーション部とを備える。

(もっと読む)

内部コマンド生成回路

【課題】電流消耗を減少させることができる内部コマンド生成回路を提供する。

【解決手段】本発明の内部コマンド生成回路は、読出しまたは書込み動作のためのコマンドを受信して、所定の周期で発生する複数のパルスを含む第1バーストパルスを生成するバーストパルス発生部と、前記第1バーストパルスをシフトして内部コマンドを生成するパルスシフト部と、を含み、前記内部コマンドは、バースト終了信号またはバーストコマンドのパルスが入力されるとディセーブルされる。

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

141 - 160 / 879

[ Back to top ]