Fターム[5J056GG08]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382) | 時間遅延を利用するもの (128)

Fターム[5J056GG08]に分類される特許

1 - 20 / 128

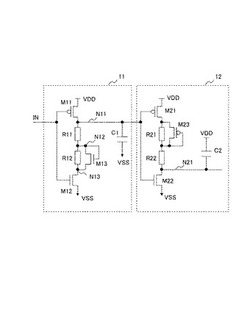

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

半導体記憶装置

【課題】電源電圧の停止及び復帰を行う構成において、外部回路より半導体記憶装置を制御するための信号数を削減する。

【解決手段】酸化物半導体を半導体層に有するトランジスタを有する記憶回路と、記憶回路に保持されたデータを読み出すための電荷を蓄積する容量素子と、容量素子への電荷の蓄積を制御するための電荷蓄積回路と、データの読み出し状態を制御するデータ検出回路と、電源電圧が供給された直後の期間において、電源電圧の信号と電源電圧を遅延させた信号とにより、電荷蓄積回路による容量素子への電荷の蓄積をさせるための信号を生成するタイミング制御回路と、容量素子の一方の電極の電位を反転して出力するインバータ回路と、を有する構成とする。

(もっと読む)

半導体集積回路およびその動作方法

【課題】高耐圧回路の素子破壊を防止する際、半導体チップ面積の増大を軽減する。

【解決手段】半導体集積回路ICは、高電源電圧で動作する高耐圧回路100、200と低電源電圧で動作する低耐圧回路300、400を内蔵する。入力信号Aに応答して、高耐圧回路の第1素子5と第2素子3はオン状態とオフ状態に、低耐圧回路の第3素子7と第4素子8はオフ状態とオン状態に制御される。この状態において、高電源電圧供給端子に所定レベルのサージ電圧が供給される。この状態で、初期サージ電流が第1素子5と第2素子3の容量を介して低耐圧回路の出力端子Yに流入する。出力端子Yの電圧降下は、高耐圧回路の第2素子3のターンオン電圧に設定される。第2素子3はオフ状態からオン状態に制御されて、サージ電圧のエネルギーを吸収するサージ吸収電流が第1素子5と第2素子3に流入する。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

集積回路及び集積回路の制御方法

【課題】回路若しくは装置が、仕様或いは規格に適用しない部分があったとしても、使用することに問題がない場合の対応方法のひとつを提供する。

【解決手段】集積回路が入出力回路とタイミング測定回路とを含み、前記入出力回路の第1の入力端子に入力される第1の信号と、前記入出力回路の第1の出力端子から出力される第2の信号とが前記タイミング測定回路に入力され、前記第2の信号は、前記入出力回路の第1の入出力端子における信号が前記第1の出力端子から出力されたものであり、前記タイミング測定回路において、前記第1の信号における第1の変化を検出し、前記第2の信号における前記第1の変化に対応する第2の変化を検出し、前記第1の変化を検出したときと前記第2の変化を検出したときとの間の時間間隔の計測を行うことを特徴とする。

(もっと読む)

タイミング制御回路、タイミング制御方法、及びシステム

【課題】タイミングマージンの減少を抑制すること。

【解決手段】システム装置21に形成された制御回路36は、可変容量35の容量値を制御し、トレーニング回路45にタイミングトレーニングを実行させる。トレーニング回路45は、メモリ12がデータDQに基づく正常なデータを書き込むことができる設定値の最大値と最小値を出力する。制御回路36は、その最大値及び最小値に基づいてデータDQのウインドウ幅を算出し、より大きなウインドウ幅に対応する容量値を可変容量35に設定する。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

エンファシス信号生成回路及び信号合成回路

【課題】電力消費の無駄を低減する。

【解決手段】加減算部100は第一信号と第二信号とを所定の比率で加減算するものであり、その比率は可変自在である。振幅調整部300は信号の振幅の調整を行うものである。直流レベル調整部400は、加減算部100に入力される信号の直流成分のレベルを調整する。回路への第一の入力信号は第一信号として加減算部100に入力される。回路への第二の入力信号は、振幅調整部300によって振幅の調整が行われると共に直流レベル調整部400によって直流成分のレベルが調整された上で、第二信号として加減算部100に入力される。

(もっと読む)

スキュー調整回路

【課題】

LSIの動作状態などに適合したスキューを複数の信号に与えることができるスキュー調整回路を提供する。

【解決手段】

第1及び第2の信号をそれぞれ伝播する第1及び第2の信号線と,第1及び第2の信号線を伝播する第1及び第2の信号がそれぞれ入力される第1及び第2のバッファ回路とを有する集積回路に設けられるスキュー調整回路であって,第1及び第2のバッファ回路の前段にそれぞれ設けられた第1及び第2の遅延回路と,第1及び第2の信号の間のスキューを測定するスキュー測定回路と,スキュー測定回路が測定した測定スキューに基づいて前記第1,第2の遅延回路の遅延量を決定し,当該決定した遅延量を前記第1,第2の遅延回路に設定する遅延調整回路とを有する。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

ワイヤ遷移を検出し支援する回路および方法

【課題】ワイヤ上の信号遷移を支援する回路及び方法を提供する。

【解決手段】回路は、第1のサブ回路を含み、サブ回路は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間ターンオンさせ、その後ターンオフさせる。第1のトランジスタ(16)は、出力(34)を高状態に駆動して、立ち上がり遷移を支援する。回路は、第2のサブ回路を含み、第2のサブ回路は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間ターンオンさせ、その後ターンオフさせる。第2のトランジスタ(25)は、出力(34)を定状態に駆動して、立ち下がり遷移を支援する。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

1 - 20 / 128

[ Back to top ]