Fターム[5J079BA04]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 補償 (687) | 電源電圧変動の補償 (32)

Fターム[5J079BA04]に分類される特許

1 - 20 / 32

水晶発振回路

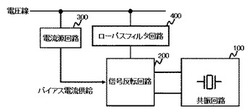

【課題】差動回路を使用することで、貫通電流に起因した高調波ノイズの影響を排除した水晶発振回路を構成することができる。しかし、他の回路が動作することによって生じた高調波ノイズが、水晶発振回路の発振出力に影響を与える場合がある。そのため、電源電圧が変動したことによる影響を軽減し、発振出力のジッタを抑制した水晶発振回路が、望まれる。

【解決手段】水晶発振回路は、水晶振動子を含む共振回路と、共振回路と接続され、差動対を含む信号反転回路と、差動対にバイアス電流を供給する電流源回路と、信号反転回路及び電流源回路に電源を供給する電圧線と信号反転回路の間に接続され、水晶振動子の固有の発振周波数より低い遮断周波数を持つローパスフィルタ回路と、を備えている。

(もっと読む)

水晶デバイスおよび電子機器

【課題】水晶デバイスおよび電子機器の小型化を図ること。

【解決手段】実施形態によれば、容器体と、水晶素子と、電解質部材とを備える水晶デバイスが提供される。容器体は、1または複数のキャビティを有する。水晶素子は、キャビティ内に配置される。電解質部材は、少なくとも一部がキャビティ内に配置される。また、実施形態によれば、これらの容器体と、水晶素子と、電解質部材とを備える水晶デバイスを搭載した電子機器が提供される。

(もっと読む)

発振装置

【課題】電源電圧の変動による発振周波数の変動を抑え、安定して発振する発振装置を提供する。

【解決手段】発振装置において、水晶振動子を接続する入出力端子に有する静電保護回路のNMOSトランジスタのドレインを接地電位に接続し、ゲートとソースと基板は水晶振動子の入出力端子を接続し、さらに接地電位と電源間に静電保護回路を備えることにより、電源電圧の変動による水晶発振回路の寄生容量値は変化せず、発振周波数の変動を抑え、安定して発振できる。

(もっと読む)

水晶発振回路

【課題】反転電圧VTH、負性抵抗−RL、発振周波数f0が電源VDDの影響を受けることがなく、定電圧回路を追加する必要がなく、しかも、動作電圧も低くなり、水晶振動子に流れる電流も小さくすることができる発振回路を提供する。

【解決手段】NMOSインバータIVnと、帰還抵抗Rfと、水晶振動子Qzと、が互いに並列接続され、NMOSインバータIVnの入力と電源VSSとの間にキャパシタCGが接続され、NMOSインバータIVnの出力と電源VSSとの間にキャパシタCDが接続された水晶発振回路1において、NMOSインバータIVnが、電源VDDに接続された定電流回路Inと、定電流回路Inと電源VSSとの間に接続されたn型のMOSトランジスタTnと、から構成されている。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

圧電発振器

【課題】 発振周波数の調整を容易に安価に行うことができると共に電源電圧変動による周波数変化を抑制できる圧電発振器を提供する。

【解決手段】 周波数調整回路と発振回路1とを備え、発振回路1の入力側に、可変容量ダイオードD3のカソードを接続し、更に当該カソードを第3の抵抗R3を介してポテンショメータRvの制御電圧電極に接続し、ポテンショメータRvには電源電圧Vccがレギュレータ2を介して印加されるようになっているので、電源電圧の変動に対しても可変容量ダイオードD3のカソードに一定の電圧を印加して周波数変化を抑制でき、ポテンショメータRvから可変容量ダイオードD3のカソードに印加する電圧を変更することで周波数の調整を行う圧電発振器である。

(もっと読む)

水晶発振回路用の電圧源回路

【課題】水晶発振回路の一定の電力消耗を維持できる水晶発振回路用の電圧源回路を提供する。

【解決手段】水晶発振回路用の電圧源回路が提供され、そのうち、電圧源回路および水晶発振回路が同一プロセスにより形成される。電圧源回路が、電流源と、第1PMOSと、第1NMOSと、調整器ユニットとを含む。電流源が電圧源および出力端間に連結され、そのうち、出力端が参考電圧を出力する。第1PMOSおよび第1NMOS双方のゲートおよびドレインが互いに連結されるとともに、第1PMOSおよび第1NMOSが出力端ならびに接地間に連結される。調整器ユニットが、参考電圧に従って水晶発振回路の電圧源として水晶発振回路への作業電圧を発生させる。

(もっと読む)

水晶発振器の梱包容器

【課題】高安定水晶発振器を搭載した製品の検査時間を短縮し、精度の良い検査を可能とし、製品の品質ばらつきを低減することが可能な水晶発振器の梱包容器を提供する。

【解決手段】水晶発振器の梱包容器10は、少なくとも1つの水晶発振器12が収納可能な収納部11Aと、個々の水晶発振器12に電源電圧を供給することが可能な少なくとも1つの電源電圧供給部13A、13Bと、個々の水晶発振器12に対応してそれぞれ設けられ、水晶発振器12からの出力信号を外部出力することが可能な少なくとも1つの出力端子17とを備えている。

(もっと読む)

発振回路、アクティブタグ及び発振出力制御方法

【課題】出力特性の変化を抑制でき、構成を簡略化できる発振回路、アクティブタグ及び発振出力制御方法を提供すること。

【解決手段】交流電流を出力する発振回路3であって、電源部と、エミッタQ3、ベースQ2及びコレクタQ1を有し、コレクタQ1に電源部からの直流電圧が印加されるトランジスターQと、コレクタQ1に接続され、前記交流電流が出力される出力端子Tと、エミッタQ3から出力されるエミッタ電圧を測定する電圧測定手段(A/Dコンバーター)53と、電圧測定手段53によるエミッタ電圧の測定結果に基づいて、エミッタ電圧が一定となるように、ベースQ2に印加されるベース電圧を制御する電圧制御手段(CPU)6とを有する。

(もっと読む)

水晶発振器及び無線装置

【課題】搭載される無線装置の検査時間短縮を図り、高安定した周波数を発振できる水晶発振器及び無線装置を提供する。

【解決手段】本発明の高安定水晶発振器100は、外部入力端子1と、外部入力端子1に接続され、水晶振動子3を有する発振回路4と、を備え、発振回路4に電力供給可能な内部バッテリー回路6を備えた構成となっている。

(もっと読む)

高周波回路

【課題】簡単な構成でバッファ回路の増幅素子に安定した直流電源を供給でき、動作の安定化を図ること。

【解決手段】この高周波回路は、高周波信号と共に安定化した直流電圧を出力する発振回路10と、発振回路10から出力される発振信号を後段回路へ出力するためのバッファ用トランジスタ21を有するバッファ回路20と、発振回路12の出力端10aとバッファ用トランジスタ21の入力端との間に接続され前記発振信号を前記バッファ用トランジスタ21のベースへ伝えるバイパスコンデンサ23と、バイパスコンデンサ23に対して並列に接続され安定化電圧をバッファ用トランジスタ21のベースに印加するためのバイアス抵抗24とを具備している。

(もっと読む)

発振回路および発振器

【課題】発振回路におけるロード電流の消費電力を低減化して、周波数調整の安定化を図ることを目的としている。

【解決手段】本発明の発振回路10は、外部の圧電振動子22を発振させ発振信号を出力する発振部20と、圧電振動子22が発振している状態で発振信号を出力するか否かを切替える出力バッファ60と、発振部20に接続された負荷容量を備え、この負荷容量を可変する可変容量回路30と、可変容量回路30の補正値データを記憶する記憶部42と、記憶部42からの補正値データを保持し、負荷容量を可変する信号を可変容量回路30へ出力するラッチ回路44と、出力バッファ60における出力停止から出力開始への切替えをトリガとして、ラッチ回路44に記憶部42の補正値データをロードする読み込み制御部50と、を備えている。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発

振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位

を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路から

なり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が

接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電

流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御

し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

発振回路

【課題】ノイズの増加を抑制しつつ、安定した発振周波数を得ることができる発振回路を提供すること。

【解決手段】振動子1と、振動子1の両端に接続されるコンデンサ2a,2bと、振動子1と並列に接続された複数のインバータ41〜4nと、複数のインバータ41〜4nに並列に接続された帰還抵抗3とを含む発振部と、その発振部の発振周波数に基づいて、複数のインバータ41〜4nから使用するインバータ数を調整する発振制御回路6とを備えるものである。

(もっと読む)

電圧制御温度補償水晶発振器及び温度−発振周波数特性調整方法

【課題】制御電圧入力端子22への基準電圧の印加に対して公称の発振周波数を生成するVC−TCXO10において、温度変化に伴う印加電圧の変動にもかかわらず、高精度の発振周波数を維持する。

【解決手段】定電圧回路11は水晶発振回路14へ供給する定電圧を生成する。定電圧出力端子20は、該定電圧を外部へ導出する端子となっている。恒温槽30におけるVC−TCXO10の温度−発振周波数特性調整時では、定電圧出力端子20−制御電圧入力端子22間に接続線38が接続されるとともに、発振周波数が使用許容温度範囲全体にわたり公称値になるように、温度補償回路12の制御データが温度補償回路調整端子21から設定される。携帯型無線機45へのVC−TCXO10の実装時では、接続線52が定電圧出力端子20−制御電圧入力端子22間に接続される。

(もっと読む)

発振装置、半導体装置、電子機器および時計

【課題】水晶発振回路を含む発振装置、半導体装置、電子機器等の消費電力を全体として抑制する。

【解決手段】発振装置は、第1の定電流を生成する第1の定電流源と、第1の定電流が通電され、定電圧を生成する定電圧制御トランジスタとを含む定電圧生成回路と、定電圧発生回路から供給される定電圧により発振駆動される水晶発振回路とを備える。定電圧は、動作保証温度範囲において第1の定電流に応じて変動する第1の傾きを有する。水晶発振回路において、動作保証温度範囲における発振停止電圧は第2の傾きを有する。第1の傾きは、第1の傾きと第2の傾きとの差と相関を有する水晶発振回路の消費電流と、第1の定電流の大きさと相関を有する定電圧生成回路の消費電流との和を極小とするように定められている。

(もっと読む)

発振回路

【課題】動作電圧範囲の広い発振回路を提供する。

【解決手段】両端にキャパシタc1、C2が接続された振動子11と、出力抵抗R1を介して振動子11に並列接続されたインバータ12を有する反転増幅部13と、インバータ12に並列接続されたトランスミッションゲート14、15を有する帰還抵抗部16と、同一導電型で、閾値電圧の異なるn型第1および第2MOSトランジスタM1、M2の直列回路を有し、電源電圧Vddのレベルに応じて、第1および第2MOSトランジスタM1、M2が相補的にオンまたはオフして帰還抵抗部16の抵抗値を可変するための制御信号A1、A2を出力する制御手段17と、を具備する。

(もっと読む)

定電圧回路及びそれを用いた水晶発振回路

【課題】 発振起動時のβUPにおける出力電圧の微調整が容易に行え、かつプロセスにてMOSトランジスタの閾値電圧の制御を行う必要がない定電圧回路を提供する。

【解決手段】 本発明の定電圧回路は、定電力出力部が、ソースが電源に接続され、ゲートに差動増幅回路の出力が入力され、定電圧を出力する第1Pチャネル型MOSトランジスタと、第1Pチャネル型MOSトランジスタのドレインにソースが接続され、ゲートがドレインに接続された第2Pチャネル型MOSトランジスタとからなり、該定電圧出力部の電圧を調整するリファレンス電流を流す、前記第2Pチャネル型MOSトランジスタに接続された第1の定電流回路と、第1定電流回路に並列に接続され、制御信号が入力されることにより所定の電流を流す第2定電流回路と、定電圧の帰還成分及びリファレンス電圧を比較し、定電圧出力部が出力する定電圧を調整する差動増幅回路とを有する。

(もっと読む)

出力回路を備えた発振回路

【課題】電源電圧を低電圧化した場合においても、発振回路の最終出力波形のデューティー比を50%に調整し易く、且つ、種々の外乱要因によってもデューティー比の変動を少なく抑えることが可能な発振回路を提供する。

【解決手段】振動子、増幅回路及び出力回路を含む発振回路であって、前記増幅回路の入力端子に接続される側の前記振動子の端子と、前記出力回路の入力端子とが接続され、振動子の前記端子と、増幅回路の前記入力端子とが容量を介して接続され、さらに、振動子の前記端子側に、所定の電位をバイアスするためのバイアス回路が接続されている。

(もっと読む)

発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器

【課題】入出力端子を介して外部から侵入するサージ電圧から前記主要回路部分を保護することができ、しかも発振回路の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器を提供すること。

【解決手段】主電源の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路を提供すること。

発振回路40に設けられた静電保護回路200は、信号路と前記定電圧Vreg側との間に接続され、信号路に侵入する第1の極性の静電圧をダイオード72を介してバイパス用定電圧Vreg側へバイパスさせる第1の静電保護回路部210と、前記信号路とアース側との間に接続され、信号路に侵入する第2の極性の静電圧をダイオード74を介してアース側へバイパスさせる第2の静電保護回路部220とを含む。

(もっと読む)

1 - 20 / 32

[ Back to top ]