Fターム[5J079BA42]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 低消費電力化 (202) | 動作電圧低減 (41)

Fターム[5J079BA42]に分類される特許

1 - 20 / 41

発振回路、発振器、電子機器及び発振回路の起動方法

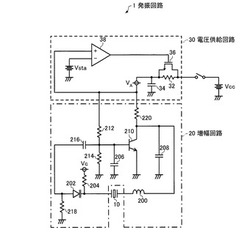

【課題】起動時の異常発振を抑えるとともに負荷の大きさによらず電源電圧の低電圧化が可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(水晶振動子10)と、共振子の一端から他端への帰還経路を有する増幅回路20と、電圧供給回路30と、を含む。電圧供給回路30は、電源電圧Vccが入力される時定数回路(抵抗32とコンデンサー34によるRC積分回路)を有し、電源電圧Vccが入力されてから時定数回路の時定数に応じて立ち上がるとともに増幅回路20の負荷によらず一定電圧となる駆動電圧VAを発生させ、駆動電圧VAを増幅回路20に供給する。

(もっと読む)

半導体装置

【課題】消費電力の低減と、製造コストの低減とを両立する発振回路を提供する。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

(もっと読む)

水晶発振器

【課題】電源電圧が低電圧化されても安定した発振動作が可能な水晶発振器を提供する。

【解決手段】本発明の水晶発振器は、高電位側電源と水晶振動子(2)の一端並びに他端との間に設けられた第1,第2の抵抗(R1,R2)と、その一方の主端子が前記水晶振動子の一端並びに他端と接続された第1,第2のトランジスタ(T1,T2)と、第1,第2のトランジスタの他方の主端子間に接続されたキャパシタ(C1)と、第1,第2のトランジスタの他方の主端子と低電位側電源との間に設けられた電流源(IR1,IR2)又は抵抗と、第1,第2のトランジスタの一方の主端子と第2,第1のトランジスタの制御端子との間に設けられ、一方の主端子の電圧に追従するとともに一方の主端子の電圧から直流オフセット電圧分降下した電圧を生成して制御端子に印加させる第1,第2の電圧フォロワ回路(4,5)と、を備える。

(もっと読む)

水晶発振回路における負荷容量の決定方法、水晶発振回路における負性抵抗RLの決定方法、発振回路、及び電子機器

【課題】本発明の目的は、低い負荷容量有する水晶発振回路において、負荷容量、及び負性抵抗RLを決定する決定方法を提供するものである。

【解決手段】(CLn+1/CLn)2=α(nは1以上の整数、α=2-1/2)が成立するように、負荷容量CL1に対して負荷容量CLn(n≧2)を決定する。さらに、CMOSインバータの入力側と出力側の間に最小帰還抵抗Rfminと並列に配置されたリーク抵抗Rzを仮想して、最小合成帰還抵抗RFminを式RFmin=(Rfmin×Rz)/(Rz+Rfmin)を用いて決定し、最大負性抵抗RLmaxの値を、式(RLmax/RFmin)1/2 <α(αは安全係数で2-1/2)を用いて決定する。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

発振装置および該発振装置を具備したクロック発生装置、半導体装置、ならびに電子装置

【課題】過渡的な電力消費をしないピークホールド回路(あるいはボトムホールド回路)を用いることで、無駄な電力消費を抑えるとともに、ノイズの発生を抑えて発振特性の悪化を防止することが可能な発振装置技術を提供。

【解決手段】基準電圧を発生する定電圧発生回路4と、駆動電圧または駆動電流によって発振する発振回路1と、発振回路1の出力である発振信号のピークレベルを検出して出力するピークホールド回路2と、定電圧発生回路4で発生された基準電圧VREFとピークホールド回路2で出力されたピークレベルPHに応じて駆動電圧または駆動電流を増減させて発振回路1の電源端子VRに入力するレギュレータ3からなる。ピークホールド回路2は定電流で動作し過渡的な電力を消費しない構成となっている。なお、ピークホールド回路2の代わりにボトムホールド回路を用いても良い。

(もっと読む)

定電圧回路及びそれを用いた水晶発振回路

【課題】定電圧の出力電圧を可変する機能を確実に発揮できる定電圧回路及びそれを用いた水晶発振回路を提供する。

【解決手段】定電圧回路24が定電圧の出力電圧VOUTを可変して高くする場合、基準電圧VREFが高く制御されることにより、PMOSトランジスタ16のゲート電圧及びドレイン電圧が高くなる。さらに、基準電圧VREFが高く制御され、NMOSトランジスタ18及びPMOSトランジスタ16のドレイン電流が多くなることにより、PMOSトランジスタ16のソース・ドレイン間電圧が高くなる。よって、PMOSトランジスタ16のソース電圧である定電圧の出力電圧VOUTが確実に高くなる。

(もっと読む)

電圧制御発振器

【課題】 発振周波数の可変量を大きくできる電圧制御発振器を提供する。

【解決手段】 水晶振動子と制御電圧供給端子13とのライン上に、抵抗R1とコンデンサC1が直列接続され、抵抗R1とコンデンサC1との間に可変容量ダイオードVD1のカソードを接続してアノードを接地し、コンデンサC1と水晶振動子に接続するポートとの間に、直列接続の可変容量ダイオードVD2及びコンデンサC3と、伸長コイルL1と、Qダンプ抵抗R6とを並列接続した並列接続回路を設け、並列接続回路の入力側が抵抗R4を介して接地し、抵抗R1とコンデンサC1との間の点と、可変容量ダイオードVD2とコンデンサC3との間の点を、抵抗R5を介して接続した電圧制御発振器である。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

分周回路及び半導体装置

【課題】回路動作の安定性の向上と、消費電力の低減とを両立できるようにした分周回路及び半導体装置を提供する。

【解決手段】発振回路に近い前段の側にあって高い周波数で動作するFF回路10と、発振回路から遠い後段の側にあって低い周波数で動作するFF回路10と、を備え、前段と後段の各FF回路10は、分周回路の動作時に通常、オン、オフを繰り返すFB−SOI−MOSFET11〜14、21、25をそれぞれ有し、前段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth1│とし、後段の各FF回路10が有するMOSFET11〜14、21、25の閾値電圧の絶対値を│Vth2│としたとき、│Vth1│<│Vth2│に設定されている。

(もっと読む)

圧電発振器

【課題】位相雑音特性におけるフロアノイズを改善する。

【解決手段】圧電振動子10と、圧電振動子10を発振させ発振信号OSCを出力する発振回路100と、発振信号OSCがベース端子に入力されエミッタ接地されたPNPトランジスターQ2と、PNPトランジスターQ2のコレクタ端子にベース端子が接続されエミッタ接地されたNPNトランジスターQ3と、NPNトランジスターQ3のコレクタ端子と接続されたバッファ回路200と、を含む圧電発振器1。

(もっと読む)

発振回路

【課題】発振バッファに過電圧が印加されるのを防止することができる発振回路を提供する。

【解決手段】発振回路10は、PTAT電流源12と、共振回路46と並列接続された発振バッファ14と、帰還抵抗Rfと、スイッチ素子54と、発振バッファ14と同一構成のレプリカバッファ52と、発振バッファ14の入力電圧を検知し、検知した入力電圧が発振時のバイアス電位よりも所定電位以上上昇した場合、及び、検知した入力電圧が発振時のバイアス電位よりも所定電位以下に下降した場合に、PTAT電流源12と発振バッファ14との接続点のノードVCCOSCの電位が発振バッファ14のPMOSトランジスタ42の耐圧を越えないように、PTAT電流源12からの電流をレプリカバッファ52回路にバイパスさせるための制御信号をスイッチ素子54手段に出力するレベル検知回路50と、を備える。

(もっと読む)

水晶発振回路

【課題】発振起動性に優れ、定常発振時には低消費電力で発振を継続することができる水晶発振回路を提供する。

【解決手段】水晶発振回路は、入力側及び出力側負荷容量5、6、と水晶振動子3とを有する共振回路と、共振回路を定常的に励振する増幅回路であるCMOSインバータを構成するP型及びN型MOSFET1、2と、増幅回路の出力振幅に応じた電圧で発振電流を制御する電流制限素子である電流制限用P型及びN型MOSFET21、22と、電流制限素子を制御する発振電流制御手段である第1及び第2の容量51、52と、第1及び第2のダイオード61、62により構成され、発振電流制御手段は、増幅回路から交流信号が出力されない非発振状態では、電流制限素子を導通状態とし、増幅回路から交流信号が出力される発振状態では、増幅回路の出力振幅に応じた交流電圧により、導通状態よりも抵抗値が大きな状態となるように、電流制限素子を制御する。

(もっと読む)

温度補償型電圧制御発振回路

【課題】 水晶振動子の周囲温度に対応してトランジスタにおける容量をダイナミックに可変とし、高感度で発振周波数を一定に保つよう制御できる温度補償型電圧制御発振回路を提供する。

【解決手段】 水晶振動子X1 の周囲温度の変化に対応して発振周波数を一定に保持する容量に相当する電圧値に変換する容量変換制御回路11と、当該容量変換制御回路11によって設定される容量に従ってNPN型トランジスタQのコレクタCとベースBとの間の容量を可変とする容量変更手段12とを有する容量変換回路1を水晶振動子X1 とNPN型トランジスタQのベースBとの間に設けた温度補償型電圧制御発振回路である。

(もっと読む)

圧電発振器

【課題】圧電発振器の低電源電圧化に対応可能とすると共に、安定した性能を有する圧電

発振器を提供することを目的とする。

【解決手段】圧電発振器1は、コルピッツ型の発振回路2と、発振回路2が出力する発振

信号より基本波周波数を濾波し、即ち通過させるフィルタ回路3と、発振回路2とフィル

タ回路3との間に接続されたダイオードD1とにより構成し、圧電発振器1には、ノイズ

を除去するためのバイパスコンデンサC5を介して電源電圧(Vcc)を印加している。

本発明においては、発振回路2とフィルタ回路3とをダイオードD1を経由して接続した

。

(もっと読む)

発振回路および発振器

【課題】低消費電流化した発振回路および発振器を提供すると共に、外部との通信による誤動作の防止および高精度な発振回路および発振器を提供する。

【解決手段】発振回路10は、外部との通信を行うインターフェース回路12と、発振段20とを備えたものであって、インターフェース回路12に接続し、インターフェース回路12に入力または出力する通信信号の外部通信端子40と、インターフェース回路12の制御信号入力端子に接続し、インターフェース回路12をアクティブ状態またはスリープ状態に切り替える制御信号を入力する外部制御端子38とを備えた構成である。そしてインターフェース回路12は、外部制御端子38および制御信号入力端子を介してインターフェース回路12に入力した制御信号にしたがってアクティブまたはスリープのいずれかの状態になる。

(もっと読む)

温度センサ回路と温度補償型圧電発振器

【課題】低電圧化に適した、ノイズの少ない温度センサ回路を得る。

【解決手段】トランジスタTr1と、第1の抵抗である抵抗R1と第2の抵抗である抵抗R2とを直列に接続した直列回路により構成される。直列回路を構成する抵抗R1の一端はトランジスタTr1のコレクタに、直列回路を構成する抵抗R2の一端が基準電源にそれぞれ接続されている。そして、トランジスタTr1のベースが抵抗R1と抵抗R2との接続点に接続され、トランジスタTr1のエミッタが接地されている。

(もっと読む)

発振子及び該発振子を有する発振器

【課題】低電圧で駆動することができること。

【解決手段】X方向に延びるように形成され、X方向に直交するY方向に振動する振動片36と、振動片36の両端を支持する振動子アイランド34a,34bとを有する振動子32と、振動片36に対して所定距離を空けた状態で振動片36を間に挟むように配置され、電圧が印加された時に静電引力を発生させて振動片36を振動させる電極部33a,33bと、を備え、振動片36は、振動部39と、振動部39を振動子アイランド34a,34bに連結する基端部35a,35bと、で一体的に形成され、振動部39の幅が、基端部35a,35bの幅に比べ広く形成されている発振子30を提供する。

(もっと読む)

発振子及び該発振子を有する発振器

【課題】振動片のスティッキングを防止して歩留まりを向上させること。

【解決手段】基端部35から先端部39に向かってX方向に延びるように形成され、該X方向に直交するY方向に振動する振動片36と、基端部35を介して振動片36を片持ち状に支持する振動子アイランド34と、を有する振動子32と、振動片36に対してギャップdを空けた状態で他方向に沿って振動片36を間に挟むように配置され、電圧が印加された時に静電引力を発生させて振動片36を振動させる電極部33a,33bとを備え、電極部33a,33bにおける電極部アイランド40a,40bの側面48a,48bに、電極部アイランド40a,40bの長手方向に沿って複数の突起部49が形成されている発振子30を提供する。

(もっと読む)

水晶発振回路

【課題】 ディレイ回路を設けたり、バイアス決定回路のバイアス点と波形整形回路のスレッショルドとを異ならせたりすることなく、消費電流を低減し、自励発振や異常発振を防ぐことができる水晶発振回路を提供する。

【解決手段】 水晶振動子21および水晶振動子21の出力を増幅し、電源電圧より低い定電圧源LDO1により駆動される発振増幅器22を有する水晶発振部2の出力に、電源電圧レベルにレベルシフトする結合コンデンサ3が接続され、その結合コンデンサ3の出力に、ソースがVddに、ゲートがVssに接続されたPチャネルMOSトランジスタ41およびソースがVssに、ゲートがVddに接続されたNチャネルMOSトランジスタ42のそれぞれのドレインが接続されたバイアス決定回路4が接続され、そのバイアス決定回路4の出力に振幅検知回路5、および波形整形回路6が接続されている。

(もっと読む)

1 - 20 / 41

[ Back to top ]